Openroad ist die führende Open-Source-Anwendung für das digitale Halbleiterdesign. Der Openroad Flow liefert einen autonomen, No-Human-in-Loop-Fluss (NHIL), der 24 Stunden Turnaround von RTL-GdII für eine schnelle Exploration und die Implementierung des physischen Entwurfs von RTL-GDII.

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

Testen Sie die Installation: Schreiben Sie 'Iverilog' in Terminal und drücken Sie eine erfolgreiche Installation ein.

sudo apt install gtkwave

Wir werden sehen, wie die Signale mit einem Beispiel in GTKWAVE aufgetragen werden.

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

Wenn 'Tcl Interp' kein Mitglied namens 'Ergebnis' hat, ist ein Fehler aufgetreten:

cd covered

cd src

gedit report.c

In der Datei report.c sehen Sie eine Liste von #include -Befehlen. Finden Sie #include <tcl.h> und fügen Sie den folgenden Befehl '#define use_interp_result 1' vor #include <tcl.h> hinzu.

Ihr Bericht sieht so aus:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

Speichern Sie die Datei report.c. Führen Sie den Befehl erneut aus und fahren Sie mit dem Installationsprozess wie oben gezeigt fort.

Quelle Verilog -Code:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

TestBench Verilog -Code:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

• Starten Sie die Linux -Verteilung und erstellen Sie ein Verzeichnis $ mkdir icarus_codes

Wo Icarus -Codes der Name des Verzeichnisses ist.

• Wechseln Sie das Verzeichnis in Icarus -Codes. Für die Simulation benötigen Sie einen Verilog -Code für die implementierte Funktionalität und eine Testbank im .V -Format. Fügen Sie diejenigen in das Arbeitsverzeichnis auf. Nehmen wir an, mein Verilog -Code heißt Mycounter.v und der TestBench ist Testbench.v . Simulieren:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

Eine Dump -Datei, die ich in der Testbank als count.vcd bezeichnet habe, wird erstellt, und Sie können auch die Ausgabe am Terminal sehen. Sie können die Ausgabe auch in der GTKWAVE anzeigen

$ gtkwave count.vcd Dieser Befehl startet die GTKWAVE Analyzer -Anwendung. Erweitern Sie im linken Feld die Testbench und klicken Sie auf den Unterordner. Es wird erweitert, um die Eingangsuhr anzuzeigen, die Wellenform zurückzusetzen und auszugeben [3: 0]. Ziehen Sie diese in das Signalpanel und analysieren Sie die Ergebnisse.

Um den Prozentsatz des von der Testbank getesteten RTL -Designs abzuschätzen, wird das Abdeckung von Verilog -Code -Deckungs -Analysator -Tool verwendet. • Generieren Sie den Code -Abdeckungsbericht im selben Verzeichnis, dh ICARUS Codes, indem Sie den folgenden Befehl ausführen

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

• Um den Berichterstattungsbericht anzuzeigen, führen Sie aus

$ covered report -d v Mycounter.cdd

Der Deckungsbericht wird im Terminal angezeigt.

Wenn Sie einen Fehler bezeichnen, der als "Segmentierungsfehler" bezeichnet wird, versuchen Sie Folgendes:

sudo apt-get install gedit

Öffnen Sie die generierte VCD -Datei in GEDIT, finden Sie die Zeile "$ comment zeigen die Parameterwerte. $ End" und löschen Sie sie.

Speichern Sie die VCD -Datei und führen Sie den Fluss aus, sie sollte jetzt funktionieren.

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

Versuchen Sie nach der Installation, Yosys zu rufen wie: ./yosys das Tool startet und die Eingabeaufforderung ändert sich an yosys>

Hier habe ich die Bibliotheksdatei Nangate45_typ.lib gegeben

Um eine Verilog -Quelldatei mit YOSYS zu synthetisieren, muss diese Bibliotheksdatei im TCL -Automatisierungsskript enthalten sein.

Erstellen Sie eine Datei namens yosys_commands.tcl und geben Sie diese Zeilen in die Datei und speichern Sie.

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

Dieses TCL -Skript sollte ausgeführt werden, nachdem Yosys aufgerufen wurde. Dadurch automatisiert der Synthese -Prozess und schreibt die synthetisierte Netzliste aus der Quellverilog -Datei

Starten Sie das YOSYS -Tool $ yosys Ich verwende eine yosys_commands.tcl -Datei. yosys> script yosys_commands.tcl

Führen Sie in ähnlicher Weise die angegebenen Skripte not_opt.tcl und opt.tcl aus, um das nicht optimierte Blockdiagramm bzw. optimierte Blockdiagramme im Fenster GraphViz (XDOT) zu sehen

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

Wenn Fehler Cmake error at CMakelists.txt auftritt

sudo apt-get install libeigen3-dev

Gehen Sie erneut zum Build -Verzeichnis in OpenSta und konfigurieren Sie den Build, indem Sie den folgenden Befehl ausführen:

cmake ..

Wenn Sie erneut einen CMAKE -Fehler haben, gehen Sie erneut zum Home -Verzeichnis und installieren Sie CUDD.

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

Jetzt ist Cudd erfolgreich installiert. Ziehen Sie nun zum OpenSta -Verzeichnis auf

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

Rufen Sie nun Opensta vom Terminal durch einfach "STA" ein und drücken Sie die Eingabetaste.

sta [~/working_directory]

or,

it will be shown like

%

Nach erfolgreicher Installation von OpenSta leiten Sie die time.tcl aus power.tcl

Für die Zeitanalyse mit OpenSta

% source time.tcl

Für die Leistungsanalyse mit OpenSta

% source power.tcl

Download Openroad Repository

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

Abhängigkeiten installieren

sudo ./etc/DependencyInstaller.sh

Openroad bauen

mkdir build

cd build

cmake ..

sudo make

sudo make install

Wenn nach dem Ausführen von "CMake" Fehler wie: CMake Error: Could not find CMAKE_ROOT !!! Führen Sie dann export PATH=/usr/local/bin/cmake:$PATH aus und führen Sie echo $CMAKE_ROOT aus, es sollte den Pfad widerspiegeln, dann "cmake" und agin run "make & make install" erneut ausführen.

Wenn noch Fehler auftreten:

sudo apt install swig

sudo apt update

Rufen Sie das Openroad -Tool aus dem Terminal auf und es sollte in openroad>

Skript zur Ausführung von Aktivitäten:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

Schreiben Sie design_nangate45.tcl -Datei

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

Jetzt sind alle Dateien fertig, einige bestimmte Dateien müssen in den Ordner "Openroad/Test" kopieren. Dies lautet:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

Gehen Sie nach dem Kopieren dieser Dateien in OpenROAD/test in das gleiche Verzeichnis und rufen Sie Openroad auf, um Dateien von einem Verzeichnis in ein anderes Verzeichnis zu kopieren.

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

Dann

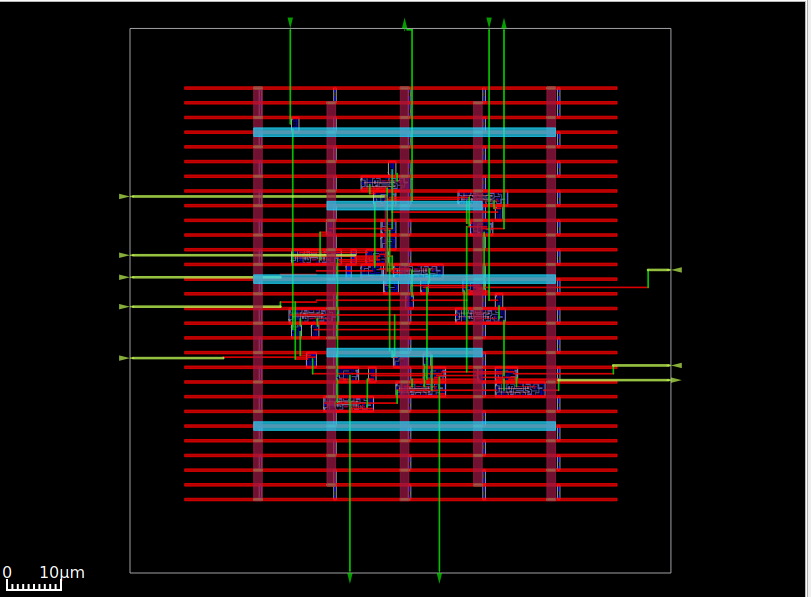

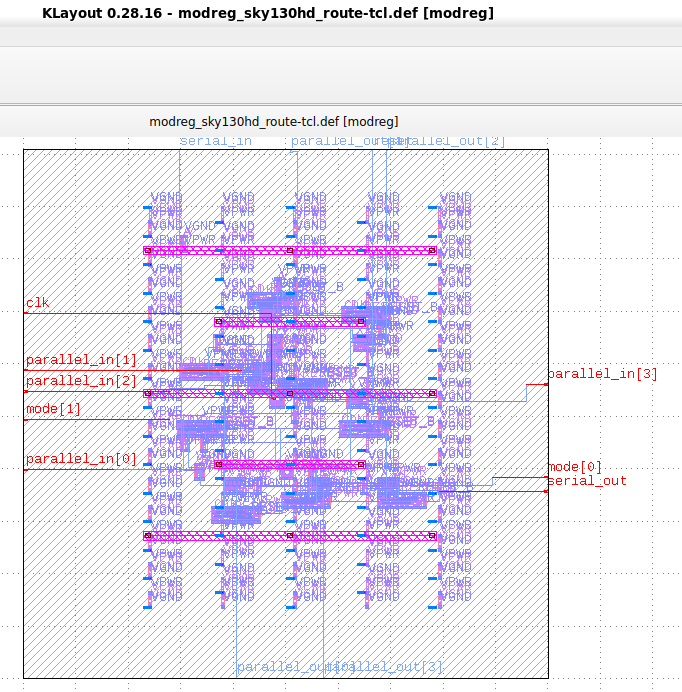

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

Wenn Sie diesen Befehl ausführen, wird ein ASIC -Layout erzeugt, das jetzt in der Openroad -GUI sichtbar ist, um es als GDSII zu speichern. Es braucht Klyout.

sudo apt install klayout

Öffnen Sie den Klayout mit diesem Befehl

klayout &

Klicken Sie nun auf die Schaltfläche "Datei" und wählen Sie die Leseroption. Klicken Sie dann auf "LEF/DEF" -Rist für "nangate45.lef". Die Datei muss das Kontrollkästchen (falls möglich) oder deaktivieren (falls dies aktiviert) oder gleichzeitig der gleiche Speicherort von "Nangate45.lef" ist.

/OpenROAD/test/Nangate45/Nangate45.lef

Klicken Sie dann auf OK. Klicken Sie nach diesem Klick erneut in der Datei und wählen Sie Öffnen. Jetzt wird ein Dialogfeld geöffnet.

/OpenROAD/test/result

Dort wird die Datei design.def gefunden, klicken Sie auf die DEF -Datei und klicken Sie auf OK. Jetzt öffnet es im GDSII -Modus und kann als GDSII gespeichert werden.

Jetzt ist das Design bereit, zur Herstellung an Foundry geschickt zu werden.

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.