OpenRoad-это ведущее основополагающее приложение для полупроводникового цифрового дизайна. Поток OpenRoad обеспечивает автономный поток без человечества (NHIL), 24-часовой поворот от RTL-GDSII для быстрого разведки дизайна и реализации физического дизайна.

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

Проверьте установку: напишите «iverilog» в терминале и нажмите «Введите успешную установку».

sudo apt install gtkwave

Посмотрим, как сигналы нанесены на график с использованием примера в GTKWave.

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

Если TCL Interp ′ не имеет члена с названием «Результат». Произошла ошибка:

cd covered

cd src

gedit report.c

В файле отчета.c вы увидите список команд #include. Найдите #include <tcl.h> и добавьте следующую команду '#define use_interp_result 1' до #include <tcl.h>.

Ваш отчет будет выглядеть так:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

Сохраните файл отчета.c. Запустите команду Make снова и перейдите с процессом установки, как показано выше.

Источник Verilog Code:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

Testbench Verilog Code:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

• Запустите дистрибуцию Linux и сделайте каталог $ mkdir icarus_codes

где коды Icarus - это название каталога.

• Изменить каталог на коды Icarus. Для симуляции вам требуется код Verilog для реализации функциональности и испытательную скамью в формате .v. Включите тех, кто в рабочем каталоге. Допустим, мой код Verilog назван Mycounter.v , а Testbench - Testbench.v . Для имитации:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

Создан файл дампы, который я назвал как count.vcd на испытательной скамейке, и вы также можете увидеть выход на терминале. Вы также можете просмотреть выход в GTKWAVE

$ gtkwave count.vcd Эта команда запускает приложение Gtkwave Analyzer. На левой панели разверните Testbench и нажмите на подпалку. Он будет расширяться, чтобы показать входные часы, сброс и выходной сигнал [3: 0]. Перетащите их на панель Signals и проанализируйте результаты.

Чтобы оценить процент проектирования RTL, протестированного тестовой скамейкой, используется инструмент Analyzer Code Code Verilog. • Сгенерировать отчет о покрытии кода в том же каталоге, т.е., коды ICARUS, выполнив следующую команду

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

• Чтобы просмотреть отчет о покрытии, выполнить

$ covered report -d v Mycounter.cdd

Отчет о покрытии отображается в терминале.

Если столкнулась с какой -либо ошибкой, называемой «ошибкой сегментации», попробуйте это:

sudo apt-get install gedit

Откройте сгенерированный VCD -файл в GEDIT, найдите строку "$ Comment Показать значения параметров. $ END" и удалить его.

Сохраните файл VCD, затем Agin запустите поток, он должен работать сейчас.

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

После установки Попробуйте вызов Yosys, например: ./yosys Запуск инструмента, и командная строка изменяется на yosys>

Здесь я дал файл библиотеки с именем Nangate45_typ.lib

Для синтеза любого исходного файла Verilog с помощью Yosys этот файл библиотеки должен быть включен в скрипт автоматизации TCL.

Сделайте файл с именем yosys_commands.tcl и поместите эти строки в файл и сохраните.

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

Этот скрипт TCL должен быть запущен после того, как Yosys вызывает. Это автоматизирует процесс синтеза и написать синтезированный список сети из файла источника Verilog

Запустите инструмент yosys $ yosys Я использую файл yosys_commands.tcl. yosys> script yosys_commands.tcl

Аналогичным образом запустите заданные скрипты not_opt.tcl и opt.tcl для просмотра неоптимизированной блок-схемы и оптимизированных блок-схемы соответственно в окне Graphviz (xdot)

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

Если ошибка возникает как Cmake error at CMakelists.txt затем перейдите в Home Directory, используя команду «CD» и установить

sudo apt-get install libeigen3-dev

Еще раз перейдите в каталог сборки в OpenSTA и настройте сборку, выполнив следующую команду:

cmake ..

Если снова любая ошибка Cmake, снова перейдите в Home Directory и установите CUDD.

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

Теперь CUDD установлен успешно. Теперь перейдите в каталог OpenSta

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

Теперь вызовите OpenSta из терминала, просто введите «sta» и нажмите Enter It, изменил подсказку на

sta [~/working_directory]

or,

it will be shown like

%

После успешной установки OpenSTA запустите time.tcl для анализа времени входов и выходов, после этого запуска power.tcl для анализа рассеивания мощности с помощью разработанной схемы.

Для анализа времени с использованием opensta

% source time.tcl

Для анализа мощности с использованием OpenSTA

% source power.tcl

Скачать Repository OpenRoad

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

Установить зависимости

sudo ./etc/DependencyInstaller.sh

Строить открытую дорогу

mkdir build

cd build

cmake ..

sudo make

sudo make install

Если после запуска "cmake" он показывает ошибку, например: CMake Error: Could not find CMAKE_ROOT !!! Затем запустите export PATH=/usr/local/bin/cmake:$PATH и echo $CMAKE_ROOT , он должен отражать путь, а затем повторить «cmake» и agin run «Make & Stake Install»

Если все еще возникают ошибки:

sudo apt install swig

sudo apt update

Вызовать инструмент OpenRoad с терминала, и его следует изменить на openroad>

Скрипт, используемый для выполнения деятельности:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

write design_nangate45.tcl файл

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

Теперь все файлы готовы, некоторые конкретные файлы должны скопировать в папку «OpenRoad/Test», это:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

После копирования этих файлов в папку OpenROAD/test , перейдите в тот же каталог и вызовите OpenRoad для копирования файлов из одного каталога в другой каталог:

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

затем

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

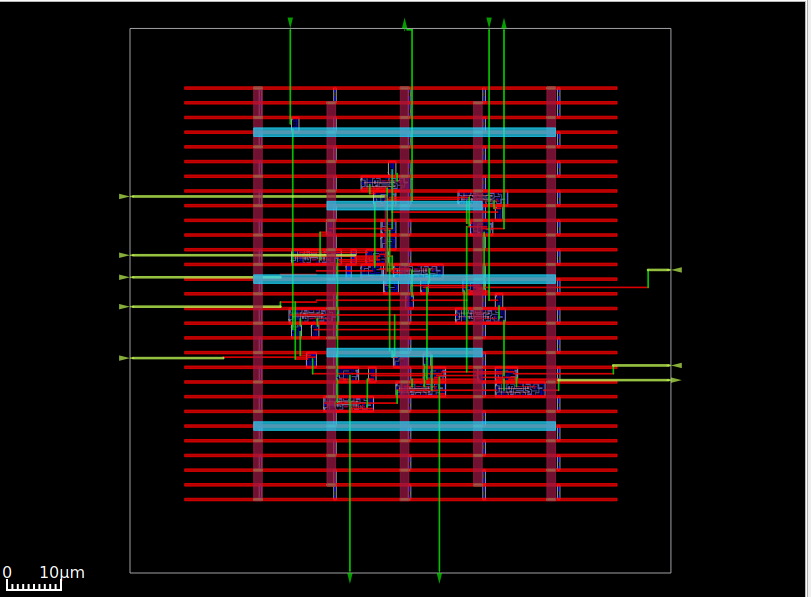

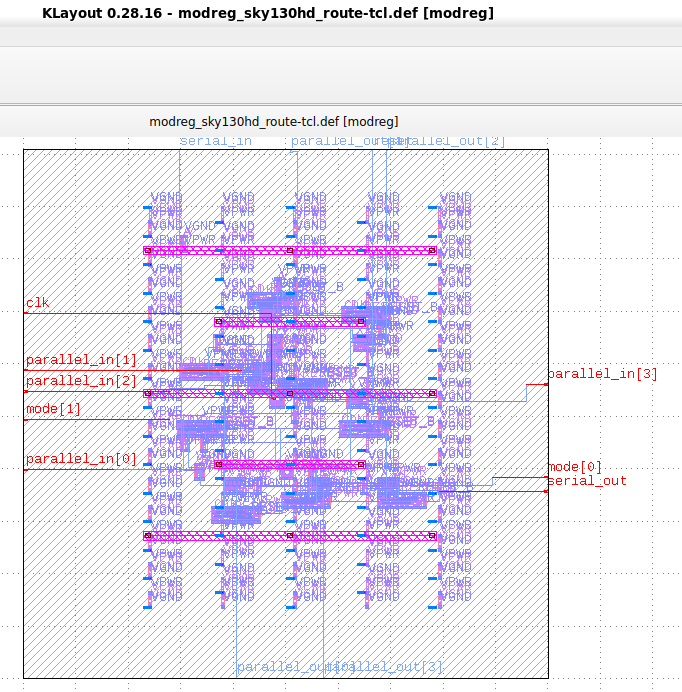

Запустив эту команду, он будет генерировать макет ASIC, которая будет видна в GUI OpenRoad, чтобы сохранить его в качестве GDSII, он нуждается в Klayout.

sudo apt install klayout

Откройте Klayout, используя эту команду

klayout &

Теперь нажмите на кнопку «Файл» и выберите опцию Reader, а затем нажмите на вкладку «Lef/Def», необходимо положить файл «nangate45.lef», и снять флажок (если проверяется) или оставаться в том же месте «nangate45.lef».

/OpenROAD/test/Nangate45/Nangate45.lef

Затем нажмите ОК. После этого нажмите еще раз по файлу и выберите «Открыть», теперь откроется диалог, перейдите к

/OpenROAD/test/result

Там будет расположен файл design.def , нажмите на файл DEF и нажмите OK. Теперь он откроется в режиме GDSII и может быть сохранен как GDSII.

Теперь дизайн готов отправиться в Foundry для изготовления.

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.