Openroad是半導體數字設計的主要開源,基礎應用。 OpenRoad流提供了自動駕駛,無人間的(NHIL)流量,從RTL-GDSII進行了24小時的周轉,以快速設計探索和物理設計實現。

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

測試安裝:在終端中寫入“ iverilog”,然後按Enter成功安裝應顯示以下輸出:iverilog:無源文件,建議-c,-y等。

sudo apt install gtkwave

我們將使用GTKWave中的示例來了解如何繪製信號。

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

如果“ tcl Interp'沒有成員命名”結果'錯誤:

cd covered

cd src

gedit report.c

在Report.c文件中,您將看到#include命令的列表。在#include <tcl.h>之前找到#include <tcl.h>,然後添加以下命令'#define use_interp_result 1'。

您的報告看起來像這樣:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

保存report.c文件。再次運行Make Command,然後繼續進行安裝過程,如上所示。

來源Verilog代碼:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

TestBench Verilog代碼:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

•啟動Linux發行版並製作目錄$ mkdir icarus_codes

伊卡洛斯代碼是目錄的名稱。

•將目錄更改為Icarus代碼。為了進行仿真,您需要一個用於實現功能的Verilog代碼和.v格式的測試工作台。在工作目錄中包括那些。假設我的Verilog代碼名為Mycounter.v ,testbench是Testbench.v 。模擬:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

創建了一個我稱為Count.VCD的轉儲文件,也是創建的,您也可以在終端上看到輸出。您還可以查看GTKWAVE中的輸出

$ gtkwave count.vcd此命令啟動gtkwave Analyzer應用程序。在左圖中,展開測試台,然後單擊子文件夾。它將擴展以顯示輸入時鐘,重置和輸出波形[3:0]。將它們拖到信號面板上並分析結果。

為了估計測試工作台測試的RTL設計的百分比,使用了覆蓋的Verilog代碼覆蓋分析儀工具。 •通過執行以下命令在同一目錄中生成代碼覆蓋報告,ICARUS代碼

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

•要查看覆蓋報告,請執行

$ covered report -d v Mycounter.cdd

覆蓋範圍報告顯示在終端中。

如果遇到任何稱為“分段故障”的錯誤,請嘗試以下操作:

sudo apt-get install gedit

在GEDIT中打開生成的VCD文件,找到“ $註釋顯示參數值。$ end”並刪除它。

保存VCD文件,然後Agin運行流,現在應該工作。

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

安裝後嘗試調用yosys,例如: ./yosys the工具啟動,命令提示符更改為yosys>

在這裡,我給了名為Nangate45_typ.lib的庫文件

要使用yosys合成任何Verilog源文件,必須將此庫文件包含在TCL自動化腳本中。

製作一個名為yosys_commands.tcl的文件,然後將此行放入文件中並保存。

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

調用Yosys之後,應運行此TCL腳本。這將自動化合成過程並從源Verilog文件中編寫合成的NetList

啟動我正在使用yosys_commands.tcl文件的yosys工具$ yosys 。 yosys> script yosys_commands.tcl

類似地,運行給定的not_opt.tcl和opt.tcl腳本,用於查看非優化的框圖和優化的框圖(xdot)窗口中的優化框圖

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

如果錯誤像Cmake error at CMakelists.txt一樣,則使用“ CD”命令移至主目錄並安裝

sudo apt-get install libeigen3-dev

再次轉到OpenSta中的構建目錄,並通過執行以下命令來配置構建:

cmake ..

如果再次出現任何CMAKE錯誤,則再次移至Home Directory並安裝CUDD。

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

現在,CUDD已成功安裝。現在移至OpenSta目錄

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

現在,只需鍵入“ sta”,然後按Enter將其更改為

sta [~/working_directory]

or,

it will be shown like

%

在成功安裝OpenSta之後,將time.tcl運行以分析輸入和輸出的時間,然後運行power.tcl以通過設計的電路分析功率耗散。

用於使用OpenSTA的時間分析

% source time.tcl

用於使用OpenSTA的功率分析

% source power.tcl

下載OpenRoad存儲庫

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

安裝依賴項

sudo ./etc/DependencyInstaller.sh

建立公開

mkdir build

cd build

cmake ..

sudo make

sudo make install

如果運行“ cmake”後,則顯示錯誤: CMake Error: Could not find CMAKE_ROOT !!!然後運行export PATH=/usr/local/bin/cmake:$PATH並運行echo $CMAKE_ROOT ,它應該反映路徑,然後重新運行“ cmake”和agin run“ make&make install”

如果仍然發生任何錯誤:

sudo apt install swig

sudo apt update

從終端調用OpenRoad工具,應將其更改為openroad>

用於執行活動的腳本:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

寫design_nangate45.tcl文件

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

現在所有文件都準備就緒,一些特定文件需要復製到“ OpenRoad/Test”文件夾中,這是:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

將此文件複製到OpenROAD/test文件夾後,轉到同一目錄並調用OpenRoad以將文件從一個目錄複製到另一個目錄是:

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

然後

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

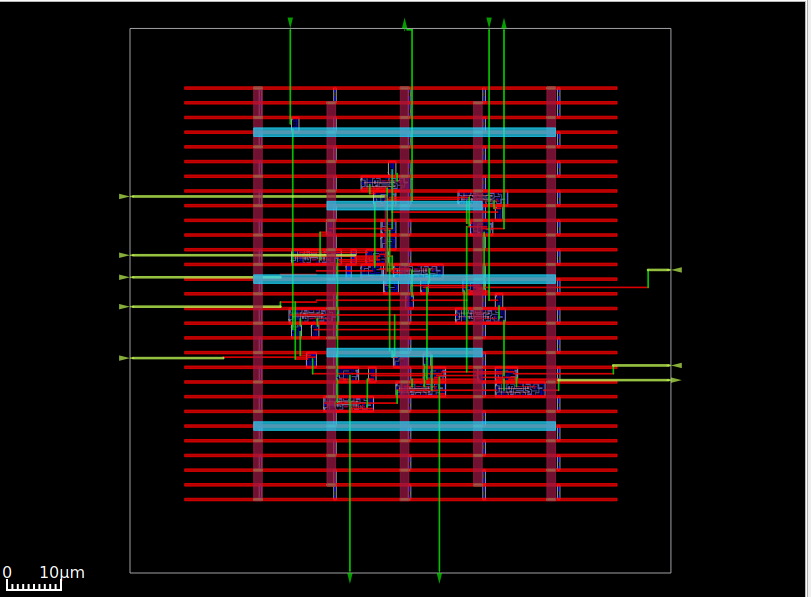

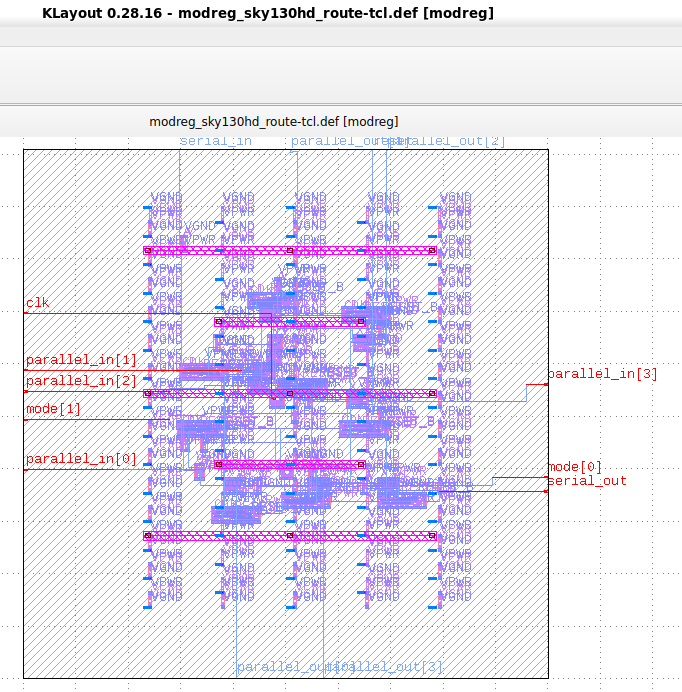

運行此命令將生成ASIC佈局,該佈局將在OpenRoad GUI中可見,以將其保存為GDSII,它需要Klayout。

sudo apt install klayout

使用此命令打開klayout

klayout &

現在單擊“文件”按鈕,然後選擇讀取器選項,然後單擊“ lef/def”選項卡,“ nangate45.lef”文件需要放置並取消選中復選框(如果已檢查)或保持“ nangate45.lef”的相同位置

/OpenROAD/test/Nangate45/Nangate45.lef

然後單擊確定。在此之後,請再次單擊文件並選擇“打開”,現在將打開對話框,導航到

/OpenROAD/test/result

design.def文件將找到,單擊DEF文件,然後單擊“確定”。現在它將以GDSII模式打開,可以保存為GDSII。

現在,設計可以發送到鑄造廠進行製造。

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.