Openroad เป็นแอพพลิเคชั่นพื้นฐานโอเพ่นซอร์สชั้นนำสำหรับการออกแบบดิจิตอลเซมิคอนดักเตอร์ Openroad Flow มอบการไหลแบบอิสระแบบไม่เป็นอิสระและไม่มีมนุษย์ (NHIL) การพลิกกลับ 24 ชั่วโมงจาก RTL-GDSII สำหรับการสำรวจการออกแบบอย่างรวดเร็วและการใช้งานการออกแบบทางกายภาพ

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

ทดสอบการติดตั้ง: เขียน 'iverilog' ในเทอร์มินัลและกด Enter Enter การติดตั้งที่ประสบความสำเร็จควรแสดงเอาต์พุตนี้: iverilog: ไม่มีไฟล์ต้นฉบับและจะแนะนำ -c, -y ฯลฯ

sudo apt install gtkwave

เราจะเห็นว่าสัญญาณถูกพล็อตโดยใช้ตัวอย่างใน GTKWave อย่างไร

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

ถ้า 'TCL Interp′ ไม่มีสมาชิกชื่อ 'เกิดข้อผิดพลาดเกิดขึ้น:

cd covered

cd src

gedit report.c

ในไฟล์ report.c คุณจะเห็นรายการคำสั่ง #include ค้นหา #include <tcl.h> และเพิ่มคำสั่งต่อไปนี้ '#define use_interp_result 1' ก่อน #include <tcl.h>

รายงานของคุณจะเป็นแบบนี้:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

บันทึกไฟล์รายงาน เรียกใช้คำสั่ง Make อีกครั้งและดำเนินการกับกระบวนการติดตั้งตามที่แสดงด้านบน

รหัสแหล่งที่มาของ Verilog:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

TestBench Verilog Code:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

•เปิดการกระจาย Linux และสร้างไดเรกทอรี $ mkdir icarus_codes

โดยที่รหัสอิคารัสเป็นชื่อของไดเรกทอรี

•เปลี่ยนไดเรกทอรีเป็นรหัสอิคารัส สำหรับการจำลองคุณต้องใช้รหัส Verilog สำหรับฟังก์ชั่นที่ใช้งานและม้านั่งทดสอบในรูปแบบ. v รวมผู้ที่อยู่ในไดเรกทอรีการทำงาน สมมติว่ารหัส verilog ของฉันมีชื่อว่า Mycounter.v และ testbench คือ Testbench.v เพื่อจำลอง:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

ไฟล์ถ่ายโอนข้อมูลซึ่งฉันได้ตั้งชื่อเป็น count.vcd ในบัลลังก์ทดสอบถูกสร้างขึ้นและคุณสามารถเห็นเอาต์พุตบนเทอร์มินัลได้เช่นกัน นอกจากนี้คุณยังสามารถดูผลลัพธ์ใน gtkwave

$ gtkwave count.vcd คำสั่งนี้เปิดตัวแอปพลิเคชัน GTKWave Analyzer ในแผงด้านซ้ายขยาย TestBench และคลิกที่โฟลเดอร์ย่อย มันจะขยายเพื่อแสดงนาฬิกาอินพุตรีเซ็ตและเอาต์พุตรูปคลื่นออก [3: 0] ลากสิ่งเหล่านั้นไปยังแผงสัญญาณและวิเคราะห์ผลลัพธ์

ในการประเมินเปอร์เซ็นต์ของการออกแบบ RTL ที่ทดสอบโดยม้านั่งทดสอบใช้เครื่องมือวิเคราะห์การครอบคลุมรหัส Verilog ที่ครอบคลุม •สร้างรายงานการครอบคลุมรหัสในไดเรกทอรีเดียวกันเช่นรหัส ICARUS โดยดำเนินการคำสั่งต่อไปนี้

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

•หากต้องการดูรายงานความครอบคลุมให้ดำเนินการ

$ covered report -d v Mycounter.cdd

รายงานความครอบคลุมจะแสดงในเทอร์มินัล

หากพบข้อผิดพลาดใด ๆ ที่เรียกว่า "ความผิดพลาดในการแบ่งส่วน" ลองทำเช่นนี้:

sudo apt-get install gedit

เปิดไฟล์ VCD ที่สร้างขึ้นใน GEDIT ค้นหาบรรทัด "$ ความคิดเห็นแสดงค่าพารามิเตอร์ $ end" และลบ

บันทึกไฟล์ VCD จากนั้น agin เรียกใช้โฟลว์มันควรจะทำงานได้แล้ว

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

หลังจากติดตั้งลองเรียกใช้ yosys เช่น: ./yosys เครื่องมือเปิดตัวและคำสั่งการเปลี่ยนคำสั่งจะเปลี่ยนเป็น yosys>

ที่นี่ฉันได้รับไฟล์ไลบรารีชื่อ Nangate45_typ.lib

ในการสังเคราะห์ไฟล์แหล่งที่มาของ Verilog โดยใช้ไฟล์ Library นี้จะต้องรวมอยู่ในสคริปต์ TCL Automation

สร้างไฟล์ชื่อ yosys_commands.tcl และใส่บรรทัดนี้ลงในไฟล์และบันทึก

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

สคริปต์ TCL นี้ควรเรียกใช้หลังจากที่มีการเรียกใช้ yosys สิ่งนี้จะทำให้กระบวนการสังเคราะห์เป็นไปโดยอัตโนมัติและเขียน netlist สังเคราะห์จากไฟล์ verilog แหล่งที่มา

เปิดตัว Yosys Tool $ yosys ฉันใช้ไฟล์ yosys_commands.tcl yosys> script yosys_commands.tcl

เรียกใช้สคริปต์ not_opt.tcl และ opt.tcl ในทำนองเดียวกันสำหรับการดูแผนภาพบล็อกที่ไม่ได้รับการปรับแต่งและไดอะแกรมบล็อกที่ได้รับการปรับปรุงตามลำดับในหน้าต่าง GraphViz (XDOT)

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

หากข้อผิดพลาดเกิดขึ้นเช่น Cmake error at CMakelists.txt จากนั้นย้ายไปที่โฮมไดเรกทอรีโดยใช้คำสั่ง "cd" และติดตั้ง

sudo apt-get install libeigen3-dev

ย้ายไปที่ไดเรกทอรี Build อีกครั้งใน OpenSta และกำหนดค่าการสร้างโดยดำเนินการคำสั่งต่อไปนี้:

cmake ..

หากเกิดข้อผิดพลาด CMake อีกครั้งแล้วย้ายไปที่ Home Directory อีกครั้งและติดตั้ง cudd

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

ตอนนี้ Cudd ได้รับการติดตั้งเรียบร้อยแล้ว ตอนนี้ย้ายไปที่ไดเรกทอรี OpenSta

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

ตอนนี้เรียกใช้ OpenSta จากเทอร์มินัลเพียงแค่พิมพ์ "sta" แล้วกด Enter มันเปลี่ยนพรอมต์เป็น

sta [~/working_directory]

or,

it will be shown like

%

หลังจากการติดตั้ง OpenSta ที่ประสบความสำเร็จจะใช้ time.tcl เพื่อวิเคราะห์ระยะเวลาของอินพุตและเอาต์พุตหลังจากใช้ power.tcl RUN.TCL เพื่อวิเคราะห์การกระจายพลังงานโดยวงจรที่ออกแบบมา

สำหรับการวิเคราะห์เวลาโดยใช้ OpenSta

% source time.tcl

สำหรับการวิเคราะห์พลังงานโดยใช้ OpenSta

% source power.tcl

ดาวน์โหลด Openroad Repository

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

ติดตั้งการพึ่งพา

sudo ./etc/DependencyInstaller.sh

สร้าง Openroad

mkdir build

cd build

cmake ..

sudo make

sudo make install

หากหลังจากเรียกใช้ "cmake" มันจะแสดงข้อผิดพลาดเช่น: CMake Error: Could not find CMAKE_ROOT !!! จากนั้นเรียกใช้ export PATH=/usr/local/bin/cmake:$PATH และเรียกใช้ echo $CMAKE_ROOT มันควรสะท้อนเส้นทางจากนั้นรัน "cmake" และ agin run "make & make install"

หากยังมีข้อผิดพลาดเกิดขึ้น:

sudo apt install swig

sudo apt update

เรียกใช้เครื่องมือ Openroad จากเทอร์มินัลและควรเปลี่ยนเป็น openroad>

สคริปต์ที่ใช้ในการดำเนินกิจกรรม:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

เขียนไฟล์ design_nangate45.tcl

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

ตอนนี้ไฟล์ทั้งหมดพร้อมแล้วไฟล์เฉพาะบางไฟล์จำเป็นต้องคัดลอกไปยังโฟลเดอร์ "Openroad/Test Test" นี่คือ:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

หลังจากคัดลอกไฟล์นี้ลงในโฟลเดอร์ OpenROAD/test ให้ไปที่ไดเรกทอรีเดียวกันและเรียกใช้ Openroad เพื่อคัดลอกไฟล์จากไดเรกทอรีหนึ่งไปยังไดเรกทอรีอื่นคือ:

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

แล้ว

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

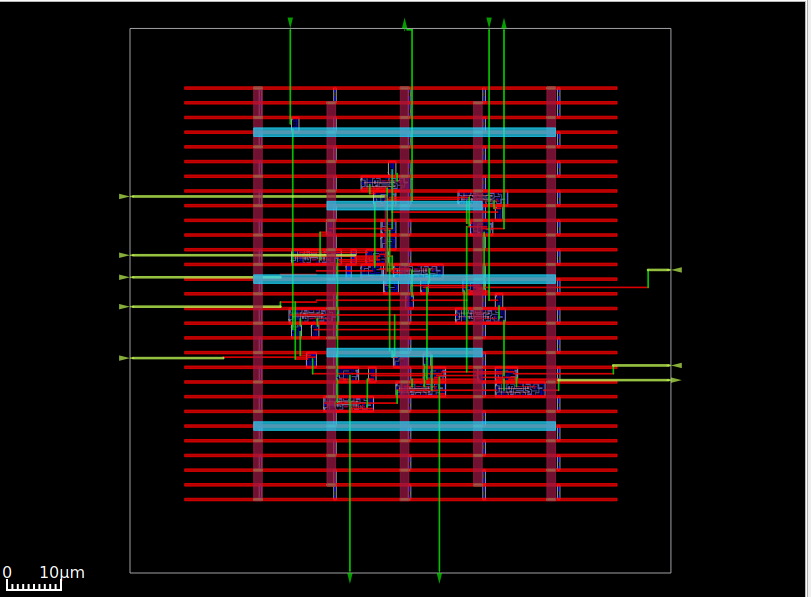

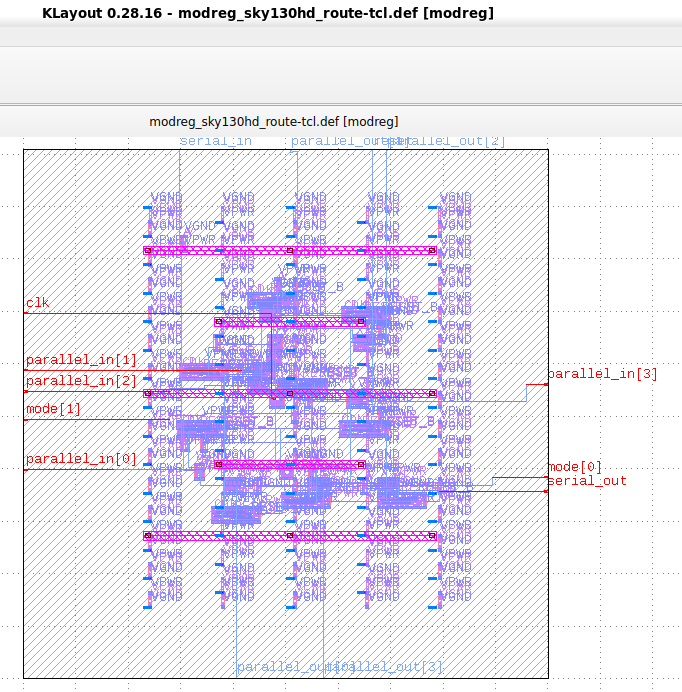

การเรียกใช้คำสั่งนี้มันจะสร้างเค้าโครง ASIC ซึ่งจะมองเห็นได้ใน Openroad GUI ตอนนี้เพื่อบันทึกไว้เป็น gdSii มันต้องการ klayout

sudo apt install klayout

เปิด klayout โดยใช้คำสั่งนี้

klayout &

ตอนนี้คลิกที่ปุ่มไฟล์และเลือกตัวเลือก Reader จากนั้นคลิกที่แท็บ "Lef/def" มีไฟล์ "nangate45.lef" และยกเลิกการเลือกช่องทำเครื่องหมาย (ถ้าตรวจสอบ) หรือยังคงอยู่

/OpenROAD/test/Nangate45/Nangate45.lef

จากนั้นคลิกตกลง หลังจากนั้นคลิกอีกครั้งบนไฟล์และเลือกเปิดตอนนี้กล่องโต้ตอบจะเปิดขึ้นไปนำทางไปยัง

/OpenROAD/test/result

จะมีไฟล์ design.def คลิกที่ไฟล์ def และคลิกที่ตกลง ตอนนี้มันจะเปิดในโหมด GDSII และสามารถบันทึกเป็น GDSII

ตอนนี้การออกแบบพร้อมที่จะส่งไปที่โรงหล่อเพื่อผลิต

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.