O OpenRoad é o principal aplicativo fundamental de código aberto para design digital semicondutores. O fluxo OpenRoad oferece um fluxo autônomo e não humano em loop (NHIL), reviravolta 24 horas do RTL-GDSII para exploração rápida do design e implementação do projeto físico.

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

Teste a instalação: Escreva 'iVerilog' no terminal e pressione Enter a instalação bem -sucedida deve mostrar esta saída: iVerilog: nenhum arquivo de origem e sugeriria -c, -y etc.

sudo apt install gtkwave

Veremos como os sinais são plotados usando um exemplo no GTKWave.

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

Se o 'TCL Interp' não tiver um membro denominado 'resultado'.

cd covered

cd src

gedit report.c

No arquivo report.c, você verá uma lista de comandos #include. Encontre #include <tcl.h> e adicione o seguinte comando '#define use_interp_result 1' antes #include <tcl.h>.

Seu relatório ficará assim:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

Salve o arquivo relation.c. Execute o comando make novamente e prossiga com o processo de instalação, como mostrado acima.

código Verilog de origem:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

Código verilog de teste:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

• Inicie a distribuição Linux e faça um diretório $ mkdir icarus_codes

onde os códigos Ícarus são o nome do diretório.

• Altere o diretório para os códigos Icarus. Para simulação, você precisa de um código Verilog para a funcionalidade implementada e um banco de teste no formato .v. Inclua aqueles no diretório de trabalho. Digamos que meu código Verilog se chama Mycounter.v e o teste é Testbench.v . Para simular:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

Um arquivo de despejo, que eu nomeei como count.vcd no banco de teste, é criado e você também pode ver a saída no terminal. Você também pode visualizar a saída no GTKWave

$ gtkwave count.vcd Este comando inicia o aplicativo GTKWave Analyzer. No painel esquerdo, expanda o teste e clique na subpasta. Ele se expandirá para mostrar o relógio de entrada, redefinir e sair da forma de onda [3: 0]. Arraste -os para o painel Signals e analise os resultados.

Para estimar a porcentagem do projeto RTL testado pelo banco de teste, é usada a ferramenta de analisador de cobertura de código verilog coberto. • Gere o relatório de cobertura de código no mesmo diretório, IE, Códigos Icarus, executando o seguinte comando

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

• Para visualizar o relatório de cobertura, execute

$ covered report -d v Mycounter.cdd

O relatório de cobertura é exibido no terminal.

Se encontrado algum erro chamado "Falha de segmentação", tente isto:

sudo apt-get install gedit

Abra o arquivo VCD gerado no GEDIT, encontre a linha "$ comentário mostre os valores dos parâmetros. $ end" e exclua -o.

Salve o arquivo VCD e, em seguida, execute o fluxo, ele deve funcionar agora.

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

Após a instalação, tente invocar Yosys como: ./yosys a ferramenta é lançada, e o prompt de comando muda para yosys>

Aqui eu dei ao arquivo da biblioteca chamado Nangate45_typ.lib

Para sintetizar qualquer arquivo de origem Verilog usando YOSYS, este arquivo de biblioteca deve ser incluído no script de automação TCL.

Faça um arquivo chamado yosys_commands.tcl e coloque essas linhas no arquivo e salve.

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

Este script TCL deve ser executado, depois que Yosys for invocado. Isso automatizará o processo de sintetizar e escreverá a lista de netlist sintetizada do arquivo verilog de origem

Inicie a ferramenta Yosys $ yosys estou usando um arquivo yosys_commands.tcl. yosys> script yosys_commands.tcl

Da mesma forma, execute os scripts de not_opt.tcl e opt.tcl dados para visualizar o diagrama de blocos não otimizado e diagramas de blocos otimizados, respectivamente, na janela GraphViz (XDOT)

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

Se o erro ocorrer como Cmake error at CMakelists.txt , vá para o diretório inicial usando o comando "cd" e instale

sudo apt-get install libeigen3-dev

Mais uma vez, vá para o diretório de compilação no OpenSta e configure a construção executando o seguinte comando:

cmake ..

Se novamente algum erro de cmake, mova -se novamente para o diretório inicial e instale o CUDD.

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

Agora o CUDD está instalado com sucesso. Agora mude para o OpenSta Directory

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

Agora invoce o OpenSta do terminal, simplesmente digite "Sta" e pressione Enter, ele mudou o prompt para

sta [~/working_directory]

or,

it will be shown like

%

Após a instalação bem -sucedida do OpenSta, execute o time.tcl para analisar o tempo de entradas e saídas, após esse execução power.tcl para analisar a dissipação de energia pelo circuito projetado.

Para análise de tempo usando o OpenSta

% source time.tcl

Para análise de energia usando o OpenSta

% source power.tcl

Faça o download do OpenRoad Repository

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

Instalar dependências

sudo ./etc/DependencyInstaller.sh

Construir o OpenRoad

mkdir build

cd build

cmake ..

sudo make

sudo make install

Se depois de executar o "cmake", ele mostrar um erro como: CMake Error: Could not find CMAKE_ROOT !!! Em seguida, execute export PATH=/usr/local/bin/cmake:$PATH e execute echo $CMAKE_ROOT , ele deve refletir o caminho, depois executar executar executar "cmake" e agin run "make & make install"

Se ainda ocorrerem erros:

sudo apt install swig

sudo apt update

Invoque a ferramenta OpenRoad do terminal e deve ser alterada para openroad>

Script usado para executar a atividade:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

Write design_nangate45.tcl Arquivo

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

Agora todos os arquivos estão prontos, alguns arquivos específicos precisam copiar na pasta "OpenRoad/Test", esta é:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

Depois de copiar esses arquivos para a pasta OpenROAD/test , vá para o mesmo diretório e invocar o OpenRoad para copiar arquivos de um diretório para outro diretório é:

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

então

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

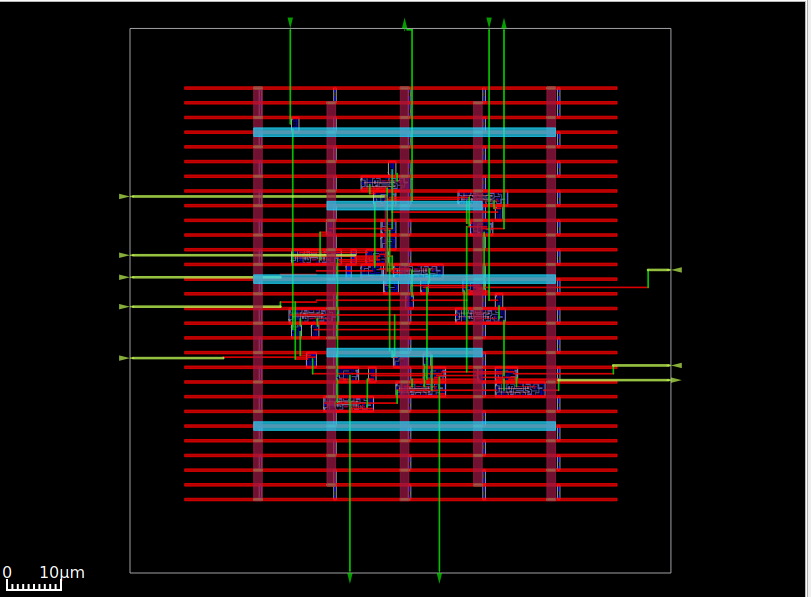

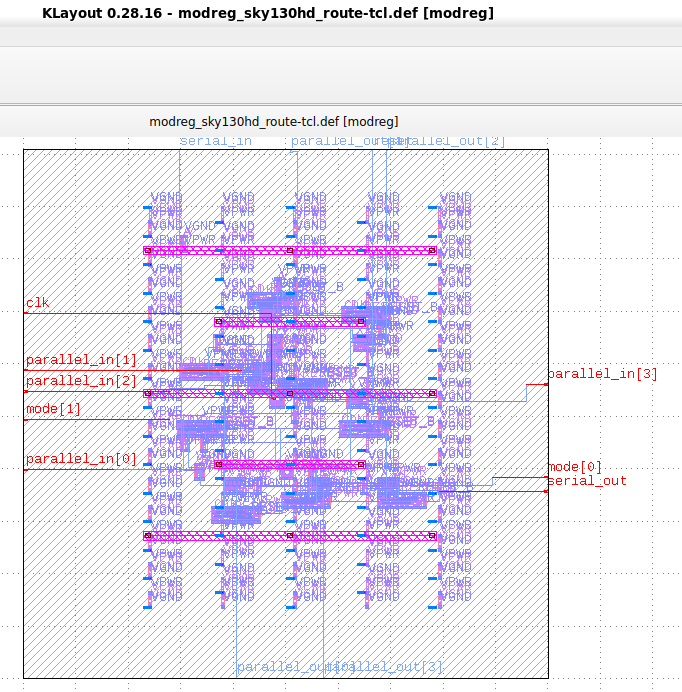

Executando este comando, ele gerará um layout da ASIC, que será visível no OpenRoad GUI agora para salvá -lo como GDSII, ele precisa de Klayout.

sudo apt install klayout

Abra o Klayout usando este comando

klayout &

Agora clique no botão do arquivo e escolha a opção do leitor e clique na guia "Lef/def", lá "nangate45.lef" o arquivo precisa ser colocado e desmarcar a caixa de seleção (se verificado) ou permanecer no mesmo local de "Nangate45.lef" está

/OpenROAD/test/Nangate45/Nangate45.lef

Em seguida, clique em OK. Depois disso, clique novamente em arquivo e escolha aberto, agora uma caixa de diálogo será aberta, navegará para

/OpenROAD/test/result

O arquivo design.def será localizado, clique no arquivo def e clique em OK. Agora ele será aberto no modo GDSII e pode ser salvo como GDSII.

Agora, o design está pronto para enviar para a fundação para a fabricação.

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.