OpenRoad adalah aplikasi dasar open-source terkemuka untuk desain digital semikonduktor. Aliran OpenRoad memberikan aliran otonom, no-human-in-loop (NHIL), perputaran 24 jam dari RTL-GDSII untuk eksplorasi desain yang cepat dan implementasi desain fisik.

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

Uji instalasi: Tulis 'iverilog' di terminal dan tekan enter instalasi yang berhasil harus menunjukkan output ini: iverilog: tidak ada file sumber dan akan menyarankan -c, -y dll.

sudo apt install gtkwave

Kita akan melihat bagaimana sinyal diplot menggunakan contoh di GTKWave.

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

Jika 'TCL Interp ′ tidak memiliki anggota yang bernama' Hasil ′ Terjadi kesalahan:

cd covered

cd src

gedit report.c

Di file Report.c Anda akan melihat daftar perintah #include. Temukan #include <tcl.h> dan tambahkan perintah berikut '#define use_interp_result 1' sebelum #include <tcl.h>.

Laporan Anda akan terlihat seperti ini:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

Simpan file Report.c. Jalankan perintah Make lagi dan lanjutkan dengan proses instalasi seperti yang ditunjukkan di atas.

Sumber Verilog Code:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

TestBench Verilog Code:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

• Luncurkan distribusi Linux dan buat direktori $ mkdir icarus_codes

di mana kode icarus adalah nama direktori.

• Ubah Direktori ke Kode Icarus. Untuk simulasi, Anda memerlukan kode Verilog untuk fungsionalitas yang diimplementasikan dan bangku uji dalam format .v. Sertakan yang ada di direktori kerja. Katakanlah kode verilog saya bernama Mycounter.v dan testbench adalah Testbench.v . Untuk mensimulasikan:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

File dump, yang saya sebut sebagai count.vcd di bangku uji, dibuat, dan Anda dapat melihat output di terminal juga. Anda juga dapat melihat output di GTKWave

$ gtkwave count.vcd Perintah ini meluncurkan aplikasi GTKwave Analyzer. Di panel kiri, perluas testbench dan klik pada subfolder. Ini akan diperluas untuk menampilkan jam input, reset dan output bentuk gelombang keluar [3: 0]. Seret itu ke panel Sinyal dan analisis hasilnya.

Untuk memperkirakan persentase desain RTL yang diuji oleh bangku uji, alat penganalisis cakupan kode Verilog tertutup digunakan. • Hasilkan laporan cakupan kode di direktori yang sama yaitu, kode icarus dengan menjalankan perintah berikut

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

• Untuk melihat laporan cakupan, jalankan

$ covered report -d v Mycounter.cdd

Laporan cakupan ditampilkan di terminal.

Jika mengalami kesalahan yang disebut "kesalahan segmentasi" coba ini:

sudo apt-get install gedit

Buka file VCD yang dihasilkan di gedit, temukan baris "$ komentar menunjukkan nilai parameter. $ end" dan hapus.

Simpan file VCD kemudian AGIN menjalankan aliran, itu harus berfungsi sekarang.

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

Setelah menginstal, cobalah menggunakan Yosys seperti: ./yosys alat diluncurkan, dan command prompt berubah menjadi yosys>

Di sini saya telah memberikan file perpustakaan bernama Nangate45_typ.lib

Untuk mensintesis file sumber Verilog menggunakan yosys, file perpustakaan ini harus dimasukkan dalam skrip otomatisasi TCL.

Buat file bernama yosys_commands.tcl dan masukkan baris ini ke dalam file dan simpan.

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

Skrip TCL ini harus dijalankan, setelah Yosys dipanggil. Ini akan mengotomatiskan proses sintesis dan menulis netlist yang disintesis dari file Sumber Verilog

Luncurkan YoSys Tool $ yosys Saya menggunakan file yosys_commands.tcl. yosys> script yosys_commands.tcl

Demikian pula Jalankan skrip not_opt.tcl dan opt.tcl yang diberikan untuk melihat diagram blok yang tidak dioptimalkan dan diagram blok yang dioptimalkan masing-masing di jendela GraphViz (XDOT)

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

Jika kesalahan datang seperti Cmake error at CMakelists.txt maka pindah ke direktori home menggunakan perintah "CD" dan instal

sudo apt-get install libeigen3-dev

Sekali lagi pindah ke direktori build di OpenSta dan konfigurasikan build dengan mengeksekusi perintah berikut:

cmake ..

Jika sekali lagi kesalahan CMake maka lagi pindah ke Home Directory dan instal CUDD.

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

Sekarang Cudd berhasil diinstal. Sekarang pindah ke direktori opensta

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

Sekarang Invoke OpenSta dari Terminal dengan cukup ketik "STA" dan tekan Enter itu mengubah prompt menjadi

sta [~/working_directory]

or,

it will be shown like

%

Setelah pemasangan OpenSta yang berhasil, jalankan time.tcl untuk menganalisis waktu input dan output, setelah itu run power.tcl untuk menganalisis disipasi daya dengan sirkuit yang dirancang.

Untuk analisis waktu menggunakan OpenSta

% source time.tcl

Untuk analisis daya menggunakan OpenSta

% source power.tcl

Unduh Repositori OpenRoad

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

Instal dependensi

sudo ./etc/DependencyInstaller.sh

Membangun openroad

mkdir build

cd build

cmake ..

sudo make

sudo make install

Jika setelah menjalankan "cmake" itu menunjukkan kesalahan seperti: CMake Error: Could not find CMAKE_ROOT !!! Kemudian jalankan export PATH=/usr/local/bin/cmake:$PATH dan jalankan echo $CMAKE_ROOT , itu harus mencerminkan jalur, lalu rerun "cmake" dan agin run "buat & buat instal"

Jika masih ada kesalahan yang terjadi:

sudo apt install swig

sudo apt update

Invoke Openroad Tool dari Terminal dan harus diubah menjadi openroad>

Script yang digunakan untuk menjalankan aktivitas:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

Tulis file design_nangate45.tcl

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

Sekarang semua file siap, beberapa file tertentu perlu disalin ke folder "OpenRoad/Test", ini adalah:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

Setelah menyalin file ini ke folder OpenROAD/test , buka direktori yang sama & Invoke OpenRoad untuk menyalin file dari satu direktori ke direktori lain adalah:

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

Kemudian

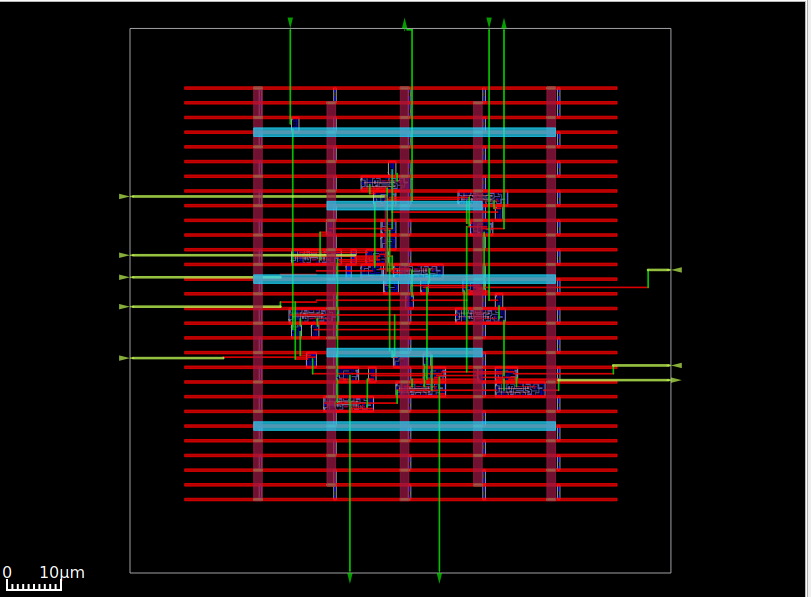

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

Menjalankan perintah ini, ia akan menghasilkan tata letak ASIC yang akan terlihat di OpenRoad GUI sekarang untuk menyimpannya karena GDSII membutuhkan klayout.

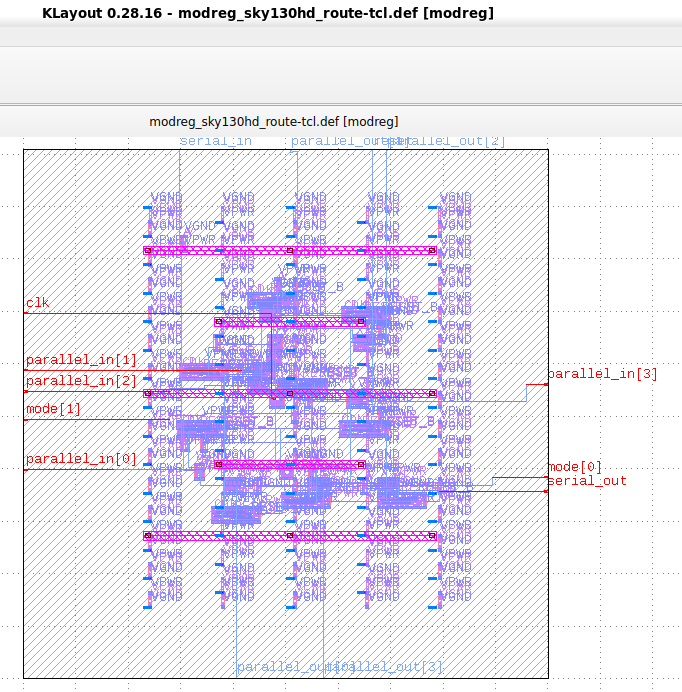

sudo apt install klayout

Buka klayout menggunakan perintah ini

klayout &

Sekarang klik tombol File dan pilih opsi pembaca lalu klik pada tab "LEF/DEF", ada file "nangate45.lef" perlu diletakkan dan hapus centang kotak centang (jika dicentang) atau tetap lokasi yang sama dari "nangate45.lef" adalah

/OpenROAD/test/Nangate45/Nangate45.lef

lalu klik OK. Setelah itu klik lagi di file dan pilih Buka, sekarang kotak dialog akan terbuka, navigasikan ke

/OpenROAD/test/result

Ada file design.def akan ditemukan, klik pada file DEF dan klik OK. Sekarang akan terbuka dalam mode GDSII dan dapat disimpan sebagai GDSII.

Sekarang desain siap dikirim ke Foundry for Fabrikasi.

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.