Openroad هو التطبيق الرئيسي المفتوح المصدر للتصميم الرقمي أشباه الموصلات. يوفر تدفق Openroad Flow تدفقًا مستقلًا غير إنساني (NHIL) (NHIL) ، وتحول على مدار 24 ساعة من RTL-GDSII لاستكشاف التصميم السريع وتنفيذ التصميم المادي.

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

اختبار التثبيت: اكتب "iverilog" في المحطة الطرفية واضغط على إدخال التثبيت الناجح يجب أن يوضح هذا المخرج: Iverilog: لا توجد ملفات مصدر ، وسوف تقترح -C ، -y إلخ.

sudo apt install gtkwave

سنرى كيف يتم رسم الإشارات باستخدام مثال في GTKWAVE.

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

إذا كان "Tcl interp" لا يحتوي على عضو مسمى "حدث خطأ: حدث خطأ:

cd covered

cd src

gedit report.c

في ملف Report.c سترى قائمة بأوامر #Include. ابحث عن #include <tcl.h> وأضف الأمر التالي "#define use_interp_result 1 'قبل #include <tcl.h>.

سيبدو تقريرك هكذا:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

احفظ ملف التقرير. قم بتشغيل الأمر Make مرة أخرى وانتقل إلى عملية التثبيت كما هو موضح أعلاه.

رمز المصدر فيريلوغ:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

رمز Testbench Verilog:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

• قم بتشغيل توزيع Linux وصنع دليلًا $ mkdir icarus_codes

حيث رموز icarus هي اسم الدليل.

• تغيير الدليل إلى رموز Icarus. للمحاكاة ، تحتاج إلى رمز Verilog للوظائف التي تم تنفيذها ومقعد اختبار بتنسيق .V. تشمل تلك الموجودة في دليل العمل. دعنا نقول أن رمز Verilog الخاص بي يسمى Mycounter.v و testbench هو Testbench.v . لمحاكاة:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

يتم إنشاء ملف تفريغ ، والذي قمت بتسميته كـ count.vcd في مقعد الاختبار ، ويمكنك رؤية الإخراج على المحطة أيضًا. يمكنك أيضًا عرض الإخراج في GTKWAVE

$ gtkwave count.vcd يقوم هذا الأمر بتشغيل تطبيق محلل GTKWAVE. في اللوحة اليسرى ، قم بتوسيع testbench وانقر على المجلد الفرعي. سوف يتوسع لإظهار ساعة الإدخال ، وإعادة تعيين وإخراج الموجي خارج [3: 0]. اسحب تلك إلى لوحة الإشارات وتحليل النتائج.

لتقدير النسبة المئوية لتصميم RTL الذي تم اختباره بواسطة مقعد الاختبار ، يتم استخدام أداة محلل رمز Verilog المغطاة. • إنشاء تقرير تغطية الكود في نفس الدليل أي رموز ICARUS عن طريق تنفيذ الأمر التالي

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

• لعرض تقرير التغطية ، تنفذ

$ covered report -d v Mycounter.cdd

يتم عرض تقرير التغطية في المحطة.

إذا واجه أي خطأ يسمى "خطأ التجزئة" ، فحاول:

sudo apt-get install gedit

افتح ملف VCD الذي تم إنشاؤه في GEDIT ، ابحث عن السطر "$ Comment Show the Parameter Base. $ End" وحذفه.

احفظ ملف VCD ثم تشغيل التدفق ، يجب أن يعمل الآن.

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

بعد yosys> ، حاول استدعاء yosys مثل ./yosys

لقد أعطيت هنا ملف المكتبة المسماة Nangate45_typ.lib

لتوليف أي ملف مصدر Verilog باستخدام yosys يجب تضمين ملف المكتبة هذا في البرنامج النصي Automation TCL.

قم بعمل ملف يسمى yosys_commands.tcl ووضع هذه الخطوط في الملف وحفظه.

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

يجب تشغيل هذا البرنامج النصي TCL ، بعد استدعاء Yosys. سيؤدي ذلك إلى أتمتة عملية التوليف واكتب قائمة Netlist المتوازنة من ملف Verilog المصدر

قم بتشغيل أداة yosys $ yosys أنا أستخدم ملف yosys_commands.tcl. yosys> script yosys_commands.tcl

بالمثل ، قم بتشغيل البرامج النصية not_opt.tcl و opt.tcl لعرض مخطط الكتلة غير المحسّن ومخططات الكتلة المحسنة على التوالي في نافذة GraphViz (XDOT)

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

إذا حدث خطأ مثل Cmake error at CMakelists.txt ، فانتقل إلى الدليل المنزلي باستخدام أمر "CD" وتثبيته

sudo apt-get install libeigen3-dev

انتقل مرة أخرى إلى دليل الإنشاء في Opensta وتكوين البناء من خلال تنفيذ الأمر التالي:

cmake ..

إذا مرة أخرى أي خطأ في CMake ، فانتقل مرة أخرى إلى الدليل المنزلي وقم بتثبيت CUDD.

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

الآن تم تثبيت الحضن بنجاح. انتقل الآن إلى دليل Opensta

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

الآن احتجز Opensta من المحطة عن طريق الكتابة ببساطة "STA" واضغط على إدخالها غيرت موجه إلى

sta [~/working_directory]

or,

it will be shown like

%

بعد التثبيت الناجح لـ OpenSta قم بتشغيل time.tcl لتحليل توقيت المدخلات والمخرجات ، بعد ذلك تشغيل power.tcl لتحليل تبديد الطاقة بواسطة الدائرة المصممة.

لتحليل الوقت باستخدام Opensta

% source time.tcl

لتحليل الطاقة باستخدام Opensta

% source power.tcl

تنزيل مستودع Openroad

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

تثبيت التبعيات

sudo ./etc/DependencyInstaller.sh

بناء Openroad

mkdir build

cd build

cmake ..

sudo make

sudo make install

إذا بعد تشغيل "cmake" ، فإنه يظهر خطأ مثل: CMake Error: Could not find CMAKE_ROOT !!! ثم قم بتشغيل export PATH=/usr/local/bin/cmake:$PATH وقم بتشغيل echo $CMAKE_ROOT ، يجب أن يعكس المسار ، ثم إعادة تشغيل "cmake" و agin run "make & make install"

إذا كانت لا تزال تحدث أي أخطاء:

sudo apt install swig

sudo apt update

استدعاء أداة Openroad من المحطة ويجب تغييرها إلى openroad>

البرنامج النصي المستخدم لتنفيذ النشاط:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

اكتب ملف design_nangate45.tcl

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

الآن جميع الملفات جاهزة ، تحتاج بعض الملفات المحددة إلى نسخها إلى مجلد "Openroad/Test" ، وهذا هو:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

بعد نسخ هذه الملفات إلى مجلد OpenROAD/test ، انتقل إلى نفس الدليل واستدعاء OpenRoad لنسخ الملفات من دليل إلى دليل آخر هو:

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

ثم

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

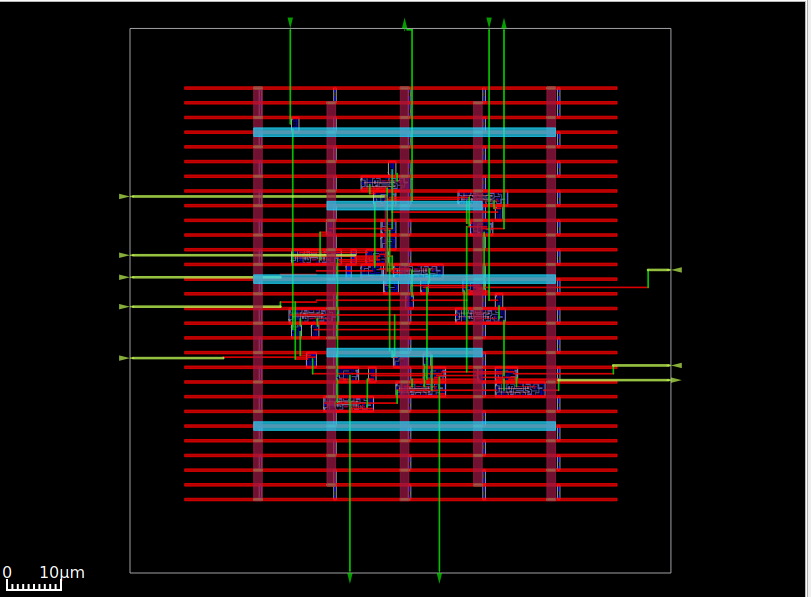

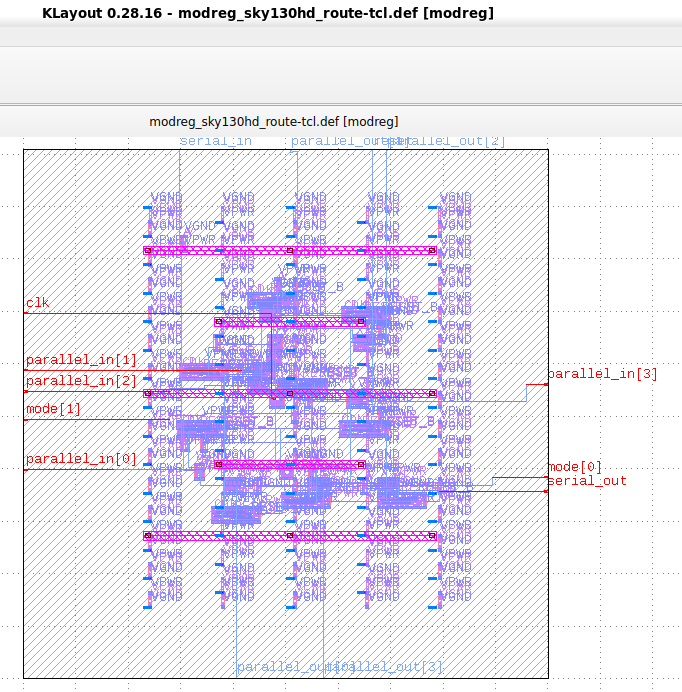

تشغيل هذا الأمر ، سيؤدي إلى إنشاء تصميم ASIC الذي سيكون مرئيًا في واجهة المستخدم الرسومية Openroad الآن لإنقاذه كـ GDSII ، فهو يحتاج إلى klayout.

sudo apt install klayout

افتح Klayout باستخدام هذا الأمر

klayout &

الآن انقر فوق زر الملف واختر خيار القارئ ، ثم انقر فوق علامة التبويب "LEF/DEF" ، هناك "nangate45.lef" يجب وضع ملف مربع الاختيار (إذا تم التحقق منه) أو تبقى نفس موقع "nangate45.lef"

/OpenROAD/test/Nangate45/Nangate45.lef

ثم انقر فوق موافق. بعد ذلك انقر مرة أخرى على الملف واختر فتح ، الآن سيتم فتح مربع حوار ، انتقل إلى

/OpenROAD/test/result

يوجد ملف design.def ، انقر فوق ملف DEF وانقر فوق "موافق". الآن سيتم فتحه في وضع GDSII ويمكن حفظه كـ GDSII.

الآن التصميم جاهز للإرسال إلى مسبك للتصنيع.

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.