オープンロードは、半導体デジタルデザインの主要なオープンソースの基礎アプリケーションです。オープンロードの流れは、RTL-GDSIIから24時間のターンアラウンドで、迅速な設計探索と物理デザインの実装を行うために、自律的でヒューマンのないループ(NHIL)フローを提供します。

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

インストールのテスト:端末に「iverilog」を書き込み、Enter成功したインストールを押します。

sudo apt install gtkwave

GTKWAVEの例を使用して、信号がどのようにプロットされるかを確認します。

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

'tcl interp'に 'result'エラーという名前のメンバーが発生していない場合:

cd covered

cd src

gedit report.c

Report.cファイルには、#includeコマンドのリストが表示されます。 #include <tcl.h>を見つけて、次のコマンドを追加します '#define use_interp_result 1' #include <tcl.h>。

あなたのレポートは次のようになります:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

Report.cファイルを保存します。 Makeコマンドをもう一度実行し、上記のようにインストールプロセスを続行します。

ソースVerilogコード:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

TestBench Verilogコード:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

•Linuxディストリビューションを起動し、ディレクトリを作成します$ MKDIR ICARUS_CODES

Icarusコードはディレクトリの名前です。

•ディレクトリをIcarusコードに変更します。シミュレーションには、実装された機能にはVerilogコードと.V形式のテストベンチが必要です。ワーキングディレクトリにそれらを含めます。私のVerilogコードの名前はMycounter.vで、TestbenchはTestbench.vです。シミュレートするには:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

テストベンチでcount.vcdと命名したダンプファイルが作成されており、ターミナルにも出力を確認できます。 GTKWAVEで出力を表示することもできます

$ gtkwave count.vcdこのコマンドは、gtkwaveアナライザーアプリケーションを起動します。左パネルで、テストベンチを展開し、サブフォルダーをクリックします。展開して、入力クロック、リセット、出力波形を表示します[3:0]。それらを信号パネルにドラッグし、結果を分析します。

テストベンチでテストされたRTL設計の割合を推定するために、対象となるVerilogコードカバレッジアナライザーツールが使用されます。 •次のコマンドを実行して、同じディレクトリ、つまりiCarusコードでコードカバレッジレポートを生成します

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

•カバレッジレポートを表示するには、実行します

$ covered report -d v Mycounter.cdd

カバレッジレポートは端末に表示されます。

「セグメンテーション障害」と呼ばれるエラーが発生した場合は、これを試してください。

sudo apt-get install gedit

GEDITで生成されたVCDファイルを開き、「$コメントがパラメーター値を表示します。$ end」を見つけて削除します。

VCDファイルを保存してから、Agin Flowを実行すると、今すぐ機能します。

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

インストール後、次のようなYosysを呼び出してみてください: ./yosysツールが起動し、コマンドプロンプトがyosys>

ここで、 Nangate45_typ.libという名前のライブラリファイルを提供しました

YOSYSを使用してVerilogソースファイルを合成するには、このライブラリファイルをTCL Automation Scriptに含める必要があります。

yosys_commands.tclという名前のファイルを作成し、この行をファイルに入れて保存します。

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

Yosysが呼び出された後、このTCLスクリプトは実行する必要があります。これにより、合成プロセスを自動化し、ソースVerilogファイルから合成されたネットリストを書き込みます

Yosys Toolを起動します$ yosys YOSYS_COMMANDS.TCLファイルを使用しています。 yosys> script yosys_commands.tcl

同様に、Graphviz(XDOT)ウィンドウでそれぞれ最適化されていないブロック図と最適化されたブロック図を表示するために、指定されたnot_opt.tclおよびopt.tclスクリプトを実行します

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

Cmake error at CMakelists.txtのようにエラーが発生した場合、「cd」コマンドとインストールを使用してホームディレクトリに移動します

sudo apt-get install libeigen3-dev

再びOpenstaのビルドディレクトリに移動し、次のコマンドを実行してビルドを構成します。

cmake ..

cmakeエラーがある場合は、再びホームディレクトリに移動し、cuddをインストールします。

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

Cuddが正常にインストールされました。ここで、Openstaディレクトリに移動します

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

次に、ターミナルからopenstaを呼び出して「sta」と入力し、Enterを押すだけでプロンプトを変更しました

sta [~/working_directory]

or,

it will be shown like

%

Opensta Run the time.tclのインストールが成功した後、入力と出力のタイミングを分析するために、その後、 power.tclを実行して、設計された回路による電力散逸を分析します。

Openstaを使用した時間分析のため

% source time.tcl

Openstaを使用した電力分析用

% source power.tcl

Openroadリポジトリをダウンロードしてください

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

依存関係をインストールします

sudo ./etc/DependencyInstaller.sh

オープンロードを建設します

mkdir build

cd build

cmake ..

sudo make

sudo make install

「cmake」を実行した後、 CMake Error: Could not find CMAKE_ROOT !!! export PATH=/usr/local/bin/cmake:$PATH and run echo $CMAKE_ROOTを実行すると、パスを反映してから、「cmake」とagin run "make&make install"を再実行する必要があります。

まだエラーが発生した場合:

sudo apt install swig

sudo apt update

ターミナルからオープンロードツールを呼び出すと、 openroad>

アクティビティを実行するために使用されるスクリプト:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

design_nangate45.tclファイルを書き込みます

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

これですべてのファイルが準備が整っているため、一部の特定のファイルが「OpenRad/Test」フォルダーにコピーする必要があります。これは次のとおりです。

design.v

synth_design.v

top.sdc

design_nangate45.tcl

このファイルをOpenROAD/testフォルダーにコピーした後、同じディレクトリに移動して、あるディレクトリから別のディレクトリにファイルをコピーするためにOpenRaodを呼び出します。

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

それから

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

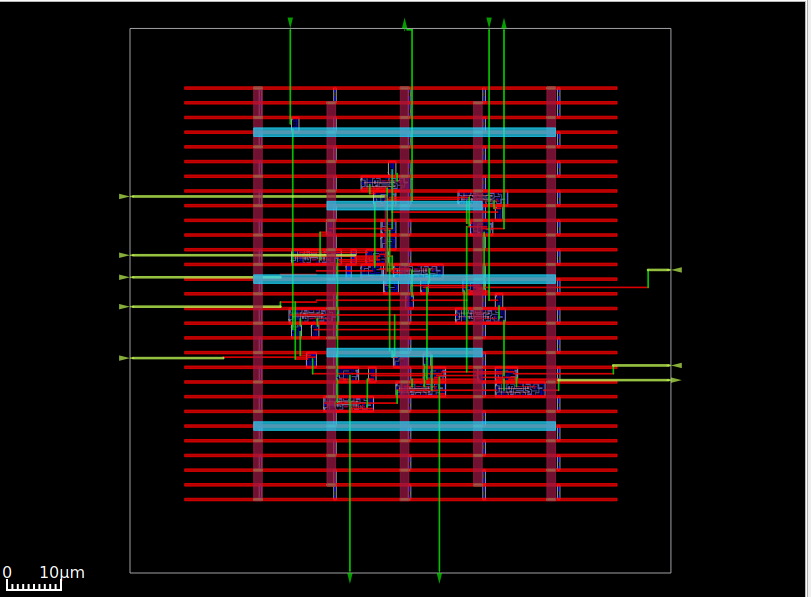

このコマンドを実行すると、ASICレイアウトが生成されます。これは、gdsiiが必要な場合に保存するために、オープンロードGUIで表示されます。

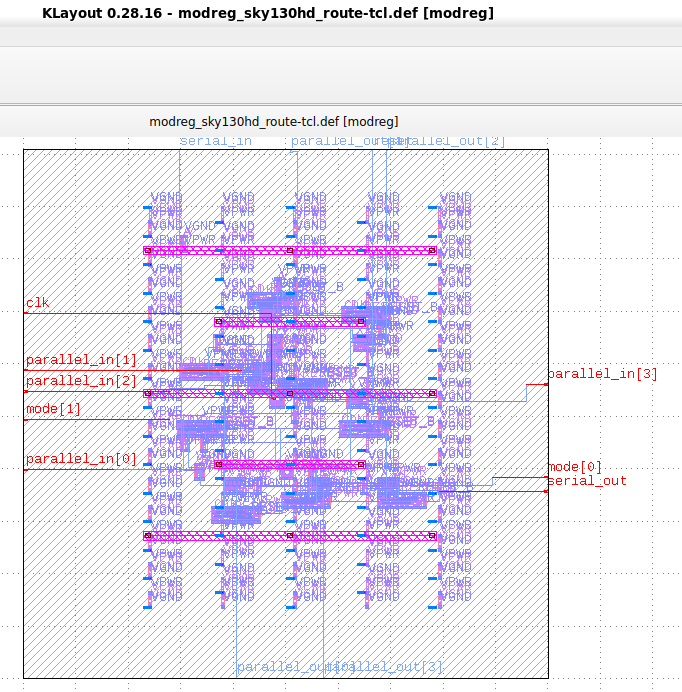

sudo apt install klayout

このコマンドを使用してklayoutを開きます

klayout &

[ファイル]ボタンをクリックして[リーダー]オプションを選択し、[LEF/DEF]タブをクリックして、「nangate45.lef」ファイルを配置してチェックする必要があります(チェックされた場合)または「nangate45.lef」の同じ場所のままです

/OpenROAD/test/Nangate45/Nangate45.lef

[OK]をクリックします。その後、もう一度[ファイル]をクリックして開くことを選択します。これでダイアログボックスが開き、次のように移動します

/OpenROAD/test/result

そこにdesign.defファイルが配置され、defファイルをクリックして[OK]をクリックします。これでGDSIIモードで開き、GDSIIとして保存できます。

現在、デザインはファウンドリーに製造のために送信する準備ができています。

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.