OpenRoad est la principale application fondamentale open-source pour la conception numérique semi-conducteurs. Le flux OpenRoad fournit un flux autonome et non humain en boucle (NHIL), un revirement de 24 heures de RTL-GDSII pour une exploration rapide de la conception et une mise en œuvre de la conception physique.

Title:

RTL-GDSII flow Using OpenROAD

____________________________________________________

| ->Synthesis |

| : Inputs [RTL, SDC, .lib, .lef] |

| : Logic Synthesis (Yosys) |

| : Output files [Netlist, SDC] |

| ->Floorplan |

| : Floorplan Initialization |

| : IO placement (random) |

| : Timing-driven mixed-size placement |

| : Macro placement |

| : Tapcell and welltie insertion |

| : PDN generation |

| ->Placement |

| : Global placement without placed IOs |

| : IO placement (optimized) |

| : Global placement with placed IOs |

| : Resizing and buffering |

| : Detailed placement |

| ->CTS : Clock Tree Synthesis |

| : Timing optimization |

| : Filler cell insertion |

| ->Routing |

| : Global Routing |

| : Detailed Routing |

| ->Finishing |

| : Metal Fill insertion |

| : Signoff timing report |

| : Generate GDSII (KLayout) |

| : DRC/LVS check (KLayout) |

|____________________________________________________|

sudo apt-get update

sudo apt - get update

sudo apt - get install gperf

sudo apt - get install autoconf

sudo apt - get install gcc g ++

sudo apt - get install flex

sudo apt - get install bison

wget https://github.com/steveicarus/iverilog/archive/refs/tags/v12_0.tar.gz

tar -xvzf v12_0.tar.gz

cd iverilog-12_0

sh autoconf.sh

./configure

sudo make

sudo make install

Testez l'installation: écrivez 'iverilog' dans le terminal et appuyez sur Installation réussie doit afficher cette sortie: iverilog: pas de fichiers source et suggérerait -c, -y etc.

sudo apt install gtkwave

Nous verrons comment les signaux sont tracés en utilisant un exemple dans gtkwave.

sudo apt update

sudo apt-get install zlib1g-dev

git clone https://git.savannah.gnu.org/git/libiconv.git

sudo apt-get install tcl8.6

sudo apt-get install tcl8.6-dev

sudo apt-get install tk8.6

sudo apt-get install tk8.6-dev

sudo apt-get install doxygen

git clone https://github.com/chiphackers/covered

cd covered

./configure

sudo make

sudo make install

Si «TCL Interp» n'a pas de membre nommé «résultat», l'erreur s'est produite:

cd covered

cd src

gedit report.c

Dans le fichier report.c, vous verrez une liste des commandes #include. Recherchez #include <tcl.h> et ajoutez la commande suivante '#define use_interp_result 1' avant #include <tcl.h>.

Votre rapport ressemblera à ceci:

#ifdef HAVE TCLTK

#define USE_INTERP_RESULT 1

#include <tcl.h>

Enregistrez le fichier report.c. Exécutez à nouveau la commande Make et continuez avec le processus d'installation comme indiqué ci-dessus.

Code Verilog source:

// 4 bit synchronous counter

module Mycounter (CLK, RST , OUT );

input CLK, RST;

output [3:0] OUT ;

reg [3:0] OUT;

always @( posedge CLK )

begin

if (RST == 1'b1 )

OUT <= 4'b0000 ;

else

OUT <=OUT+1;

end

endmodule

TestBench Verilog Code:

// Testbench for a 4 bit synchronous counter

module Testbench ();

reg Clock , Reset ;

wire [3:0] Count ;

// instantiate the DUV and make connections

Mycounter I1(.CLK ( Clock ),. RST ( Reset ),.OUT( Count ) );

// initialize the Testbench

initial begin

$display (" Starting simulation ...");

Clock = 1'b0 ;

Reset = 1'b1 ; // reset the counter at t=0

# 100 Reset = 1'b0 ; // remove reset at t=100

# 2000 Reset = 1'b1 ; // remove reset at t= 2100

# 400 $finish ; // end the simulation after t= 2500

end

// generate stimulus (in this case clock signal )

always #50 Clock =∼Clock ;// clock period =100

// monitor the response and save it in a file

initial begin

$dumpfile ("count.vcd"); // specifies the VCD file

$dumpvars ; // dump all the variables

$monitor ("%d ,%b ,%b ,%d", $time , Clock , Reset , Count );

end

endmodule

• Lancez la distribution Linux et créez un répertoire $ mkdir icarus_codes

où icarus codes est le nom du répertoire.

• Modifier le répertoire en codes icarus. Pour la simulation, vous avez besoin d'un code Verilog pour les fonctionnalités implémentées et un banc de test au format .v. Incluez ceux dans le répertoire de travail. Disons que mon code Verilog est nommé Mycounter.v et que TestBench est Testbench.v . Pour simuler:

$ iverilog -o Mycounter Mycounter.v Testbench.v

$ vvp Mycounter

Un fichier de vidage, que j'ai nommé Count.vcd dans le banc de test, est créé, et vous pouvez également voir la sortie sur le terminal. Vous pouvez également afficher la sortie dans le gtkwave

$ gtkwave count.vcd Cette commande lance l'application GTKWAVE Analyzer. Dans le panneau de gauche, développez le banc d'essai et cliquez sur le sous-dossier. Il se développera pour afficher l'horloge d'entrée, réinitialiser et sortir la forme d'onde de sortie [3: 0]. Faites glisser ceux dans le panneau des signaux et analysez les résultats.

Pour estimer le pourcentage de conception RTL testée par le banc de test, l'outil d'analyseur de couverture de code Verilog couvert est utilisé. • Générez le rapport de couverture de code dans le même répertoire, c'est-à-dire les codes ICARUS en exécutant la commande suivante

$ covered score -t Testbench -v Testbench.v -v Mycounter.v -vcd count.vcd -o Mycounter.cdd

• Pour afficher le rapport de couverture, exécutez

$ covered report -d v Mycounter.cdd

Le rapport de couverture est affiché dans le terminal.

Si vous avez rencontré une erreur appelée "défaut de segmentation", essayez ceci:

sudo apt-get install gedit

Ouvrez le fichier VCD généré dans GEdit, recherchez la ligne "$ commentaire Affichez les valeurs des paramètres. $ end" et supprimez-le.

Enregistrez le fichier VCD puis AGIN exécute le flux, il devrait fonctionner maintenant.

sudo apt-get install -y build-essential clang bison flex libreadline-dev gawk tcl-dev libffi-dev git graphviz xdot pkg-config python3 libboost-system-dev libboost-python-dev libboost-filesystem-dev zlib1g-dev

git clone https://github.com/YosysHQ/yosys.git

git submodule update --init

cd yosys

sudo make

sudo make install

Après l'installation, essayez d'invoquer des yosys comme: ./yosys L'outil lance, et l'invite de commande change en yosys>

Ici, j'ai donné le fichier de bibliothèque nommé Nangate45_typ.lib

Pour synthétiser tout fichier source Verilog à l'aide de YOSYS, ce fichier de bibliothèque doit être inclus dans le script d'automatisation TCL.

Faites un fichier nommé yosys_commands.tcl et placez ces lignes dans le fichier et enregistrez.

#Read modules from verilog

read_verilog counter.v

#Elaborate design hierarchy

hierarchy −check −top Mycounter

#Translate Processes to netlist

proc

#mapping to the internal cell library

techmap

#mapping flip-flops to Nangate45_typ.lib

dfflibmap −liberty Nangate45_typ.lib

#mapping logic to Nangate45_typ.lib

abc -liberty Nangate45_typ.lib

#remove unused cells

clean

#write the synthesized design in a verilog file

write_verilog −noattr synth_Mycounter.v

Ce script TCL doit être exécuté, après que Yosys a été invoqué. Cela automatisera le processus synthétisé et rédigera la netlist synthétisée à partir du fichier Verilog source

Lancez l'outil YOSYS $ yosys J'utilise un fichier yosys_commands.tcl. yosys> script yosys_commands.tcl

Exécutez de même les scripts not_opt.tcl et opt.tcl donnés pour afficher respectivement le schéma de bloc non optimisé et les diagrammes de blocs optimisés dans la fenêtre Graphviz (XDOT)

sudo apt-get update

sudo apt-get install build-essential tcl-dev tk-dev cmake git

git clone https://github.com/The-OpenROAD-Project/OpenSTA.git

cd OpenSTA

mkdir build

cd build

cmake ..

Si l'erreur vient comme Cmake error at CMakelists.txt , passez au répertoire domestique à l'aide de la commande "CD" et installez

sudo apt-get install libeigen3-dev

Déplacez-vous à nouveau au répertoire de construction dans OpenSta et configurez la version en exécutant la commande suivante:

cmake ..

Si encore une erreur CMake, passez à nouveau au répertoire domestique et installez CUDD.

git clone https://github.com/ivmai/cudd.git

sudo apt-get install automake

sudo apt-get install autoconf m4 perl

cd cudd

autoreconf -i

mkdir build

cd build

../configure --prefix=$HOME/cudd

sudo make

sudo make install

Maintenant, CUDD est installé avec succès. Maintenant, déplacez-vous vers le répertoire OpenSta

cd OpenSTA

cd build

cmake .. -DUSE_CUDD=ON -DCUDD_DIR=$HOME/cudd

sudo make

sudo make install

Invoquez maintenant OpenSta du terminal en tapant simplement "STA" et appuyez sur Entrée, il a changé l'invite pour

sta [~/working_directory]

or,

it will be shown like

%

Après une installation réussie d'OpenSta, exécutez le time.tcl pour analyser le moment des entrées et des sorties, après cela, exécutez power.tcl pour analyser la dissipation de puissance par le circuit conçu.

Pour l'analyse du temps à l'aide d'OpenSta

% source time.tcl

Pour l'analyse de puissance à l'aide d'OpenSta

% source power.tcl

Télécharger le référentiel OpenRoad

git clone --recursive https://github.com/The-OpenROAD-Project/OpenROAD.git

cd OpenROAD

Installer des dépendances

sudo ./etc/DependencyInstaller.sh

Construisez OpenRoad

mkdir build

cd build

cmake ..

sudo make

sudo make install

Si après l'exécution de "cmake", il montre une erreur comme: CMake Error: Could not find CMAKE_ROOT !!! puis exécutez export PATH=/usr/local/bin/cmake:$PATH et exécutez echo $CMAKE_ROOT , il devrait refléter le chemin, puis relancer "cmake" et agin exécuter "faire et faire installer"

Si des erreurs sont toujours survenues:

sudo apt install swig

sudo apt update

Invoquez l'outil OpenRoad du terminal et il doit être changé en openroad>

Script utilisé pour exécuter l'activité:

design_nangate45.tcl

1. RTL Netlist: gcd_nangate45.v

(Location: OpenROAD/test/gcd_nangate45.v)

2. SDC file: gcd_nangate45.sdc

(Location: OpenROAD/test/gcd_nangate45.sdc)

3. Library file: Nangate45_typ.lib

(Location: OpenROAD/test/Nangate45/Nangate45_typ.lib)

4. LEF file

A. Technology Lef: Nangate45_tech.lef

(Location: OpenROAD/test/Nangate45/Nangate45_tech.lef)

B. Standard Cell Lef: Nangate45_stdcell.lef

(Location: OpenROAD/test/Nangate45/Nangate45_stdcell.lef)

Écrivez le fichier de design_nangate45.tcl

source "helpers.tcl"

source "flow_helpers.tcl"

source "Nangate45/Nangate45.vars"

set design "<design name>"

set top_module "<design main module>"

set synth_verilog "synth_design.v"

set sdc_file "top.sdc"

set die_area {0 0 100.13 100.8}

set core_area {10.07 11.2 90.25 91}

source -echo "flow.tcl”

Maintenant, tous les fichiers sont prêts, certains fichiers spécifiques doivent copier dans le dossier "OpenRoad / Tester", c'est:

design.v

synth_design.v

top.sdc

design_nangate45.tcl

Après avoir copié ces fichiers dans un dossier OpenROAD/test , accédez au même répertoire et appelez OpenRoad pour copier des fichiers d'un répertoire à un autre répertoire est:

sudo cp -i /path/of/your/directory/<filename> /path/to/directory/to/copy/

alors

openroad> sudo openroad -gui -log design_logfile.log design_nangate45.tcl

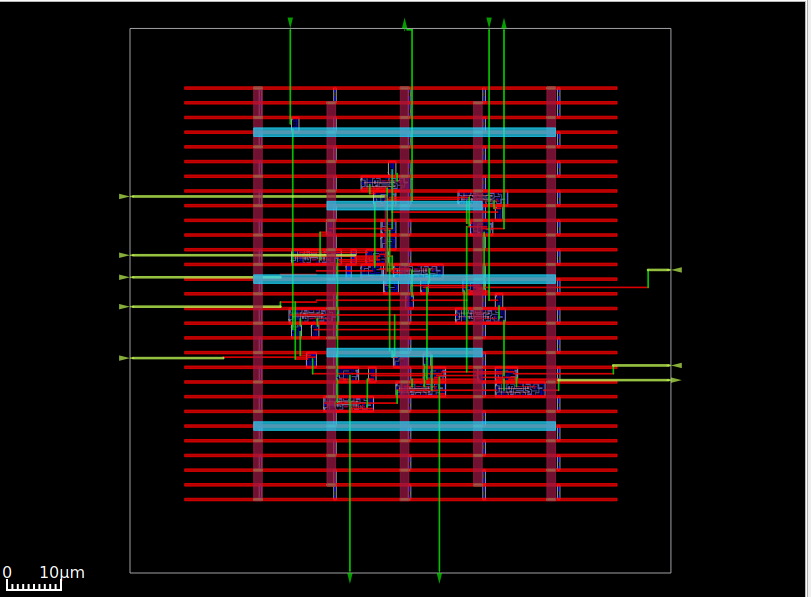

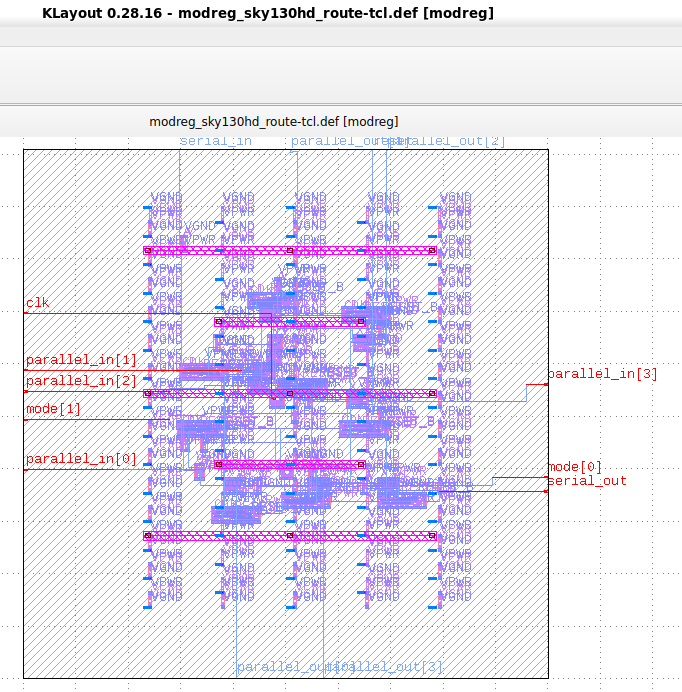

En exécutant cette commande, il générera maintenant la disposition ASIC qui sera visible dans OpenRoad GUI pour l'enregistrer en tant que gdsii, il a besoin de klayout.

sudo apt install klayout

Ouvrez Klayout en utilisant cette commande

klayout &

Maintenant, cliquez sur le bouton Fichier et choisissez l'option le lecteur, puis cliquez sur "Lef / Def", il y a le fichier "Nangate45.lef" doit être mis et décochez la case à cocher (si cochée) ou restez le même emplacement de "Nangate45.Lef" est

/OpenROAD/test/Nangate45/Nangate45.lef

puis cliquez sur OK. Après cela, cliquez à nouveau dans le fichier et choisissez Open, maintenant une boîte de dialogue s'ouvrira, accédez à

/OpenROAD/test/result

Le fichier design.def sera localisé, cliquez sur le fichier DEF et cliquez sur OK. Maintenant, il s'ouvrira en mode GDSII et peut être enregistré en tant que GDSII.

Maintenant, le design est prêt à être envoyé à la fonderie pour fabrication.

[1] Installation steps for The ICARUS Verilog Compilation System. [Online]. Available:

https://github.com/steveicarus/iverilog

[2] Installation steps for Covered - Verilog Code Coverage Analyzer. [Online]. Available:

https://github.com/chiphackers/covered/blob/master/INSTALL

[3] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[4] Installation steps for Yosys Open SYnthesis Suite. [Online]. Available: https:

//github.com/YosysHQ/yosys

[5] S. Saurabh, Introduction to VLSI Design Flow. Cambridge: Cambridge University Press,

2023.

[6] Yosys: Example Usage. [Online]. Available: https://yosyshq.net/yosys/

[7] Documentation for Yosys Open SYnthesis Suite commands. [Online]. Available:

https://yosyshq.readthedocs.io/projects/yosys/en/manual-rewrite/cmd ref.html

[8] Ajayi, Tutu, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny,

Andrew B. Kahng, Minsoo Kim et al. "Toward an open-source digital flow: First learnings

from the openroad project." In Proceedings of the 56th Annual Design Automation

Conference 2019, pp. 1-4. 2019.

[9] Ajayi, Tutu, and David Blaauw. "OpenROAD: Toward a self-driving, open-source digital

layout implementation tool chain." In Proceedings of Government Microcircuit

Applications and Critical Technology Conference. 2019.