ICE40 Power Testing

Das Ziel dieser Übung ist es, aus Sicht der Kraft zu verstehen, was die verschiedenen Kompromisse im ICE40 -FPGA sind. Dies würde es uns ermöglichen, batteriebetriebene Geräte zu entwerfen, die die FPGA verwenden, die Batterielebensdauer abschätzen und auch Entwurfszeitanleitungen bereitstellen.

Aufstellen

- Die verwendete Hardware ist das ICE40 Breakout Board von Gitter. Dieses Board wurde ausgewählt, als es alle Power Rails der FPGA ausbricht.

- Ich habe die PCF -Datei vom Upduino als identisch verwendet.

- Die absolut wundervolle Icestorm Toolchain wurde als sehr schnell und skriptierbar verwendet. Ich würde vergleichbare Ergebnisse von den Anbieter Radiant Toolchain erwarten.

- Der Strom an jeder Schiene wurde mit einem Joulecope JS110 gemessen.

- Ein Spielzeugmathematikbeispiel wird bereitgestellt, bei dem zwei 8 -Bit -Zähler miteinander vervielfacht werden, um in jedem Taktzyklus ein 16 -Bit -Ergebnis zu erzielen.

Ergebnisse

Hinweis: Alle Ströme in der Tabelle befinden sich in UA.

| Beschreibung | PLL (1,219V) | Bank 0 (3.283V) | Bank 1 (3,283V) | Bank 2 (3,283V) | Kern (1,219 V) |

|---|

| Nicht konfiguriert | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| Zurücksetzen | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| Leeres Design | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| Externe 12 MHz + 28 -Bit -Zähler (32 LCs) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| Externe 12 MHz + 28*2 -Bit -Zähler (60 LCs) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| Externe 12 MHz + 28*4 -Bit -Zähler (116 LCs) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| Externe 12 MHz + 28*8 -Bit -Zähler (228 LCs) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + 24 -Bit -Zähler (28 LCs) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + 24 -Bit -Zähler (28 LCs) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + 24 -Bit -Zähler (28 LCs) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + 24 -Bit -Zähler (28 LCs) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 kHz) + 24 -Bit -Zähler (28 LCs) | 4.4 | 3.76 | 3.4 | 1.5 | 96,3 |

| Externe angehaltene Uhr (0 kHz) + 24 -Bit -Zähler (28 LCs) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + Math (No DSP) + 24 -Bit -Zähler (208 LCs) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 MHz) + Math (1 DSP) + 24 -Bit -Zähler (72 LCs) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (48 MHz Takt) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12 MHz in, 16 -MHz -Ausgang) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12 MHz in, 32 -MHz -Ausgang) | 138,9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12 MHz in, 48 MHz Ausgang) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

Beobachtungen

- Done LED -Verbindung nehmen 150UA! Trennen Sie dies für die niedrigste Leistung.

- Der RGB -Treiber nimmt ~ 280UA und setzt den Curren oder den Rgben auf Null.

- Das Halten des FPGA im Reset oder das Unkonfigurieren verbraucht mehr Strom, als wenn es mit einem tatsächlichen Niedrigstromdesign programmiert wird.

- Das Aktivieren von Pullup -Widerständen bei Eingängen hat den Stromverbrauch überhaupt nicht geändert. Dies ist wahrscheinlich darauf zurückzuführen, dass das IO nicht viel Einmischung aufnimmt. Das Berühren des IO in diesem Zustand führt dazu, dass die Macht steigt.

- Mapping Math zu einem DSP -Slice ist aus der Sicht des Power -Sicht sinnvoll, im obigen Spielzeugbeispiel sparen wir ungefähr 110UA.

- Ein minimal funktionaler FPGA (10 kHz, 24 -Bit -Zähler) kann nur 4,4 1,219 + 3,76 3,3 + 3,4 3,3 + 1,5 3,3 + 96,3*1,219 = 151UW verbrauchen. Der Stromverbrauch mit einer so niedrigen Taktrate ändert sich nicht signifikant mit zunehmender Konstruktionsgröße (ein 1536 weitem Zähler führt dazu, dass der Kernstrom um 3UA zunimmt). Dies impliziert, dass die FPGA in einem System, in dem die Uhr für längere Zeit auf 10 kHz fallen gelassen werden kann, recht gut funktioniert. Die 10 -kHz -Uhr ermöglicht es der FPGA, auf einen Interrupt zu reagieren und auf eine schnellere Uhr umzusteigen. Alternativ kann die Uhr auch auf diesem FPGA vollständig gestoppt werden, wenn sie von einer externen Uhr geliefert wird, wie durch den angehaltenen Takttest gezeigt.

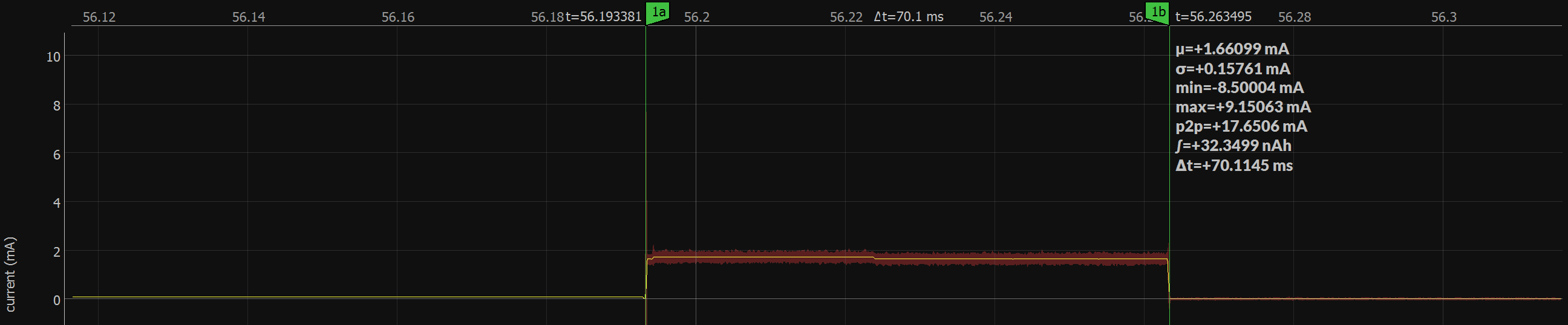

Bootup

Die FPGA -Stiefel von Flash programmiert mit einem 10 -kHz -Design mit niedrigem Strom. Die FPGA konfiguriert sich vom Flash und zeichnet die Strom- und SPI -Flash -Bank (Bank 1) wie unten gezeigt. Die gesamten Energieverbrauchszahlen sowie die Startzeiten sind wichtig für Anwendungen, die das FPGA ausführen und erfordern, dass sie nur selten für Stromeinsparungen starten. Wie in den darunter liegenden Diagrammen gezeigt, verbraucht das Booten aus dem Blitz etwa 46na Energie und dauert etwa 70 ms von Anfang bis Ende. Beachten Sie, dass dies nicht den Flash -Chip -Stromverbrauch enthält!

Ein Beispiel mit niedrigem Power -Design

OK, großartig, jetzt wo wir Messungen haben, was nützt es, wenn wir es nicht verwenden können! Beginnen wir mit einem Spielzeugdesign, damit es leicht zu verstehen ist.

Anforderungen

- Langsame Uhr ist die niedrige Geschwindigkeit von 10 kHz, die es der FPGA ermöglicht, auf externe Interrupts zu reagieren

- Wachen Sie für 50 ms auf, um alle paar Sekunden nützliche Arbeiten zu erledigen. Das "Arbeiterdesign" kann zu einer Uhr geschaltet oder bei 10 kHz läuft, falls er auf einen Interrupt reagieren muss.

- Arbeit, wenn die Wache bei 48 MHz sein sollte

Design

Offensichtlich müssen wir die Uhr auf der FPGA im Schlafen abteilen. Das Schalten des Designs zwischen 10 kHz und 48 MHz erfordert eine besondere Sorgfalt, um beim Multiplexing zwischen den beiden Uhren Störungen auf der Uhr zu vermeiden. Ein störungsfreier Clock -Mux ist eine hübsche Standardkomponente, die dies sauber macht.

Der 10 -kHz -Oszillator füttert nicht nur die GFCM, sondern auch den Zeitnehmer, der die Uhr auf das Design umschaltet, das die Arbeit erledigt. Der Zeitnehmer ist ein einfacher Zähler, der die höhere Taktrate für 50 ms pro 3.2s auswählt.

Das Design, das die Arbeit in diesem Fall erledigt, ist ein einfacher LED -Blinker und könnte durch etwas ziemlich Komplexes ersetzt werden.

Ein einfacher Testbench wurde verwendet, um das Design zu beweisen und Fehler loszuwerden ...

Ergebnisse

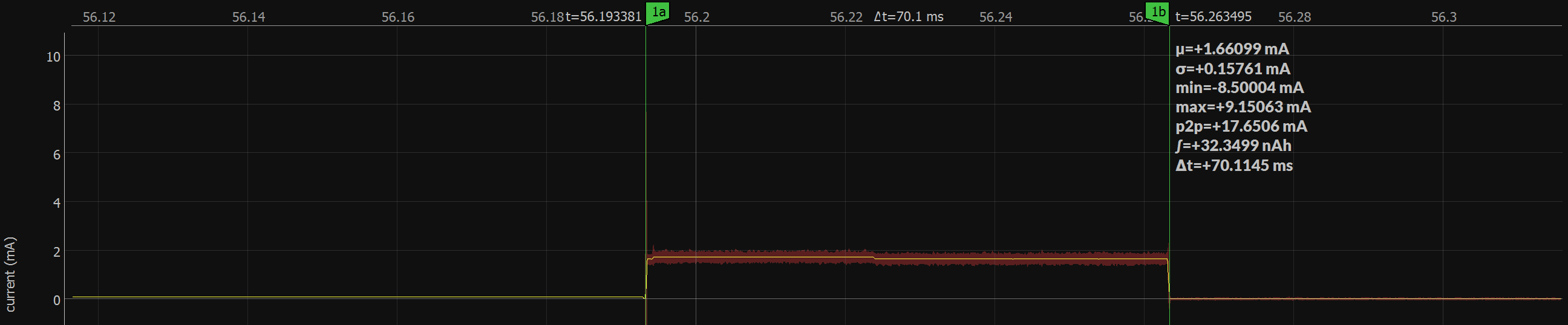

Das vollständige Design verbraucht 62 LCs, 3 SB_GB, 1 LF_OSC, 1 HF_OSC und den RGB -Treiber. Hier ist der aktuelle Verbrauch der FPGA auf der Kernscheibe. Wie Sie sehen können, scheint dies das Ziel erreicht zu haben!

- Es wird nur eine Stromversorgung der Kernschiene gemessen

- Die 135UA -Strombasis ist viel höher als der Strom in der gemessenen Tabelle. Es ist nicht klar, worauf dies ist.

- Duty Cycling funktioniert! Der Spitzenstrom beträgt 2 mA, während die Basisleistung etwa 135UA beträgt, der Durchschnitt 162UA, gemessen am Strommesser.

- Der Hochfrequenzoszillator musste deaktiviert werden, um an die 135UA -Grundlinie zu gelangen, wenn seine Ausgabe nicht ausgewählt wurde. Wenn dies nicht erfolgt, ist die Grundlinie bei etwa 630 UA signifikant höher, wenn die ausgewählte Uhr 10 kHz beträgt.

Zukünftige Arbeit

- Überprüfen Sie die Stromversorgung bei der Zuordnung von Bram vs. Registern

- Stromverbrauch von IO -Banken mit Spannung und Fahren bekannte Lasten

- Stromschwankung im Vergleich zu Temperatur

- Irgendwelche anderen Ideen?