Tujuan dari latihan ini adalah untuk memahami dari sudut pandang kekuatan, apa berbagai tradeoff di ICE40 FPGA. Ini akan memungkinkan kami untuk merancang perangkat bertenaga baterai yang menggunakan FPGA dan memperkirakan masa pakai baterai dan juga memberikan panduan waktu desain.

Catatan: Semua arus dalam tabel ada di UA.

| Keterangan | PLL (1.219V) | Bank 0 (3.283V) | Bank 1 (3.283V) | Bank 2 (3.283V) | Inti (1.219v) |

|---|---|---|---|---|---|

| Tidak dikonfigurasi | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| Mengatur ulang | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| Desain kosong | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| Eksternal 12 MHz + 28 bit counter (32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| Eksternal 12 MHz + 28*Penghitung 2 Bit (60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| Eksternal 12 MHz + 28*penghitung 4 bit (116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| Eksternal 12 MHz + 28*penghitung 8 bit (228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + penghitung 24 bit (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + penghitung 24 bit (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + penghitung 24 bit (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + penghitung 24 bit (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 kHz) + penghitung 24 bit (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| Jam terhenti eksternal (0 kHz) + penghitung 24 bit (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + Matematika (tidak ada DSP) + penghitung 24 bit (208 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 MHz) + Matematika (1 DSP) + penghitung 24 bit (72 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (jam 48 MHz) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12MHz in, output 16MHz) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12MHz in, output 32MHz) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12MHz in, output 48MHz) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

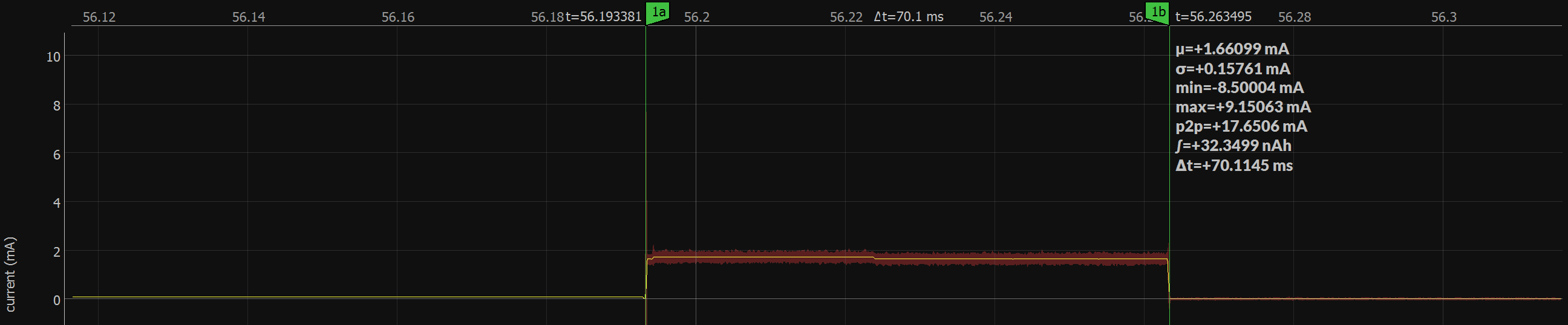

FPGA Boots dari Flash diprogram dengan desain 10kHz daya rendah. FPGA mengonfigurasi dirinya dari Flash dan menarik daya pada Core dan SPI Flash Bank (Bank 1) seperti yang ditunjukkan di bawah ini. Jumlah konsumsi energi total serta waktu boot penting untuk aplikasi yang akan mematikan FPGA dan mengharuskannya untuk mem -boot jarang untuk penghematan daya. Seperti yang ditunjukkan pada plot di bawah ini, boot dari flash mengkonsumsi sekitar 46Nah energi dan membutuhkan sekitar 70 ms dari awal hingga akhir. Perhatikan bahwa ini tidak termasuk konsumsi daya chip flash!

Oke, bagus, sekarang kita memiliki pengukuran, apa gunanya jika kita tidak bisa menggunakannya! Mari kita mulai dengan desain mainan sehingga mudah dimengerti.

Jelas, kita perlu gerbang jam di FPGA saat tertidur. Mengganti desain antara 10kHz dan 48MHz membutuhkan perawatan khusus untuk menghindari gangguan pada jam ketika multiplexing antara kedua jam. Jam Glitch Free Mux adalah komponen standar yang cukup yang melakukan ini dengan bersih.

Osilator 10kHz memberi makan tidak hanya GFCM tetapi juga pencatat waktu yang mengalihkan jam ke desain yang melakukan pekerjaan. Pencatat waktu adalah penghitung sederhana yang memilih laju clock yang lebih tinggi untuk 50ms setiap 3.2s.

Desain yang melakukan pekerjaan dalam kasus ini adalah blinker LED sederhana dan dapat digantikan oleh sesuatu yang cukup kompleks.

Testbench sederhana digunakan untuk membuktikan desain dan menyingkirkan bug ...

Desain penuh mengkonsumsi 62 LC, 3 SB_GB, 1 LF_OSC, 1 HF_OSC dan driver RGB. Inilah konsumsi FPGA saat ini pada rel power inti. Seperti yang Anda lihat, ini tampaknya telah mencapai tujuan!