ice40_power

1.0.0

這項練習的目的是從權力的角度來了解ICE40 FPGA中的各種權衡。這將使我們能夠設計使用FPGA並估算電池壽命並提供設計時間指導的電池供電設備。

注意:表中的所有電流都在UA中。

| 描述 | PLL(1.219V) | 銀行0(3.283V) | 銀行1(3.283V) | 銀行2(3.283V) | 核心(1.219V) |

|---|---|---|---|---|---|

| 未配置 | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| 重置 | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| 空白設計 | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| 外部12 MHz + 28位計數器(32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| 外部12 MHz + 28*2位計數器(60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| 外部12 MHz + 28*4位計數器(116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| 外部12 MHz + 28*8位計數器(228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC(48 MHz) + 24位計數器(28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC(24 MHz) + 24位計數器(28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC(12 MHz) + 24位計數器(28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC(6 MHz) + 24位計數器(28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC(10 kHz) + 24位計數器(28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| 外部停止時鐘(0 kHz) + 24位計數器(28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC(12 MHz) +數學(無DSP) + 24位計數器(208 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC(12 MHz) +數學(1 DSP) + 24位計數器(72 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB(48 MHz時鐘) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL(12MHz,16MHz輸出) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL(12MHz,32MHz輸出) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL(12MHz,48MHz輸出) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

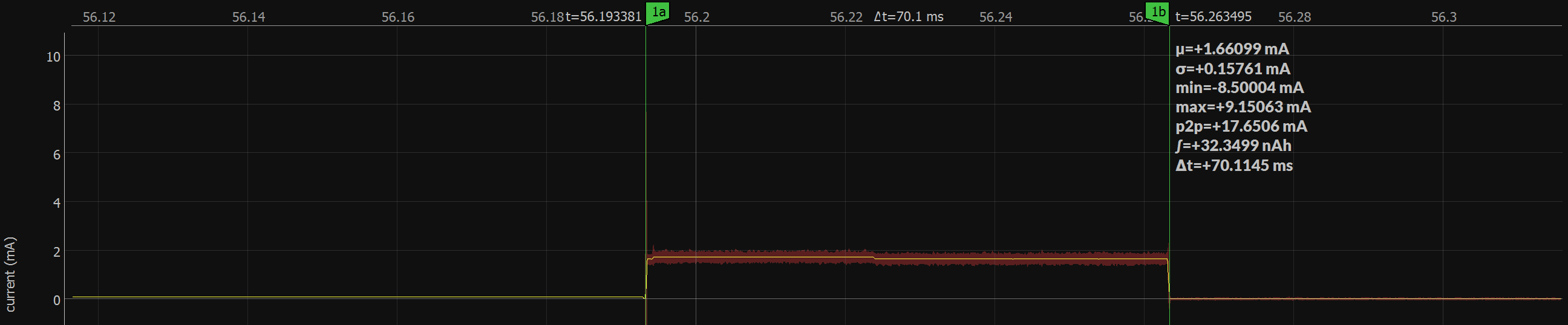

Flash的FPGA靴子通過低功率10kHz設計編程。 FPGA從Flash配置自身,並在Core和SPI Flash Bask(Bank 1)上汲取電源,如下所示。總能耗數量和啟動時間對於可以關閉FPGA並要求其啟動以節省的應用非常重要。如下圖所示,從閃光燈啟動的啟動消耗了約46nah的能量,並且從頭到尾都需要大約70毫秒。請注意,這不包括Flash芯片功耗!

好的,太好了,現在我們有了測量,如果我們不能使用它,那有什麼好處!讓我們從玩具設計開始,以便易於理解。

顯然,當它睡著時,我們需要在FPGA上登機。切換10kHz和48MHz之間的設計需要特殊護理,以避免在兩個時鐘之間多重時鐘上的故障。無故障時鐘MUX是一個非常標準的組件,可以乾淨地進行操作。

10kHz振盪器不僅為GFCM提供了饋送,還為將時鐘切換到完成工作的設計的計時器。計時器是一個簡單的計數器,每3.2s選擇較高的時鐘速率。

在這種情況下進行工作的設計是一個簡單的LED眨眼,可以用相當複雜的東西代替。

一個簡單的測試板用於證明設計並擺脫錯誤...

完整的設計消耗了62個LC,3 SB_GB,1 LF_OSC,1 HF_OSC和RGB驅動程序。這是FPGA在核心電源導軌上的當前消耗。如您所見,這似乎已經實現了目標!