الهدف من هذا التمرين هو فهم من وجهة نظر السلطة ، وما هي المقايضة المختلفة في ICE40 FPGA. هذا من شأنه أن يسمح لنا بتصميم الأجهزة التي تعمل بالبطارية التي تستخدم FPGA وتقدير عمر البطارية وكذلك توفير إرشادات وقت التصميم.

ملاحظة: جميع التيارات في الجدول موجودة في UA.

| وصف | PLL (1.219V) | البنك 0 (3.283V) | البنك 1 (3.283V) | البنك 2 (3.283V) | جوهر (1.219V) |

|---|---|---|---|---|---|

| غير متكافئ | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| إعادة ضبط | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| تصميم فارغ | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| خارجي 12 ميغاهيرتز + 28 بت (32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| خارجي 12 ميغاهيرتز + 28*2 بت (60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| خارجي 12 ميغاهيرتز + 28*4 بت (116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| خارجي 12 ميغاهيرتز + 28*8 بت (228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + 24 بت (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + 24 بت (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + 24 بت (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + 24 بت (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 كيلو هرتز) + 24 بت (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| ساعة متوقفة خارجية (0 كيلو هرتز) + 24 بت (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + MATH (NO DSP) + 24 بت (208 LC'S) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 MHz) + MATH (1 DSP) + 24 بت (72 LC'S) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (48 MHz على مدار الساعة) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12 ميجا هرتز في ، إخراج 16 ميجا هرتز) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12 ميجا هرتز في ، 32 ميجا هرتز الإخراج) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12 ميجا هرتز في ، إخراج 48 ميجا هرتز) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

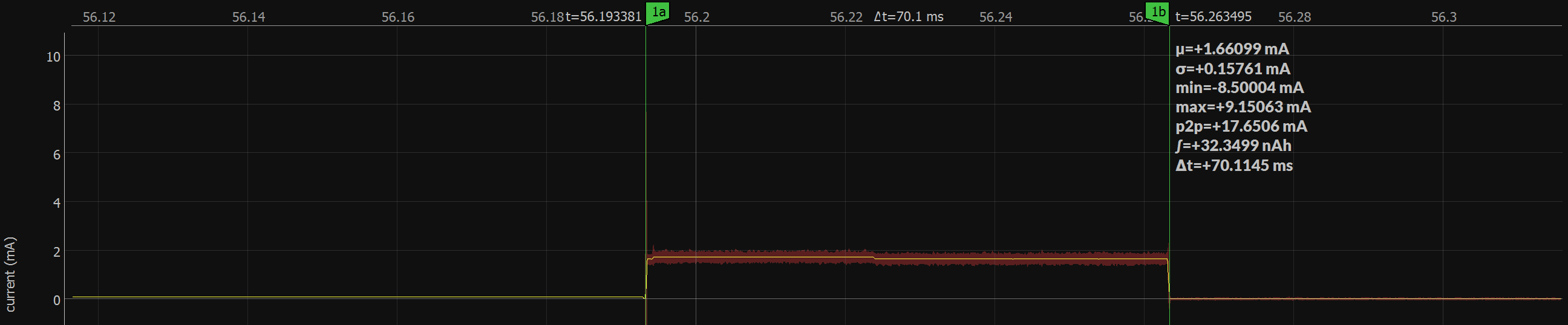

أحذية FPGA من فلاش مبرمجة بتصميم منخفض طاقة 10 كيلو هرتز. يقوم FPGA بتكوين نفسه من Flash ويسحب الطاقة على Core و SPI Flash Bank (Bank 1) كما هو موضح أدناه. تعد إجمالي أرقام استهلاك الطاقة بالإضافة إلى أوقات التمهيد مهمة للتطبيقات التي ستعمل على تشغيل FPGA وتتطلب من ذلك التمهيد بشكل غير متكرر لتوفير الطاقة. كما هو موضح في المؤامرات أدناه ، يستهلك التمهيد من الفلاش حوالي 46NAH من الطاقة ويستغرق حوالي 70 مللي ثانية من البداية إلى النهاية. لاحظ أن هذا لا يشمل استهلاك طاقة شريحة الفلاش!

حسنًا ، رائع ، الآن لدينا قياسات ، ما هو جيد إذا لم نتمكن من استخدامه! لنبدأ بتصميم لعبة بحيث يسهل فهمه.

من الواضح أننا نحتاج إلى بوابة الساعة على FPGA عند النوم. يتطلب تبديل التصميم بين 10 كيلو هرتز و 48 ميجا هرتز رعاية خاصة لتجنب مواطن الخلل على مدار الساعة عند تعدد الإرسال بين الساعتين. يعد Mux الخالي من خلل مكونًا قياسيًا جدًا يقوم بذلك بشكل نظيف.

لا يتغذى مذبذب 10KHz ليس فقط GFCM ولكن أيضًا على حارس الوقت الذي يحول الساعة إلى التصميم الذي يقوم بالعمل. حارس الوقت هو عداد بسيط يختار معدل الساعة الأعلى لـ 50 مللي ثانية كل 3.2 ثانية.

التصميم الذي يقوم بالعمل في هذه الحالة هو وميض LED بسيط ويمكن استبداله بشيء معقد للغاية.

تم استخدام مجموعة Testbench البسيطة لإثبات التصميم والتخلص من الأخطاء ...

يستهلك التصميم الكامل 62 LC's و 3 SB_GB و 1 LF_OSC و 1 HF_OSC وبرنامج RGB. هيريس الاستهلاك الحالي لـ FPGA على سكة الطاقة الأساسية. كما ترون ، يبدو أن هذا حقق الهدف!