Teste de energia ICE40

O objetivo deste exercício é entender de um ponto de vista de poder, quais são as várias compensações no FPGA ICE40. Isso nos permitiria projetar dispositivos alimentados por bateria que usam o FPGA e estimariam a duração da bateria e também fornecem orientações de tempo de design.

Configurar

- O hardware usado é a placa de fuga do ICE40 da Lattice. Esta placa foi escolhida ao quebrar todos os trilhos de força do FPGA.

- Eu usei o arquivo PCF do upduino como idêntico.

- A cadeia de ferramentas ICESTORM absolutamente maravilhosa foi usada como muito rápida e scriptável. Eu esperaria resultados comparáveis da cadeia de ferramentas radiantes dos fornecedores.

- A corrente em cada trilho foi medida usando um joulescope JS110.

- Um exemplo de matemática de brinquedos é fornecido onde dois contadores de 8 bits são multiplicados juntos para obter um resultado de 16 bits em cada ciclo de relógio.

Resultados

Nota: Todas as correntes da tabela estão em UA.

| Descrição | PLL (1.219V) | Banco 0 (3.283V) | Banco 1 (3.283V) | Banco 2 (3.283V) | Núcleo (1.219V) |

|---|

| Não configurado | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| Reiniciar | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| Projeto em branco | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| Counter externo de 12 MHz + 28 bits (32 LC's) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| Counter externo de 12 MHz + 28*2 bits (60 LC's) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| Counter externo de 12 MHz + 28*4 bits (116 LC's) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| Counter externo de 12 MHz + 28*8 bits (228 LC's) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + contador de 24 bits (28 LC's) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + contador de 24 bits (28 LC's) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + contador de 24 bits (28 LC's) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + contador de 24 bits (28 LC's) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 kHz) + contador de 24 bits (28 LC's) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| Relógio interno externo (0 kHz) + contador de 24 bits (28 LC's) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + matemática (sem DSP) + contador de 24 bits (208 LC's) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 MHz) + matemática (1 DSP) + contador de 24 bits (72 LC's) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (relógio de 48 MHz) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12MHz em saída de 16MHz) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12MHz em saída de 32MHz) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12MHz em saída de 48MHz) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

Observações

- Conexão LED feita Tome 150ua! Desconecte isso quanto à menor potência.

- O driver RGB leva ~ 280ua, definindo o Curren ou o rgbleden para zero cair essa corrente completamente.

- Segurar o FPGA em redefinição ou deixá -lo não configurado consome mais energia do que se estiver programado com um design real de baixa energia.

- A possibilidade de resistores de pullups nas entradas não alterou o consumo de energia. Provavelmente, isso se deve ao IO não obter muita interferência. Tocar o IO nesse estado faz com que o poder suba.

- O mapeamento de matemática para uma fatia do DSP faz sentido do ponto de vista do poder, no exemplo de brinquedo acima, economizamos cerca de 110ua.

- Um FPGA minimamente funcional (10kHz, contador de 24 bits) pode consumir apenas 4,4 1,219 + 3,76 3,3 + 3,4 3,3 + 1,5 3,3 + 96,3*1,219 = 151UW. O consumo de energia com uma taxa de relógio tão baixa não muda significativamente com o aumento do tamanho do projeto (um contador de 1536 largura faz com que a corrente do núcleo aumente em 3ua). Isso implica que o FPGA funcionará muito bem se usado em um sistema onde o relógio pode ser retirado para 10kHz por longos períodos de tempo. O relógio de 10kHz permite que o FPGA responda a uma interrupção e também mude para um relógio mais rápido. Como alternativa, o relógio pode ser completamente interrompido nesse FPGA, se for fornecido por um relógio externo, como mostrado pelo teste de relógio interrompido.

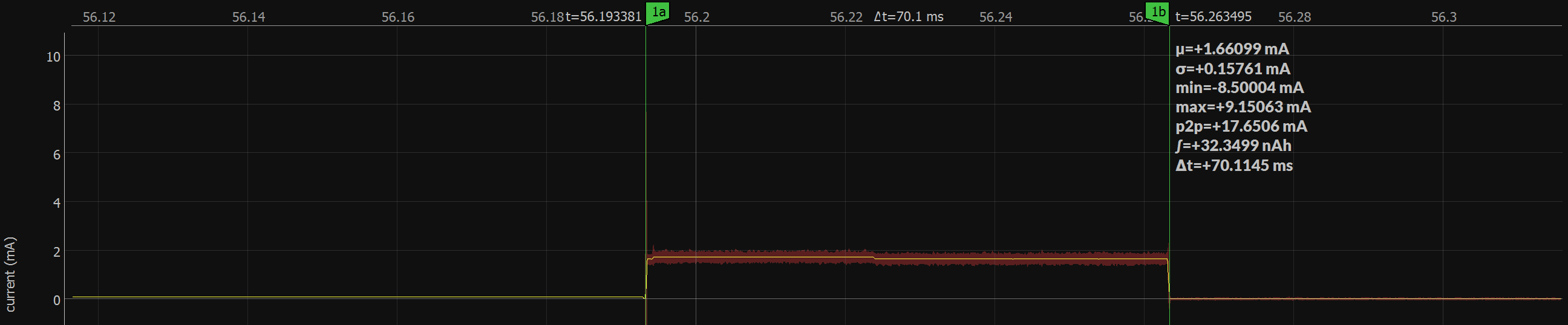

Bootup

As botas FPGA do flash programadas com design de 10kHz de baixa potência. O FPGA se configura do Flash e consome energia no núcleo e o SPI Flash Bank (Banco 1), como mostrado abaixo. Os números totais de consumo de energia e os tempos de inicialização são importantes para aplicativos que desligam o FPGA e exigem que ele inicialize com pouca frequência para economizar energia. Conforme mostrado nas parcelas abaixo, a inicialização do flash consome cerca de 46nah de energia e leva cerca de 70ms do início ao fim. Observe que isso não inclui o consumo de energia do flash chip!

Um amostra de design de baixa potência

Ok, ótimo, agora que temos medições, de que é o bem se não podemos usá -lo! Vamos começar com um design de brinquedos para que seja fácil de entender.

Requisitos

- O relógio lento deve ser a baixa velocidade de 10kHz que permite que o FPGA responda a interrupções externas

- Acorde para 50ms para fazer algum trabalho útil a cada poucos segundos, o "design do trabalhador" pode ser fechado com o relógio ou continuado em funcionamento a 10kHz, caso precise responder a uma interrupção.

- Trabalho quando acordado deve estar em 48 MHz relógio

Projeto

Claramente, precisamos levar o relógio no FPGA quando está dormindo. Alternar o design entre 10kHz e 48MHz requer cuidados especiais para evitar falhas no relógio ao multiplexar entre os dois relógios. Um relógio sem falha MUX é um componente bastante padrão que faz isso de maneira limpa.

O oscilador de 10kHz alimenta não apenas o GFCM, mas também o cronometrista que muda o relógio para o design que faz o trabalho. O cronometrista é um contador simples que seleciona a taxa de relógio mais alta para 50ms a cada 3,2s.

O design que faz o trabalho neste caso é um piscar de LED simples e pode ser substituído por algo bastante complexo.

Um teste simples foi usado para provar o design e se livrar dos insetos ...

Resultados

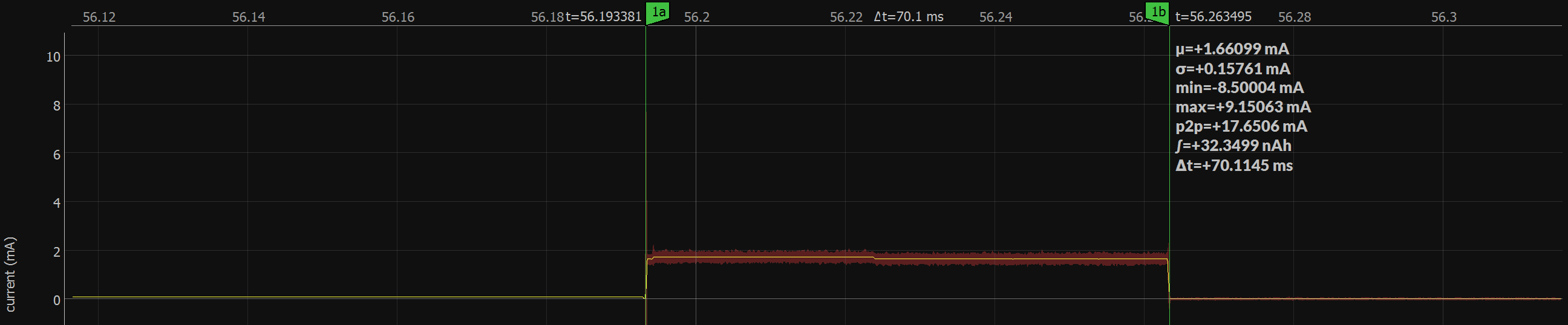

O design completo consome 62 LC's, 3 sb_gb, 1 lf_osc, 1 hf_osc e o driver RGB. Aqui está o consumo atual do FPGA no trilho de energia principal. Como você pode ver, isso parece ter atingido o objetivo!

- Somente a energia no trilho do núcleo é medida

- A linha de base da corrente 135ua é muito maior que a corrente da tabela medida. Não está claro o que isso é devido.

- O ciclismo de serviço funciona! A corrente de pico é 2MA, enquanto a potência da linha de base é de cerca de 135ua, a média é de 162ua, conforme medido pelo medidor atual.

- O oscilador de alta frequência teve que ser desativado para chegar à linha de base 135ua quando sua saída não foi selecionada. Se isso não for feito, a linha de base será significativamente maior em cerca de 630ua quando o relógio selecionado é de 10kHz.

Trabalho futuro

- Confira a energia ao mapear para Bram vs. registros

- Consumo de energia de bancos de IO com tensão e impulsionando cargas conhecidas

- Variação atual vs. temperatura

- Alguma outra idéia?