이 연습의 목표는 파워 관점에서, ICE40 FPGA의 다양한 트레이드 오프가 무엇인지 이해하는 것입니다. 이를 통해 FPGA를 사용하는 배터리 구동 장치를 설계하고 배터리 수명을 추정하고 설계 시간 안내를 제공 할 수 있습니다.

참고 : 테이블의 모든 전류는 UA입니다.

| 설명 | PLL (1.219V) | 은행 0 (3.283V) | 은행 1 (3.283V) | 은행 2 (3.283V) | 코어 (1.219V) |

|---|---|---|---|---|---|

| 구성되지 않은 | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| 다시 놓기 | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| 빈 디자인 | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| 외부 12MHz + 28 비트 카운터 (32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| 외부 12 MHz + 28*2 비트 카운터 (60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| 외부 12 MHz + 28*4 비트 카운터 (116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| 외부 12 MHz + 28*8 비트 카운터 (228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + 24 비트 카운터 (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + 24 비트 카운터 (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + 24 비트 카운터 (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + 24 비트 카운터 (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 kHz) + 24 비트 카운터 (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| 외부 중단 시계 (0 kHz) + 24 비트 카운터 (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + 수학 (DSP 없음) + 24 비트 카운터 (208 LC 's) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| hfosc (12 mhz) + 수학 (1 dsp) + 24 비트 카운터 (72 LC 's) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (48MHz 클럭) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12MHz 인치, 16MHz 출력) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12MHz 인치, 32MHz 출력) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12MHz 인치, 48MHz 출력) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

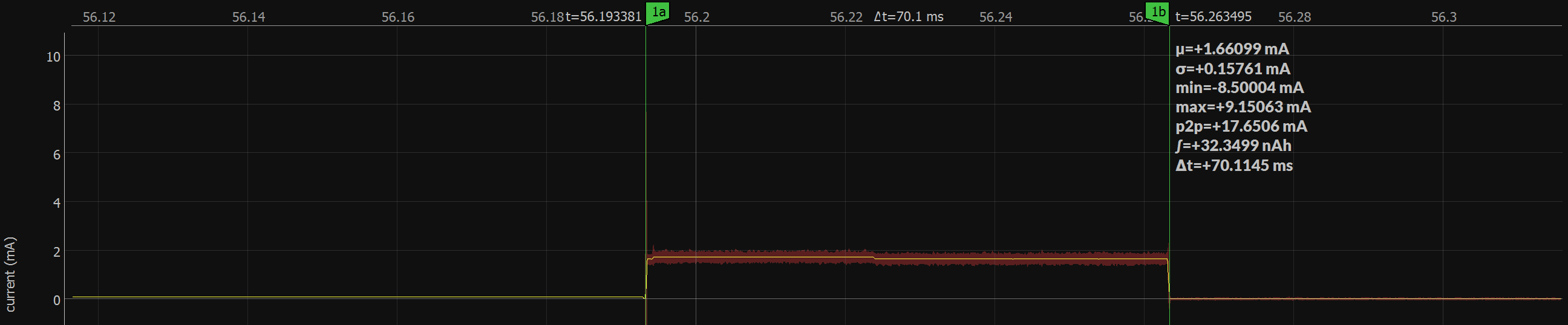

Flash의 FPGA 부츠는 저전력 10kHz 설계로 프로그래밍되었습니다. FPGA는 플래시에서 자체적으로 구성되고 아래와 같이 코어 및 SPI 플래시 뱅크 (은행 1)에 전원을 뽑습니다. 부팅 시간뿐만 아니라 총 에너지 소비량은 FPGA에 전원을 끄고 전력 절약을 위해 드물게 부팅 해야하는 응용 프로그램에 중요합니다. 아래 플롯에서 볼 수 있듯이 플래시에서 부팅하면 약 46nah의 에너지가 소비되며 처음부터 끝까지 약 70ms가 걸립니다. 이것은 플래시 칩 전력 소비가 포함되어 있지 않습니다!

좋아, 좋아, 이제 우리는 측정 값을 가지고 있으므로, 우리가 그것을 사용할 수 없다면 얼마나 좋은 일입니까! 장난감 디자인으로 시작하여 이해하기 쉽습니다.

분명히, 우리는 잠들 때 FPGA에서 시계를 게이트해야합니다. 10kHz와 48MHz 사이의 설계를 전환하려면 두 시계 사이를 멀티플렉싱 할 때 시계의 결함을 피하기 위해 특별한주의가 필요합니다. 글리치 프리 클럭 MUX는이를 깨끗하게 수행하는 꽤 표준 구성 요소입니다.

10kHz 발진기는 GFCM뿐만 아니라 시계를 작업하는 디자인으로 전환하는 타임 키퍼도 공급합니다. 타임 키퍼는 3.2 초마다 50ms의 더 높은 시계 속도를 선택하는 간단한 카운터입니다.

이 경우 작업을 수행하는 디자인은 간단한 LED 깜박임이며 상당히 복잡한 것으로 대체 될 수 있습니다.

간단한 테스트 벤치는 설계를 증명하고 버그를 제거하는 데 사용되었습니다 ...

풀 디자인은 62 LC, 3 SB_GB, 1 LF_OSC, 1 HF_OSC 및 RGB 드라이버를 소비합니다. 그녀는 코어 파워 레일에서 FPGA의 현재 소비를 제공합니다. 보시다시피, 이것은 목표를 달성 한 것 같습니다!