この演習の目標は、Powerの観点から、ICE40 FPGAのさまざまなトレードオフが何であるかを理解することです。これにより、FPGAを使用するバッテリー駆動のデバイスを設計し、バッテリー寿命を推定し、設計時間ガイダンスも提供できます。

注:テーブル内のすべての電流はUAにあります。

| 説明 | PLL(1.219V) | 銀行0(3.283V) | 銀行1(3.283V) | 銀行2(3.283V) | コア(1.219V) |

|---|---|---|---|---|---|

| 構成されていない | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| リセット | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| 空白のデザイン | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| 外部12 MHz + 28ビットカウンター(32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| 外部12 MHz + 28*2ビットカウンター(60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| 外部12 MHz + 28*4ビットカウンター(116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| 外部12 MHz + 28*8ビットカウンター(228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC(48 MHz) + 24ビットカウンター(28 lc's) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC(24 MHz) + 24ビットカウンター(28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC(12 MHz) + 24ビットカウンター(28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC(6 MHz) + 24ビットカウンター(28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC(10 kHz) + 24ビットカウンター(28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| 外部停止時計(0 kHz) + 24ビットカウンター(28 lc's) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC(12 MHz) + Math(DSPなし) + 24ビットカウンター(208 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC(12 MHz) + Math(1 DSP) + 24ビットカウンター(72 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB(48 MHzクロック) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL(12MHz IN、16MHz出力) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL(12MHz in、32MHz出力) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL(12MHz IN、48MHz出力) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

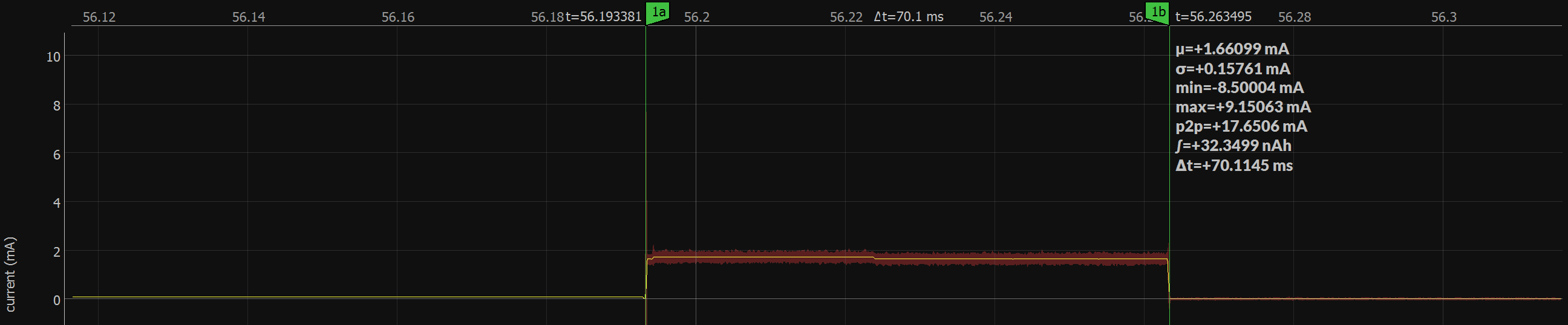

低電力10kHzデザインでプログラムされたフラッシュのFPGAブーツ。 FPGAは、Flashから自分自身を構成し、以下に示すようにコアとSPIフラッシュバンク(銀行1)に電力を供給します。総エネルギー消費数とブート時間は、FPGAの電力を供給し、電力節約のためにまれに起動する必要があるアプリケーションにとって重要です。以下のプロットに示すように、フラッシュからの起動は約46nhのエネルギーを消費し、最初から最後まで約70ミリ秒かかります。これには、フラッシュチップ電源消費が含まれていないことに注意してください!

わかりました、素晴らしい、今、私たちは測定値を持っているので、それを使うことができないなら、それは何が良いでしょう!おもちゃのデザインから始めましょう。

明らかに、眠っているときにFPGAの時計をゲートする必要があります。 10kHzと48MHzの間に設計を切り替えるには、2つのクロック間を多重化するときに時計のグリッチを避けるために特別な注意が必要です。グリッチフリークロックMuxは、これをきれいに行う非常に標準的なコンポーネントです。

10kHz発振器は、GFCMだけでなく、クロックを作業を行うデザインに切り替えるタイムキーパーにも供給されます。タイムキーパーは、3.2秒ごとに50msのクロックレートが高いことを選択する単純なカウンターです。

この場合、作業を行うデザインは、単純なLEDブリンカーであり、非常に複雑なものに置き換えることができます。

デザインを証明し、バグを取り除くために、簡単なテストベンチが使用されました...

フルデザインは、62 LC、3 SB_GB、1 LF_OSC、1 HF_OSC、およびRGBドライバーを消費します。 Core Power RailでのFPGAの現在の消費量を示しています。ご覧のとおり、これは目標を達成したようです!