Цель этого упражнения состоит в том, чтобы понять с точки зрения власти, каковы различные компромисс в FPGA ICE40. Это позволило бы нам разработать устройства с батарейным питанием, которые используют FPGA и оценивают время автономной работы, а также обеспечивают руководство по дизайну.

Примечание: все токи в таблице находятся в UA.

| Описание | PLL (1,219 В) | Банк 0 (3,283 В) | Банк 1 (3,283 В) | Банк 2 (3,283 В) | Ядро (1,219 В) |

|---|---|---|---|---|---|

| Неконфигурировано | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| Перезагрузить | 4.4 | 1.29 | 82,9 | 1.5 | 188.3 |

| Пустой дизайн | 4.1 | 1.3 | 3.4 | 1.5 | 85,6 |

| Внешний 12 МГц + 28 -битный счетчик (32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| Внешнее 12 МГц + 28*2 -битное счетчик (60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| Внешний 12 МГц + 28*4 -битный счетчик (116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624,2 |

| Внешний 12 МГц + 28*8 -битный счетчик (228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 МГц) + 24 -битный счетчик (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 МГц) + 24 -битный счетчик (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 МГц) + 24 -битный счетчик (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 МГц) + 24 -битный счетчик (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 кГц) + 24 -битный счетчик (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| Внешние остановленные часы (0 кГц) + 24 -битный счетчик (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 МГц) + математика (без DSP) + 24 -битный счетчик (208 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 МГц) + математика (1 DSP) + 24 -битный счетчик (72 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (часы 48 МГц) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12 МГц в, 16 МГц вывод) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12 МГц в, 32 МГц вывод) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12 МГц в, 48 МГц вывод) | 103,6 | 1.29 | 3.42 | 1.4 | 2573 |

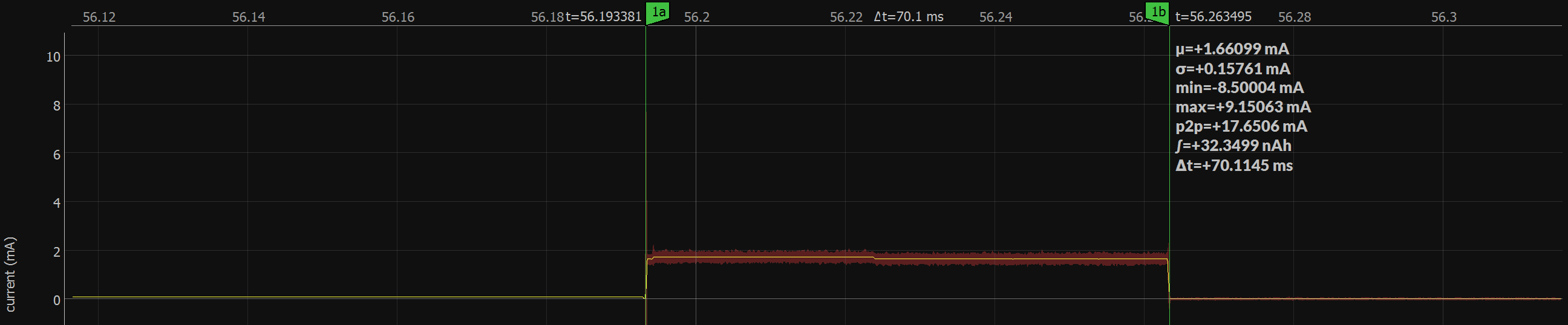

Сапоги FPGA от Flash, запрограммированные с низкой мощностью 10 кГц. FPGA конфигурирует себя из Flash и рисует мощность на банк Flash Core и SPI (банк 1), как показано ниже. Общие числа потребления энергии, а также время загрузки важны для приложений, которые будут питать FPGA и требуют того, чтобы они нечасто загружались для экономии питания. Как показано на сюжетах ниже, загрузка из вспышки потребляет около 46NAH энергии и занимает около 70 мс от начала до конца. Обратите внимание, что это не включает в себя энергопотребление флэш -чипа!

Хорошо, отлично, теперь, когда у нас есть измерения, что хорошо, если мы не можем его использовать! Давайте начнем с дизайна игрушек, так что его легко понять.

Очевидно, что нам нужно прижать часы на FPGA, когда он спят. Переключение конструкции между 10 кГц до 48 МГц требует особой помощи, чтобы избежать глюков на часах при мультиплексировании между двумя часами. Mux Free Free Clock - это довольно стандартный компонент, который делает это чисто.

Осциллятор 10 кГц питает не только GFCM, но и хронометрист, который переключает часы на дизайн, который выполняет работу. Временный хронометрист - это простой счетчик, который выбирает более высокую тактовую частоту в течение 50 мс каждые 3,2.

Дизайн, который выполняет работу в этом случае, является простым светодиодным миганом и может быть заменен чем -то довольно сложным.

Простой тестовый запас использовался, чтобы доказать дизайн и избавиться от ошибок ...

Полный дизайн потребляет 62 LC, 3 SB_GB, 1 LF_OSC, 1 HF_OSC и драйвер RGB. Вот текущее потребление FPGA на основной силовой рельсе. Как видите, это, кажется, достигло цели!