เป้าหมายของแบบฝึกหัดนี้คือการเข้าใจจากมุมมองของพลังสิ่งที่การแลกเปลี่ยนต่าง ๆ ใน ICE40 FPGA คืออะไร สิ่งนี้จะช่วยให้เราสามารถออกแบบอุปกรณ์ที่ใช้พลังงานจากแบตเตอรี่ที่ใช้ FPGA และประเมินอายุการใช้งานแบตเตอรี่และยังให้คำแนะนำเวลาในการออกแบบ

หมายเหตุ: กระแสทั้งหมดในตารางอยู่ใน UA

| คำอธิบาย | PLL (1.219V) | ธนาคาร 0 (3.283V) | ธนาคาร 1 (3.283V) | ธนาคาร 2 (3.283V) | CORE (1.219V) |

|---|---|---|---|---|---|

| ไม่ได้กำหนดค่า | 4.4 | 1.29 | ค.ศ. 1552 | 1.5 | 381.6 |

| รีเซ็ต | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| การออกแบบที่ว่างเปล่า | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| ตัวนับภายนอก 12 MHz + 28 บิต (32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| ภายนอก 12 MHz + 28*2 บิตตัวนับ (60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| ภายนอก 12 MHz + 28*4 บิตตัวนับ (116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| ภายนอก 12 MHz + 28*8 บิตตัวนับ (228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + 24 บิตตัวนับ (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + 24 บิตตัวนับ (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + 24 บิตตัวนับ (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + 24 บิตตัวนับ (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 kHz) + 24 บิตตัวนับ (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| นาฬิกาหยุดภายนอก (0 kHz) + 24 บิตตัวนับ (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + Math (ไม่มี DSP) + 24 บิตตัวนับ (208 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 MHz) + Math (1 DSP) + 24 บิตตัวนับ (72 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (นาฬิกา 48 MHz) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12MHz ใน, เอาต์พุต 16MHz) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12MHz ใน, เอาต์พุต 32MHz) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12MHz ใน, 48MHz output) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

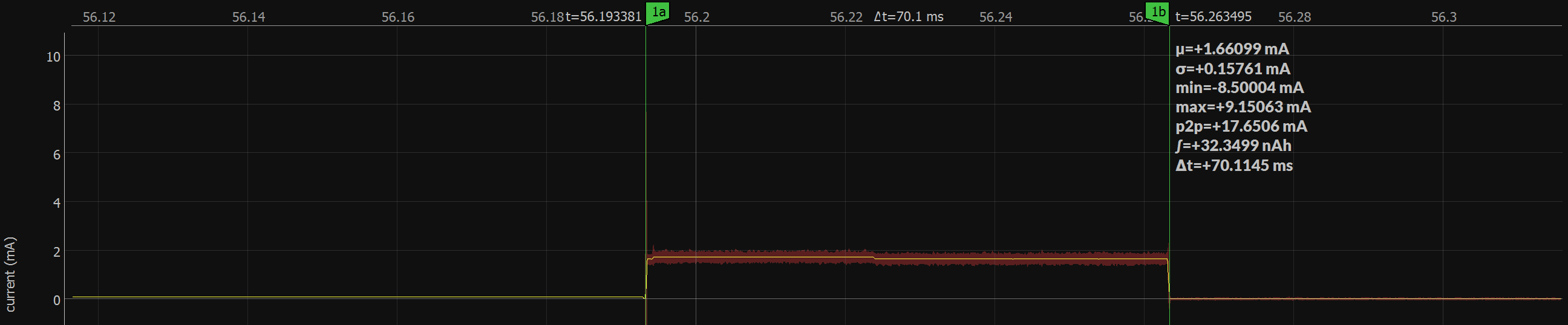

รองเท้าบูท FPGA จากแฟลชที่ตั้งโปรแกรมด้วยการออกแบบพลังงานต่ำ 10kHz FPGA กำหนดค่าตัวเองจากแฟลชและดึงพลังงานบน Core และ SPI Flash Bank (ธนาคาร 1) ดังที่แสดงด้านล่าง จำนวนการใช้พลังงานทั้งหมดรวมถึงเวลาบูตเป็นสิ่งสำคัญสำหรับแอปพลิเคชันที่จะปิด FPGA และต้องการให้บูตไม่บ่อยนักเพื่อประหยัดพลังงาน ดังที่แสดงในพล็อตด้านล่างการบูทจากแฟลชใช้พลังงานประมาณ 46NAH และใช้เวลาประมาณ 70ms ตั้งแต่ต้นจนจบ โปรดทราบว่าสิ่งนี้ไม่รวมการใช้พลังงานชิปแฟลช!

ตกลงเยี่ยมมากตอนนี้เรามีการวัดแล้วมันดีแค่ไหนถ้าเราใช้ไม่ได้! เริ่มต้นด้วยการออกแบบของเล่นเพื่อให้เข้าใจง่าย

เห็นได้ชัดว่าเราต้องทำประตูนาฬิกาบน FPGA เมื่อนอนหลับ การสลับการออกแบบระหว่าง 10kHz และ 48MHz ต้องใช้ความระมัดระวังเป็นพิเศษเพื่อหลีกเลี่ยงข้อบกพร่องบนนาฬิกาเมื่อมัลติเพล็กซ์ระหว่างสองนาฬิกา MUX นาฬิกาฟรีที่ผิดพลาดเป็นส่วนประกอบมาตรฐานที่ทำสิ่งนี้ได้อย่างหมดจด

10kHz oscillator ไม่เพียง แต่ฟีด GFCM เท่านั้น แต่ยังรวมถึงผู้จับเวลาที่สลับนาฬิกาไปสู่การออกแบบที่ทำงาน Timekeeper เป็นตัวนับง่าย ๆ ที่เลือกอัตรานาฬิกาที่สูงขึ้นสำหรับ 50ms ทุก 3.2s

การออกแบบที่ทำงานในกรณีนี้เป็นไฟกะพริบง่าย ๆ และสามารถแทนที่ด้วยสิ่งที่ค่อนข้างซับซ้อน

testbench ง่าย ๆ ถูกใช้เพื่อพิสูจน์การออกแบบและกำจัดข้อบกพร่อง ...

การออกแบบเต็มรูปแบบใช้ 62 LC, 3 SB_GB, 1 LF_OSC, 1 HF_OSC และไดรเวอร์ RGB นี่คือการบริโภคปัจจุบันของ FPGA บนรางพลังงานหลัก อย่างที่คุณเห็นดูเหมือนว่าจะบรรลุเป้าหมาย!