Test de puissance ICE40

Le but de cet exercice est de comprendre d'un point de vue de puissance, quels sont les différents compromis dans le FPGA ICE40. Cela nous permettrait de concevoir des dispositifs alimentés par batterie qui utilisent le FPGA et d'estimer la durée de vie de la batterie et de fournir des conseils de temps de conception.

Installation

- Le matériel utilisé est la planche de rupture ICE40 du réseau. Cette planche a été choisie car elle éclate tous les rails de puissance du FPGA.

- J'ai utilisé le fichier PCF à partir du Upduino comme son identique.

- La chaîne d'outils Icestorm absolument merveilleuse a été utilisée comme très rapide et scriptable. Je m'attendrais à des résultats comparables de la chaîne d'outils radiante des fournisseurs.

- Le courant sur chaque rail a été mesuré à l'aide d'un Joulescope JS110.

- Un exemple de mathématiques jouets est fourni lorsque deux compteurs à 8 bits sont multipliés ensemble pour obtenir un résultat 16 bits sur chaque cycle d'horloge.

Résultats

Remarque: Tous les courants du tableau sont dans UA.

| Description | PLL (1.219V) | Banque 0 (3.283v) | Banque 1 (3.283v) | Banque 2 (3.283v) | Noyau (1.219v) |

|---|

| Non configuré | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| Réinitialiser | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| Conception vide | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| Compteur externe de 12 MHz + 28 bits (32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| Compteur externe 12 MHz + 28 * 2 bits (60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| Compteur externe 12 MHz + 28 * 4 bits (116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| Compteur externe 12 MHz + 28 * 8 bits (228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + compteur 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + compteur 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + compteur 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + compteur 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 kHz) + compteur 24 bits (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| Horloge interrompue externe (0 kHz) + compteur 24 bits (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + mathématiques (pas de DSP) + compteur 24 bits (208 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 MHz) + mathématiques (1 DSP) + compteur 24 bits (72 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RVB (horloge 48 MHz) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12 MHz dans, sortie 16 MHz) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12 MHz dans, sortie 32 MHz) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12 MHz dans, sortie 48 MHz) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

Observations

- Connexion LED fait Take 150UA! Débranchez-le pour la plus faible puissance.

- Le conducteur RVB prend ~ 280UA, en réglant le curren ou le RGBLEDEN à zéro laisse entièrement abandonner ce courant.

- Tenir le FPGA en réinitialisation ou le laisser non configuré consomme plus de puissance que si son programmation avec une conception réelle de faible puissance.

- L'activation des résistances de traction sur les entrées n'a pas du tout modifié la consommation d'énergie. Cela est probablement dû au fait que l'IO ne ramasse pas beaucoup d'interférence. Le toucher de l'OI dans cet état provoque une augmentation du pouvoir.

- La cartographie des mathématiques à une tranche de DSP est logique du point de vue de puissance, dans l'exemple de jouets ci-dessus, nous économisons environ 110UA.

- Un FPGA mini-fonctionnel (10 kHz, compteur 24 bits) peut consommer aussi peu que 4,4 1,219 + 3,76 3,3 + 3,4 3,3 + 1,5 3,3 + 96,3 * 1,219 = 151UW. La consommation d'énergie avec une fréquence d'horloge aussi faible ne change pas de manière significative avec l'augmentation de la taille de la conception (un compteur large de 1536 provoque une augmentation du courant central de 3UA). Cela implique que le FPGA fonctionnera assez bien s'il est utilisé dans un système où l'horloge peut être déposée à 10 kHz pendant de longues périodes. L'horloge de 10 kHz permet au FPGA de répondre à une interruption et également de passer à une horloge plus rapide. Alternativement, l'horloge peut également être complètement arrêtée sur ce FPGA si elle est fournie par une horloge externe, comme le montre le test d'horloge interrompu.

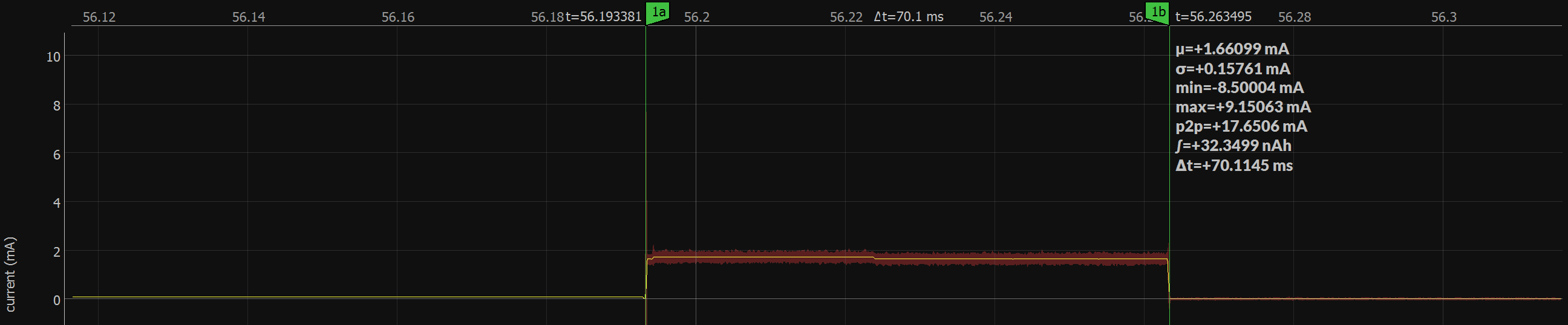

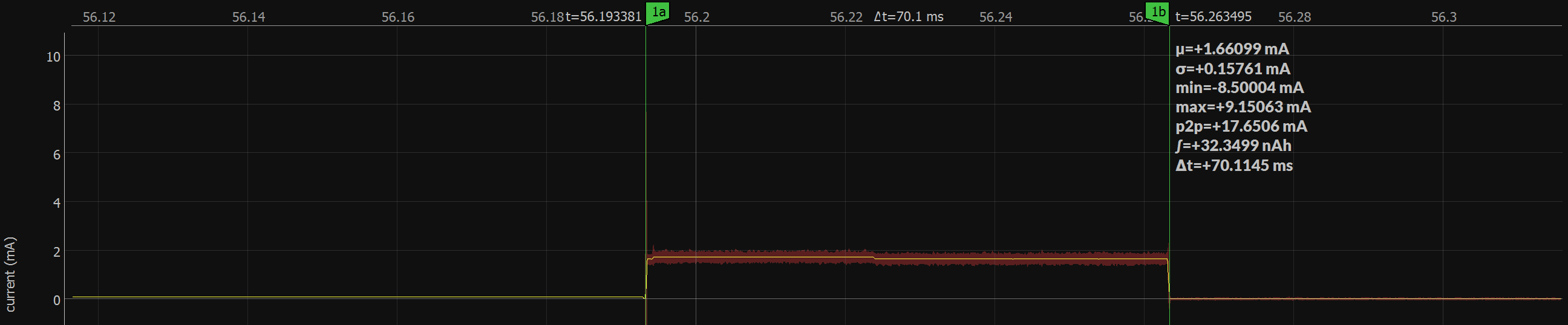

Démarrage

Les bottes FPGA de Flash ont programmé avec une conception de 10 kHz à faible puissance. Le FPGA se configure à partir de Flash et tire de l'alimentation sur le noyau et la banque Flash SPI (banque 1) comme indiqué ci-dessous. Les nombres de consommation d'énergie totaux ainsi que les temps de démarrage sont importants pour les applications qui éteindront le FPGA et l'obligeront à démarrer rarement pour la économie d'énergie. Comme indiqué dans les parcelles ci-dessous, le démarrage du flash consomme environ 46 na d'énergie et prend environ 70 ms du début à la fin. Notez que cela n'inclut pas la consommation d'énergie de la puce flash!

Un échantillon de conception de faible puissance

Ok, génial, maintenant que nous avons des mesures, à quoi bon si nous ne pouvons pas l'utiliser! Commençons par une conception de jouets, donc c'est facile à comprendre.

Exigences

- L'horloge lente doit être la basse vitesse de 10 kHz qui permet au FPGA de répondre aux interruptions externes

- Réveillez-vous sur 50 ms pour effectuer un travail utile toutes les quelques secondes, la «conception des travailleurs» peut être fermée d'horloge ou continuer à fonctionner à 10 kHz au cas où il aurait besoin de répondre à une interruption.

- Travaillez quand Awake doit être à 48 MHz d'horloge

Conception

De toute évidence, nous devons faire la porte de l'horloge sur le FPGA quand il est endormi. Le changement de conception entre 10 kHz et 48 MHz nécessite des soins spéciaux pour éviter les pépins de l'horloge lors du multiplexage entre les deux horloges. Un MUX à horloge sans glitch est un composant assez standard qui le fait proprement.

L'oscillateur à 10 kHz alimente non seulement le GFCM mais aussi le chronométreur qui passe l'horloge à la conception qui fait le travail. Le chronométreur est un compteur simple qui sélectionne la fréquence d'horloge plus élevée pour 50 ms toutes les 3,2 s.

La conception qui fait le travail dans ce cas est un simple clignotant LED et pourrait être remplacé par quelque chose de assez complexe.

Un simple test a été utilisé pour prouver la conception et se débarrasser des bugs ...

Résultats

La conception complète consomme 62 LC, 3 SB_GB, 1 LF_OSC, 1 HF_OSC et le pilote RGB. Voici la consommation actuelle du FPGA sur le rail de puissance central. Comme vous pouvez le voir, cela semble avoir atteint l'objectif!

- Seule la puissance sur le rail central est mesurée

- La ligne de base du courant 135UA est beaucoup plus élevée que le courant du tableau mesuré. On ne sait pas à quoi cela est dû.

- Les travaux de cyclisme! Le courant de pointe est de 2 mA tandis que la puissance de base est d'environ 135ua, la moyenne est de 162UA, mesurée par le compteur de courant.

- L'oscillateur à haute fréquence a dû être désactivé pour accéder à la ligne de base 135UA lorsque sa sortie n'a pas été sélectionnée. Si cela n'est pas fait, la ligne de base est nettement plus élevée à environ 630UA lorsque l'horloge sélectionnée est de 10 kHz.

Travail futur

- Découvrez la puissance lors du mappage de Bram vs Registres

- Consommation électrique des banques IO avec tension et conduite des charges connues

- Variation de courant par rapport à la température

- D'autres idées?