Prueba de energía ICE40

El objetivo de este ejercicio es comprender desde un punto de vista de poder, cuáles son las diversas compensaciones en el ICE40 FPGA. Esto nos permitiría diseñar dispositivos con batería que usen el FPGA y estimar la duración de la batería y también proporcionar una guía de tiempo de diseño.

Configuración

- El hardware utilizado es el tablero de ruptura ICE40 de la red. Este tablero fue elegido cuando estalla todos los rieles de energía del FPGA.

- Utilicé el archivo PCF del upduino como idéntico.

- La absolutamente maravillosa Toolchain de icestorm se utilizó como muy rápida y scriptible. Esperaría resultados comparables de la cadena de herramientas radiante de los proveedores.

- La corriente en cada riel se midió utilizando un Joulescope JS110.

- Se proporciona un ejemplo de matemática de juguete donde dos contadores de 8 bits se multiplican para obtener un resultado de 16 bits en cada ciclo de reloj.

Resultados

Nota: Todas las corrientes en la tabla están en UA.

| Descripción | PLL (1.219V) | Banco 0 (3.283V) | Banco 1 (3.283V) | Banco 2 (3.283V) | Núcleo (1.219v) |

|---|

| No configurado | 4.4 | 1.29 | 1552 | 1.5 | 381.6 |

| Reiniciar | 4.4 | 1.29 | 82.9 | 1.5 | 188.3 |

| Diseño en blanco | 4.1 | 1.3 | 3.4 | 1.5 | 85.6 |

| Contador externo de 12 MHz + 28 bits (32 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 613.5 |

| CONTADOR EXTERNO 12 MHz + 28*2 bits (60 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 616.65 |

| Contador externo de 12 MHz + 28*4 bits (116 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 624.2 |

| Externo 12 MHz + contador de 28*8 bits (228 LC) | 4.1 | 1.3 | 3.4 | 1.5 | 641.3 |

| HFOSC (48 MHz) + contador de 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 2184 |

| HFOSC (24 MHz) + contador de 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 1162 |

| HFOSC (12 MHz) + contador de 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 645 |

| HFOSC (6 MHz) + contador de 24 bits (28 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 388.4 |

| LFOSC (10 kHz) + contador de 24 bits (28 LC) | 4.4 | 3.76 | 3.4 | 1.5 | 96.3 |

| Reloj externo detenido (0 kHz) + contador de 24 bits (28 lc) | 4.4 | 3.76 | 3.4 | 1.5 | 92.1 |

| HFOSC (12 MHz) + matemáticas (sin DSP) + contador de 24 bits (208 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 996 |

| HFOSC (12 MHz) + Matemáticas (1 DSP) + contador de 24 bits (72 LC) | 4.1 | 3.76 | 3.4 | 1.5 | 882 |

| HFOSC + RGB (reloj de 48 MHz) | 4.4 | 321.9 | 3.4 | 1.5 | 2195 |

| PLL (12MHz in, salida de 16MHz) | 138.6 | 1.29 | 3.42 | 1.4 | 1419 |

| PLL (12MHz in, salida de 32MHz) | 138.9 | 1.29 | 3.42 | 1.4 | 2029 |

| PLL (12MHz in, salida de 48MHz) | 103.6 | 1.29 | 3.42 | 1.4 | 2573 |

Observaciones

- ¡Conexión LED realizada Toma 150UA! Desconecte esto para obtener la potencia más baja.

- El controlador RGB toma ~ 280UA, configurando el curren o el rgbleden en cero cae por completo esta corriente.

- Sostener el FPGA en reinicio o dejarlo sin configurar consume más potencia que si está programado con un diseño real de baja potencia.

- Habilitar las resistencias de pulverización en las entradas no cambió el consumo de energía en absoluto. Esto probablemente se deba a que el IO no recoge mucha interferencia. Tocar el IO en este estado hace que el poder aumente.

- Mapear las matemáticas a una porción DSP tienen sentido desde el punto de vista de la potencia, en el ejemplo de juguete anterior, guardamos alrededor de 110UA.

- Un FPGA mínimamente funcional (10 kHz, contador de 24 bits) puede consumir tan solo 4.4 1.219 + 3.76 3.3 + 3.4 3.3 + 1.5 3.3 + 96.3*1.219 = 151UW. El consumo de energía con una tasa de reloj tan baja no cambia significativamente al aumentar el tamaño de diseño (un contador de 1536 ancho hace que la corriente central aumente en 3UA). Esto implica que el FPGA funcionará bastante bien si se usa en un sistema donde el reloj se puede caer a 10 kHz durante largos períodos de tiempo. El reloj de 10 kHz permite que el FPGA responda a una interrupción y también cambie a un reloj más rápido. Alternativamente, el reloj se puede detener por completo en este FPGA también si es suministrado por un reloj externo como se muestra en la prueba del reloj detenido.

Arranque

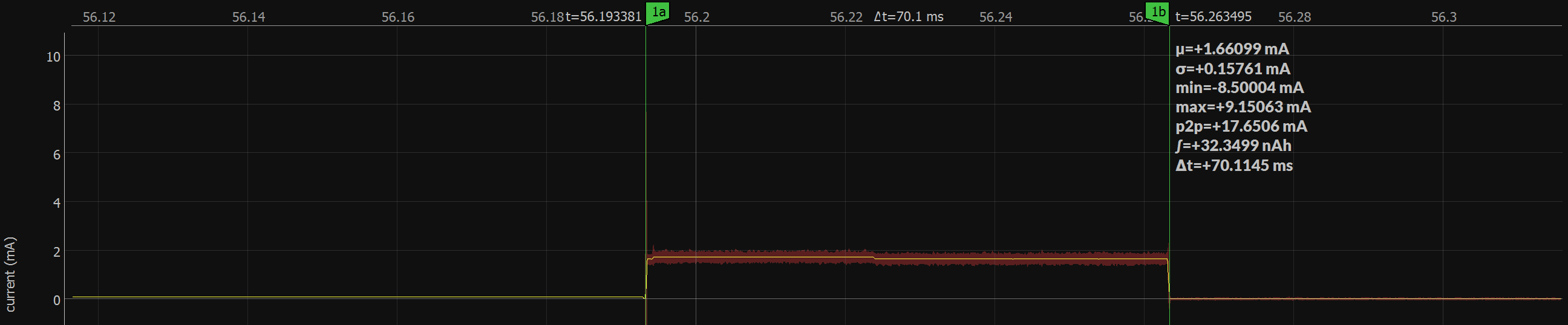

Las botas FPGA de Flash programadas con diseño de 10 kHz de baja potencia. El FPGA se configura de Flash y extrae energía en el Core y SPI Flash Bank (Bank 1) como se muestra a continuación. Los números de consumo de energía total, así como los tiempos de arranque, son importantes para las aplicaciones que alimentarán el FPGA y requieren que inicie con poca frecuencia para el ahorro de energía. Como se muestra en los gráficos a continuación, el arranque del Flash consume aproximadamente 46 nebos de energía y toma aproximadamente 70 ms de principio a fin. ¡Tenga en cuenta que esto no incluye el consumo de energía del chip flash!

Una muestra de diseño de baja potencia

Ok, genial, ahora que tenemos medidas, ¡de qué sirve si no podemos usarlo! Comencemos con un diseño de juguete para que sea fácil de entender.

Requisitos

- El reloj lento debe ser la baja velocidad de 10 kHz que permite que el FPGA responda a interrupciones externas

- Despierta para 50 ms para hacer un trabajo útil cada pocos segundos, el "diseño de trabajadores" puede ser cerrado o seguir funcionando a 10 kHz en caso de que necesite responder a una interrupción.

- El trabajo cuando está despierto debe estar en un reloj de 48MHz

Diseño

Claramente, necesitamos compilar el reloj en el FPGA cuando está dormido. Cambiar el diseño entre 10 kHz y 48MHz requiere un cuidado especial para evitar fallas en el reloj al multiplexar entre los dos relojes. Un mux de reloj sin fallas es un componente bastante estándar que lo hace limpiamente.

El oscilador de 10 kHz alimenta no solo el GFCM sino también el cronometrador que cambia el reloj al diseño que hace el trabajo. El cronometrador es un contador simple que selecciona la tasa de reloj más alta durante 50 ms cada 3.2s.

El diseño que hace el trabajo en este caso es un parpadeo LED simple y podría ser reemplazado por algo bastante complejo.

Se usó un simple Testbench para probar el diseño y deshacerse de los errores ...

Resultados

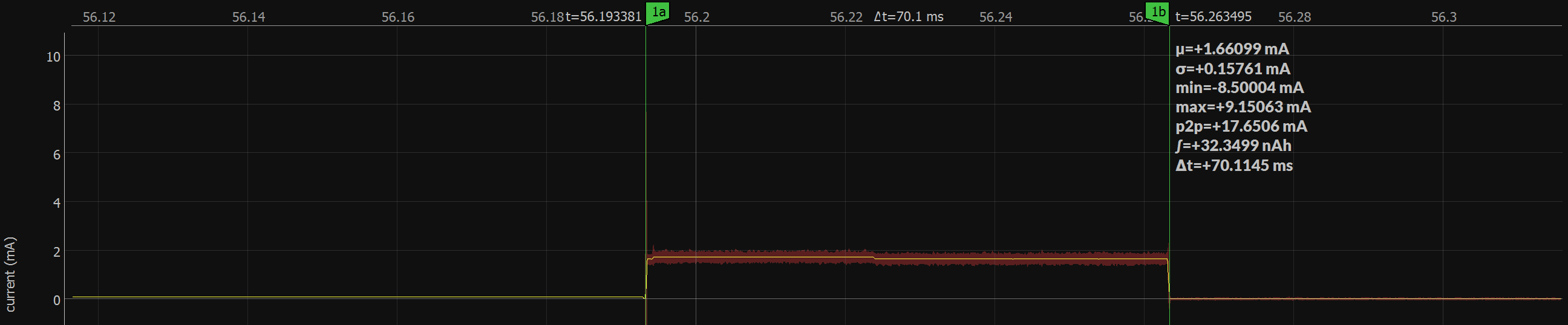

El diseño completo consume 62 LC, 3 SB_GB, 1 LF_OSC, 1 HF_OSC y el controlador RGB. Aquí está el consumo actual del FPGA en el riel de potencia central. Como puede ver, ¡esto parece haber alcanzado el objetivo!

- Solo se mide la potencia en el riel de núcleo

- La línea de base de corriente 135UA es mucho más alta que la corriente en la tabla medida. No está claro a qué se debe esto.

- ¡Funciona el ciclismo de servicio! La corriente máxima es de 2 mA, mientras que la potencia de línea de base es de aproximadamente 135UA, el promedio es de 162UA medido por el medidor de corriente.

- El oscilador de alta frecuencia tuvo que desactivarse para llegar a la línea de base 135UA cuando no se seleccionó su salida. Si esto no se hace, la línea de base es significativamente más alta en aproximadamente 630UA cuando el reloj seleccionado es de 10 kHz.

Trabajo futuro

- Echa un vistazo a la energía cuando se asigna a Bram vs. Registros

- Consumo de energía de bancos IO con voltaje y conducir cargas conocidas

- Variación actual versus temperatura

- ¿Alguna otra idea?