本文檔介紹了虛擬FPGA實驗室。單獨的文件將為您提供幫助:

概述

關於Makerchip

是什麼使項目虛擬FPGA實驗室變得特別?

FPGA董事會證明了

FPGA外圍宏觀實例

例子

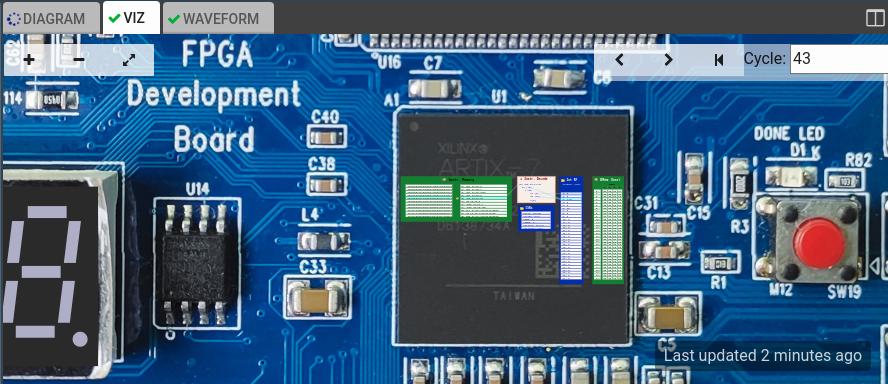

視覺調試

如何添加自己的FPGA板和外圍設備

在實際FPGA中運行的步驟

未來範圍

貢獻者

貢獻

執照

FPGA的新手?現場編程的門陣列(FPGA)是可以編程以進行邏輯操作的硬件電路。它們在在軟件中實施算法和製造特定於應用程序的集成電路(ASIC)之間提供了一個甜蜜的位置。它們通常比軟件實施提供的性能和發電效率要好得多,而實施的時間和費用要比ASIC所需的時間和費用要少得多。即使在向客戶部署後,也可以根據需要對它們進行重新編程以升級功能或修復錯誤(在“字段”中)。 FPGA也對特定於應用程序特定的集成電路(ASIC)或處理器有益。

儘管遠比ASIC更容易獲得,但對於初學者和學生來說,FPGA仍然可能有點昂貴且難以學習。這就是這個項目的來源...不僅適合初學者。

該項目以Makerchip IDE的所有功能和易用性為基礎,並為FPGA開發增加了便利。特別是,我們利用Makerchip的視覺調試功能來提供FPGA及其外圍設備的可視化,從而模仿了物理實驗室的體驗。但是,比物理體驗更好,您還具有基於仿真的開發的好處:快速彙編(無合成,位置和佈局和bitstreams),所有信號值的全部可見性以及對時間的全面控制。

Makerchip除了Verilog/SystemVerilog之外,還可以通過支持TL-Verilog的支持進一步簡化了體驗。 TL-Verilog功能對新移民來說更容易接近(更不用說專家的無數好處了)。

總之:

目前,我們僅使用這些董事會證明,我們計劃將來添加更多董事會。您可以很容易地添加自己的FPGA板。歡迎捐款。

只需單擊此處,然後就去! (右鍵單擊要在新選項卡中打開的。)下面的說明將指導您。

您也可以從此處的任何示例項目開始。

或者,尤其是對於本地FPGA使用,您可以使用MakerChip-App在本地計算機上編輯文件(您可以在其中維護GIT存儲庫並運行FPGA流)。

在模擬中運行一些邏輯後,您將可以使用這些說明將設計導出到任何支持的物理FPGA板。

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

m4+board(...)宏(和外圍宏,例如m4+lcd(...) ,定義硬件)。

m4_lab()為I/OS提供了一個信號超集。董事會或外圍設備上具有相應組件的人應被驅動/使用。其中包括:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

您可以在NAV-TLV選項卡中的m4_lab()宏觀實例化的單行擴展中看到這些信號聲明。

在開始模板中,下面的第三個參數可用於選擇板:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

板包含以下組件的子集,

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

可以實例化外圍和其他外圍設備m4+宏。

這是您可以在Makerchip中加載的一些示例。在示例中,您會在此存儲庫中找到源代碼。 (右鍵單擊在新標籤中打開的鏈接。)

LED模塊

七個段顯示

LCD模塊

VGA顯示

溫度傳感器

輕型傳感器

按鈕

滑動

RGB LED

RISC-V神話核心

板定義出現在fpga_includes.tlv文件的頂部。解釋這些參數並添加新的板子應該很容易。還要確保更新所有可用板的清單(您可以使用git grep -i zedboard找到它)。

以上步驟僅更新虛擬環境。物理FPGA構建流是另一回事,並且依賴於平台,儘管開源平台 - 靜態的構建流都可以使用,我們很樂意使用它們。

我們歡迎您的貢獻。

Makerchip的Visual Debug功能用於創建虛擬FPGA實驗室。

您也可以使用Visual Deubg可視化FPGA內部運行的邏輯。

通過構造代碼以在TL-Verilog中定義FPGA邏輯(不使用純Verilog/Systemverilog排除),您可以在邏輯中添加可視化。

這是示例代碼結構。

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

可以在Makerchip IDE中找到視覺調試文檔和示例。

此鏈接中提供了詳細的分步說明。信用歸功於Mayank Kabra幫助我建立這一部分。

LED演示:鏈接

博客文章

在我們的努力中,我們遇到了以下相關項目。 (在此列表中出現不是認可,只是認識到我們並不孤單。)給我們其他任何人的拉力請求。

這項工作是通過OSFPGA基金會和Google Summer的Code(GSOC)2021贊助的(由Redwood EDA,LLC的指導,並在VLSI System Design中獲得了Redwood Eda LLC的指導,並獲得了Redwood EDA LLC的指導,並獲得了Redwood EDA LLC的指導。

貢獻是使開源社區成為學習,啟發和創造的驚人工具的原因。您所做的任何貢獻都非常感謝。提起錯誤的榮譽。非常感謝您修復它們,並為新董事會提供了新功能和支持。

根據MIT許可分發。請參閱許可證。