Este documento apresenta o laboratório virtual do FPGA. Documentos separados o ajudarão com:

Visão geral

Sobre Makerchip

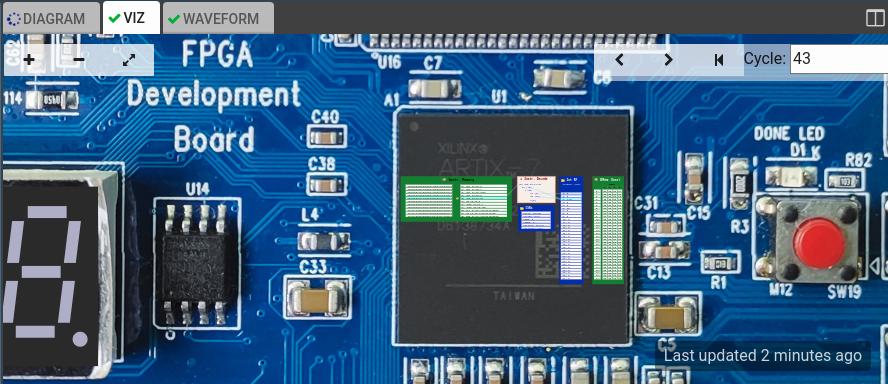

O que torna o Projeto Virtual FPGA Lab especial?

As placas FPGA demonstraram

Instanciações de macro periféricas de FPGA

Exemplos

Debug visual

Como adicionar placas e periféricos FPGA

Passos para executar em um FPGA real

Escopo futuro

Colaboradores

Contribuindo

Licença

Novo no FPGAS? Matrizes de portões programáveis em campo (FPGAs) são um circuito de hardware que pode ser programado para realizar operações lógicas. Eles fornecem um ponto ideal entre a implementação de algoritmos no software e a fabricação de circuitos integrados específicos de aplicativos (ASICs). Eles geralmente fornecem desempenho e eficiência de energia muito melhores do que as implementações de software e exigem muito menos tempo e despesa para implementar do que as ASICs. Eles podem ser reprogramados conforme necessário para atualizar a funcionalidade ou corrigir erros, mesmo após a implantação para os clientes (no "campo"). Os FPGAs também são benéficos para prototipando circuitos integrados específicos de aplicativos (ASICs) ou processadores.

Embora muito mais acessíveis que os ASICs, os FPGAs ainda podem ser um pouco caros e difíceis de aprender para iniciantes e estudantes. É aí que entra esse projeto ... e não é apenas para iniciantes.

Este projeto baseia-se em todo o poder e facilidade de uso do MakerChip IDE e adiciona conveniência para o desenvolvimento do FPGA. Em particular, aproveitamos o recurso de depuração visual da Makerchip para fornecer visualizações de FPGAs e seus periféricos, imitando assim a experiência física do laboratório. Mas melhor que a experiência física, você também tem os benefícios do desenvolvimento baseado em simulação: compilação rápida (sem síntese, local e rotina e transmissões), visibilidade total de todos os valores de sinal e controle total do tempo.

O MakerChip simplifica ainda mais a experiência com suporte para TL-Verilog, além do Verilog/SystemVerilog. Os recursos de TL-Verilog são mais acessíveis aos recém-chegados (sem mencionar os inúmeros benefícios para os especialistas).

Resumindo:

Atualmente, demonstramos usar apenas essas placas e planejamos adicionar mais placas no futuro. Você pode facilmente adicionar suas próprias placas FPGA. Contribuições são bem -vindas.

Basta clicar aqui e ir! (Clique com o botão direito do mouse para abrir em uma nova guia.) As instruções abaixo o guiarão.

Você também pode começar em qualquer projeto de exemplo aqui.

Como alternativa, especialmente para uso local do FPGA, você pode usar o MakerChip-App para editar arquivos em sua máquina local (onde você pode manter seu repositório Git e executar fluxos de FPGA).

Depois de ter alguma lógica em execução na simulação, você poderá exportar seu design para qualquer placa FPGA física suportada usando essas instruções.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

A m4+board(...) macro (e macros periféricas, como m4+lcd(...) , defina o hardware).

m4_lab() fornece um superconjunto de sinais para E/SO. Aqueles que possuem componentes correspondentes na placa ou periféricos devem ser conduzidos/usados. Estes incluem:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

Você pode ver essas declarações de sinal na expansão de uma linha da instanciação de macro m4_lab() na guia NAV-TLV.

No modelo de partida, o terceiro argumento abaixo pode ser usado para selecionar a placa:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

As placas contêm um subconjunto dos seguintes componentes,

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

Os periféricos externos e outros podem ser as macros Uisng m4+ instantadas.

Aqui estão um exemplo que você pode carregar no MakerChip. Você encontrará o código -fonte neste repositório em exemplos. (Clique com o botão direito do mouse em links para abrir em uma nova guia.)

Módulo LED

Sete displays de segmento

Módulo LCD

VGA Display

Sensor de temperatura

Sensor de luz

Botões de pressão

Slideswitches

RGB LED

Risc-v mito núcleo

As definições da placa aparecem na parte superior do arquivo fpga_includes.tlv . Deve ser fácil o suficiente para interpretar esses parâmetros e adicionar novas placas pelo exemplo. Certifique -se de atualizar todas as listagens das placas disponíveis (que você pode encontrar usando git grep -i zedboard ).

As etapas acima atualizam apenas o ambiente virtual. O fluxo físico de construção do FPGA é uma questão diferente e depende da plataforma, embora estejam disponíveis fluxos de construção de plataforma de código aberto, e gostaríamos de usá-los.

Congratulamo -nos com suas contribuições.

O recurso de depuração visual do MakerChip é usado para criar o laboratório FPGA virtual.

Você também pode usar o Visual Deubg para visualizar a lógica em execução dentro do FPGA.

Ao estruturar seu código para definir sua lógica FPGA no TL-Verilog (que não exclui usando o Verilog/SystemVerilog puro), você pode adicionar visualização à sua lógica.

Aqui está uma estrutura de código de amostra.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

A documentação e exemplos visuais de depuração podem ser encontrados no MakerChip IDE.

As instruções passo a passo detalhadas são fornecidas neste link. O crédito vai para Mayank Kabra por me ajudar a construir essa parte.

Demonstração LED: Link

Postagem do blog

Em nossos esforços, encontramos os seguintes projetos relacionados. (A aparição nesta lista não é um endosso, apenas um reconhecimento de que não estamos sozinhos.) Faça uma solicitação de tração com outros.

Este trabalho foi patrocinado pela OSFPGA Foundation e pelo Google Summer of Code (GSOC) 2021 (com a Fundação Silicon Livre e Open Silicon (Fossi) como uma organização GSOC Umbrella), com orientação da Redwood EDA, LLC e com suporte de treinamento do design do sistema VLSI.

As contribuições são o que tornam a comunidade de código aberto um veículo tão incrível para aprender, inspirar e criar. Quaisquer contribuições que você faz são muito apreciadas . Parabéns por preenchimento de bugs. Agradecemos mais profundos por consertá -los e por contribuir com novos recursos e suporte para novas placas.

Distribuído sob a licença do MIT. Veja License.md.