In diesem Dokument wird das virtuelle FPGA -Labor vorgestellt. Separate Dokumente helfen Ihnen bei:

Überblick

Über Makerchip

Was macht das Projekt Virtual FPGA Lab zu besonders?

FPGA -Boards demonstriert

Fpga periphere Makro -Instanziationen

Beispiele

Visuelles Debuggen

So fügen Sie eigene FPGA -Boards und Peripheriegeräte hinzu

Schritte zum Ausführen in einem tatsächlichen FPGA

Zukünftiger Umfang

Mitwirkende

Beitragen

Lizenz

Neu in FPGAs? Feldprogrammierbare Gate-Arrays (FPGAs) sind Hardwareschaltungen, die so programmiert werden können, dass er logische Vorgänge ausführt. Sie bieten einen Sweet Spot zwischen der Implementierung von Algorithmen in der Software und der Herstellung von anwendungsspezifischen integrierten Schaltungen (ASICs). Sie bieten im Allgemeinen eine weitaus bessere Leistung und Energieeffizienz als Software-Implementierungen und benötigen weitaus weniger Zeit und Kosten für die Implementierung als ASICs. Sie können nach Bedarf neu programmiert werden, um die Funktionalität zu verbessern oder Fehler zu beheben, auch nach der Bereitstellung für Kunden (im "Feld"). FPGAs sind auch für Prototyping-anwendungsspezifische integrierte Schaltkreise (ASICs) oder Prozessoren von Vorteil.

Obwohl FPGAs weitaus zugänglicher als ASICs, können sie für Anfänger und Schüler immer noch ein bisschen kostspielig und schwer zu lernen sein. Hier kommt dieses Projekt ins Spiel ... und es ist nicht nur für Anfänger.

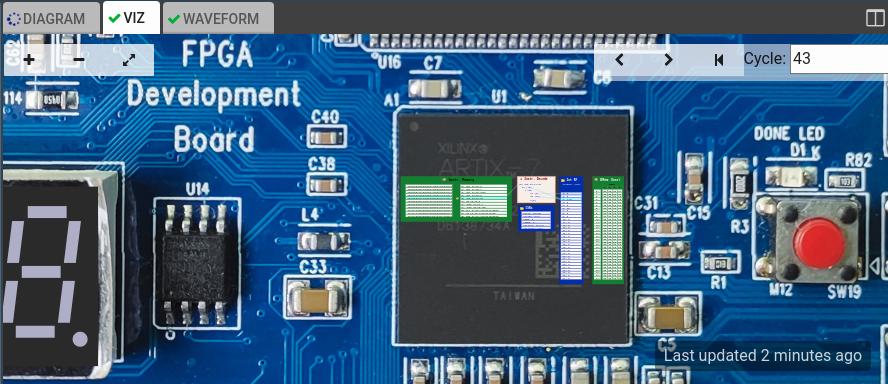

Dieses Projekt baut auf der gesamten Kraft und der Benutzerfreundlichkeit der Makerchip-IDE auf und fügt die FPGA-Entwicklung ein. Insbesondere nutzen wir die visuelle Debug -Funktion von Makerchip, um Visualisierungen von FPGAs und deren Peripheriegeräte zu bieten und damit das physische Laborerlebnis nachzuahmen. Aber besser als die physische Erfahrung, Sie haben auch die Vorteile einer simulationsbasierten Entwicklung: schnelle Zusammenstellung (keine Synthese, Ort und Route und Bitstreams), vollständige Sichtbarkeit aller Signalwerte und vollständige Kontrolle der Zeit.

Makerchip vereinfacht die Erfahrung mit Unterstützung für TL-Verilog zusätzlich zu Verilog/Systemverilog. TL-Verilog-Funktionen sind für Neuankömmlinge zugänglicher (ganz zu schweigen von den unzähligen Vorteilen für Experten).

Zusammenfassend:

Derzeit zeigen wir nur diese Boards und planen, in Zukunft weitere Boards hinzuzufügen. Sie können Ihre eigenen FPGA -Boards sehr leicht hinzufügen. Beiträge sind willkommen.

Klicken Sie einfach hier und gehen Sie! (Klicken Sie mit der rechten Maustaste, um in einer neuen Registerkarte zu öffnen.) Anweisungen unten werden Sie leiten.

Sie können hier auch von jedem Beispielprojekt aus starten.

Insbesondere für die lokale FPGA-Verwendung können Sie Makerchip-App verwenden, um Dateien auf Ihrem lokalen Computer zu bearbeiten (wo Sie Ihr Git-Repository beibehalten und FPGA-Flows ausführen können).

Sobald Sie eine Logik in der Simulation erhalten, können Sie Ihr Design mit diesen Anweisungen in eine unterstützte physische FPGA -Karte exportieren.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

Das m4+board(...) -Makro (und periphere Makros wie m4+lcd(...) definieren die Hardware).

m4_lab() bietet eine Superset von Signalen für I/OS. Diejenigen, die entsprechende Komponenten auf der Tafel oder Peripheriegeräte haben, sollten angetrieben/verwendet werden. Dazu gehören:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

Sie können diese Signaldeklarationen in der One-Line-Erweiterung der m4_lab() -Makro-Instanziierung auf der Registerkarte NAV-TLV sehen.

In der Startvorlage kann das folgende 3. Argument verwendet werden, um die Karte auszuwählen:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

Boards enthalten eine Teilmenge der folgenden Komponenten.

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

Externe und andere Peripheriegeräte können UISNG m4+ Makros instanziiert werden.

Hier sind einige Beispiele, die Sie Makerchip einladen können. Sie finden den Quellcode in diesem Repository unter Beispielen. (Klicken Sie mit der rechten Maustaste Links, um sie in einer neuen Registerkarte zu öffnen.)

LED -Modul

Sieben Segment -Anzeigen

LCD -Modul

VGA -Anzeige

Temperatursensor

Lichtsensor

Knöpfe drücken

Slidenschalter

RGB LED

Risc-V Mythos

Die Board -Definitionen werden oben in der Datei fpga_includes.tlv angezeigt. Es sollte einfach genug sein, diese Parameter zu interpretieren und neue Boards mit Beispiel hinzuzufügen. Stellen Sie sicher, dass Sie auch alle Angebote der verfügbaren Boards aktualisieren (die Sie mit git grep -i zedboard finden können).

Die obigen Schritte aktualisieren nur die virtuelle Umgebung. Der physische FPGA Build Flow ist eine andere Sache und ist plattformabhängig, obwohl Open-Source-Plattform-Agnostic-Build-Flüsse verfügbar sind und wir sie gerne verwenden würden.

Wir begrüßen Ihre Beiträge.

Die visuelle Debug -Funktion von Makerchip wird zum Erstellen des virtuellen FPGA -Labors verwendet.

Sie können auch Visual Deubg verwenden, um die Logik zu visualisieren, die in der FPGA ausgeführt wird.

Indem Sie Ihren Code strukturieren, um Ihre FPGA-Logik in TL-Verilog zu definieren (was mit Pure Verilog/Systemverilog nicht ausschließt) können Sie Ihrer Logik Visualisierung hinzufügen.

Hier ist eine Beispielcodestruktur.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

In der Makerchip -IDE finden sich visuelle Debug -Dokumentation und Beispiele.

In diesem Link finden Sie detaillierte Schritt-für-Schritt-Anweisungen. Der Guthaben geht Mayank Kabra für den Aufbau dieses Teils.

LED -Demo: Link

Blog -Beitrag

In unseren Bemühungen sind wir auf die folgenden verwandten Projekte gestoßen. (Erscheinung auf dieser Liste ist keine Bestätigung, sondern nur eine Erkenntnis, dass wir nicht allein sind.) Geben Sie uns eine Pull -Anfrage mit anderen.

Diese Arbeit wurde über die OSFPGA Foundation und den Google Summer of Code (GSOC) 2021 (mit der Free und Open Source Silicon Foundation (FOSSI) als GSOC -Dachorganisation) gesponsert.

Beiträge machen die Open -Source -Community zu einem erstaunlichen Fahrzeug, um zu lernen, zu inspirieren und zu kreieren. Alle Beiträge, die Sie leisten, werden sehr geschätzt . Ein großes Lob für die Einreichung von Fehler. DANKE DANKE, dass Sie sie behoben haben und neue Funktionen und Unterstützung für neue Boards beigetragen haben.

Unter der MIT -Lizenz verteilt. Siehe Lizenz.MD.