本文档介绍了虚拟FPGA实验室。单独的文件将为您提供帮助:

概述

关于Makerchip

是什么使项目虚拟FPGA实验室变得特别?

FPGA董事会证明了

FPGA外围宏观实例

例子

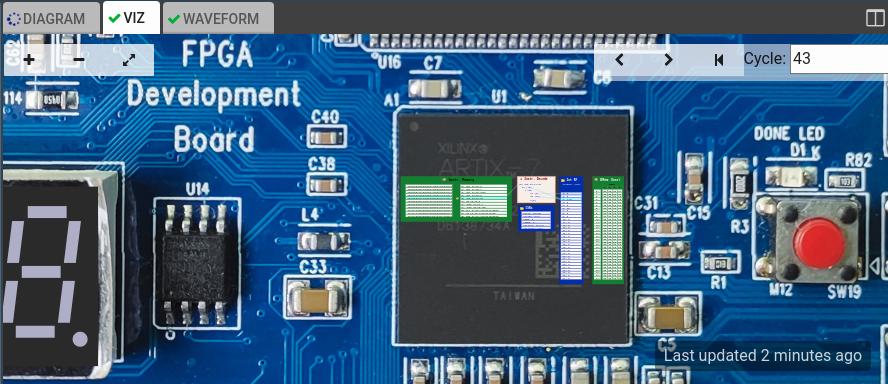

视觉调试

如何添加自己的FPGA板和外围设备

在实际FPGA中运行的步骤

未来范围

贡献者

贡献

执照

FPGA的新手?现场编程的门阵列(FPGA)是可以编程以进行逻辑操作的硬件电路。它们在在软件中实施算法和制造特定于应用程序的集成电路(ASIC)之间提供了一个甜蜜的位置。它们通常比软件实施提供的性能和发电效率要好得多,而实施的时间和费用要比ASIC所需的时间和费用要少得多。即使在向客户部署后,也可以根据需要对它们进行重新编程以升级功能或修复错误(在“字段”中)。 FPGA也对特定于应用程序特定的集成电路(ASIC)或处理器有益。

尽管远比ASIC更容易获得,但对于初学者和学生来说,FPGA仍然可能有点昂贵且难以学习。这就是这个项目的来源...不仅适合初学者。

该项目以Makerchip IDE的所有功能和易用性为基础,并为FPGA开发增加了便利。特别是,我们利用Makerchip的视觉调试功能来提供FPGA及其外围设备的可视化,从而模仿了物理实验室的体验。但是,比物理体验更好,您还具有基于仿真的开发的好处:快速汇编(无合成,位置和布局和bitstreams),所有信号值的全部可见性以及对时间的全面控制。

Makerchip除了Verilog/SystemVerilog之外,还可以通过支持TL-Verilog的支持进一步简化了体验。 TL-Verilog功能对新移民来说更容易接近(更不用说专家的无数好处了)。

总之:

目前,我们仅使用这些董事会证明,我们计划将来添加更多董事会。您可以很容易地添加自己的FPGA板。欢迎捐款。

只需单击此处,然后就去! (右键单击要在新选项卡中打开的。)下面的说明将指导您。

您也可以从此处的任何示例项目开始。

或者,尤其是对于本地FPGA使用,您可以使用MakerChip-App在本地计算机上编辑文件(您可以在其中维护GIT存储库并运行FPGA流)。

在模拟中运行一些逻辑后,您将可以使用这些说明将设计导出到任何支持的物理FPGA板。

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

m4+board(...)宏(和外围宏,例如m4+lcd(...) ,定义硬件)。

m4_lab()为I/OS提供了一个信号超集。董事会或外围设备上具有相应组件的人应被驱动/使用。其中包括:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

您可以在NAV-TLV选项卡中的m4_lab()宏观实例化的单行扩展中看到这些信号声明。

在开始模板中,下面的第三个参数可用于选择板:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

板包含以下组件的子集,

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

可以实例化外围和其他外围设备m4+宏。

这是您可以在Makerchip中加载的一些示例。在示例中,您会在此存储库中找到源代码。 (右键单击在新标签中打开的链接。)

LED模块

七个段显示

LCD模块

VGA显示

温度传感器

轻型传感器

按钮

滑动

RGB LED

RISC-V神话核心

板定义出现在fpga_includes.tlv文件的顶部。解释这些参数并添加新的板子应该很容易。还要确保更新所有可用板的清单(您可以使用git grep -i zedboard找到它)。

以上步骤仅更新虚拟环境。物理FPGA构建流是另一回事,并且依赖于平台,尽管开源平台 - 静态的构建流都可以使用,我们很乐意使用它们。

我们欢迎您的贡献。

Makerchip的Visual Debug功能用于创建虚拟FPGA实验室。

您也可以使用Visual Deubg可视化FPGA内部运行的逻辑。

通过构造代码以在TL-Verilog中定义FPGA逻辑(不使用纯Verilog/Systemverilog排除),您可以在逻辑中添加可视化。

这是示例代码结构。

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

可以在Makerchip IDE中找到视觉调试文档和示例。

此链接中提供了详细的分步说明。信用归功于Mayank Kabra帮助我建立这一部分。

LED演示:链接

博客文章

在我们的努力中,我们遇到了以下相关项目。 (在此列表中出现不是认可,只是认识到我们并不孤单。)给我们其他任何人的拉力请求。

这项工作是通过OSFPGA基金会和Google Summer的Code(GSOC)2021赞助的(由Redwood EDA,LLC的指导,并在VLSI System Design中获得了Redwood Eda LLC的指导,并获得了Redwood EDA LLC的指导,并获得了Redwood EDA LLC的指导。

贡献是使开源社区成为学习,启发和创造的惊人工具的原因。您所做的任何贡献都非常感谢。提起错误的荣誉。非常感谢您修复它们,并为新董事会提供了新功能和支持。

根据MIT许可分发。请参阅许可证。