Este documento presenta el laboratorio FPGA virtual. Los documentos separados lo ayudarán con:

Descripción general

Sobre makerchip

¿Qué hace que el Project Virtual FPGA Lab sea especial?

Tableros de FPGA demostrados

FPGA Instantiaciones de macro periféricas

Ejemplos

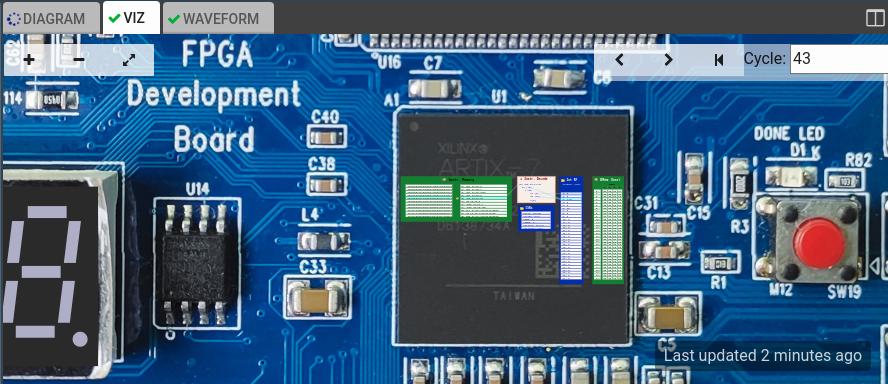

Depuración visual

Cómo agregar propias tablas y periféricos FPGA

Pasos para ejecutar en un FPGA real

Alcance futuro

Colaboradores

Que contribuye

Licencia

¿Nuevo en FPGA? Las matrices de compuerta programables de campo (FPGA) son un circuito de hardware que se pueden programar para llevar a cabo operaciones lógicas. Proporcionan un punto óptimo entre la implementación de algoritmos en el software y la fabricación de circuitos integrados específicos de la aplicación (ASIC). Generalmente proporcionan un rendimiento y eficiencia de potencia mucho mejor que las implementaciones de software, y requieren mucho menos tiempo y gastos para implementar que los ASIC. Se pueden reprogramarse según sea necesario para actualizar la funcionalidad o corregir errores, incluso después de la implementación en los clientes (en el "campo"). Los FPGA también son beneficiosos para la creación de prototipos de circuitos integrados específicos de la aplicación (ASICS) o procesadores.

Aunque mucho más accesible que los ASIC, los FPGA aún pueden ser un poco costosos y difíciles de aprender para principiantes y estudiantes. Ahí es donde entra este proyecto ... y no es solo para principiantes.

Este proyecto se basa en toda la potencia y la facilidad de uso de MakerChip IDE y agrega conveniencia para el desarrollo de FPGA. En particular, aprovechamos la función de depuración visual de Makerchip para proporcionar visualizaciones de FPGA y sus periféricos, imitando así la experiencia de laboratorio físico. Pero mejor que la experiencia física, también tiene los beneficios del desarrollo basado en la simulación: compilación rápida (sin síntesis, lugar y rutas y bitsreams), visibilidad total de todos los valores de señal y control total del tiempo.

MakerChip simplifica aún más la experiencia con el soporte para TL-Verilog además de Verilog/SystemVerilog. Las características de TL-Verilog son más accesibles para los recién llegados (sin mencionar los innumerables beneficios para los expertos).

En resumen:

Actualmente demostramos usar solo estas juntas y planeamos agregar más tablas en el futuro. Puede agregar fácilmente sus propios tableros FPGA. Las contribuciones son bienvenidas.

¡Simplemente haga clic aquí y vaya! (Haga clic derecho para abrir en una nueva pestaña). Las instrucciones a continuación lo guiarán.

También puede comenzar desde cualquiera de los proyectos de ejemplo aquí.

Alternativamente, especialmente para el uso local de FPGA, puede usar MakerChip-App para editar archivos en su máquina local (donde puede mantener su repositorio GIT y ejecutar flujos de FPGA).

Una vez que tenga algo de lógica ejecutándose en simulación, podrá exportar su diseño a cualquier placa FPGA física compatible utilizando estas instrucciones.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

La m4+board(...) macro (y las macros periféricas, como m4+lcd(...) , definen el hardware).

m4_lab() proporciona un superconjunto de señales para I/OS. Aquellos que tienen componentes correspondientes en la placa o periféricos deben ser conducidos/usados. Estos incluyen:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

Puede ver estas declaraciones de señal en la expansión de una línea de la instanciación macro m4_lab() en la pestaña NAV-TLV.

En la plantilla de inicio, el tercer argumento a continuación se puede usar para seleccionar la placa:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

Las tablas contienen un subconjunto de los siguientes componentes,

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

Los periféricos externos y otros se pueden instanciar uisng m4+ macros.

Aquí hay algún ejemplo que puede cargar en MakerChip. Encontrará el código fuente en este repositorio bajo ejemplos. (Haga clic derecho en enlaces para abrir en una nueva pestaña)

Módulo LED

Pantallas de siete segmentos

Módulo LCD

Pantalla VGA

Sensor de temperatura

Sensor de luz

Botones de presentación

Toboganes

LED RGB

Núcleo de mito risc-v

Las definiciones de la placa aparecen en la parte superior del archivo fpga_includes.tlv . Debería ser bastante fácil interpretar estos parámetros y agregar nuevas placas con el ejemplo. Asegúrese también de actualizar todos los listados de tableros disponibles (que puede encontrar utilizando git grep -i zedboard ).

Los pasos anteriores actualizan solo el entorno virtual. El flujo físico de compilación FPGA es un asunto diferente y depende de la plataforma, aunque los flujos de construcción de plataforma de código abierto están disponibles, y nos encantaría usarlos.

Agradecemos sus contribuciones.

La función de depuración visual de Makerchip se utiliza para crear el laboratorio FPGA virtual.

También puede usar Visual Deubg para visualizar la lógica que se ejecuta dentro del FPGA.

Al estructurar su código para definir su lógica FPGA en TL-Verilog (que no impide el uso de Verilog/SystemVerilog puro), puede agregar visualización a su lógica.

Aquí hay una estructura de código de muestra.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

La documentación y los ejemplos de depuración visual se pueden encontrar dentro del IDE MakerChip.

Se proporcionan instrucciones detalladas paso a paso en este enlace. El crédito va a Mayank Kabra por ayudarme a construir esta parte.

Demo LED: enlace

Blog

En nuestros esfuerzos, nos hemos encontrado con los siguientes proyectos relacionados. (La apariencia en esta lista no es un respaldo, solo un reconocimiento de que no estamos solos). Danos una solicitud de extracción con cualquier otra.

Este trabajo ha sido patrocinado a través de la Fundación OSFPGA y Google Summer of Code (GSOC) 2021 (con la Fundación Silicon Silicon (FOSSI) gratuita y libre como una organización paraguas de GSOC), con mentoría de Redwood EDA, LLC, y con soporte de capacitación de VLSI System Design.

Las contribuciones son las que hacen que la comunidad de código abierto sea un vehículo tan increíble para aprender, inspirar y crear. Cualquier contribución que haga es muy apreciada . Felicitaciones por archivos de errores. El más profundo agradecimiento por arreglarlos y por contribuir con nuevas características y soporte para nuevas tablas.

Distribuido bajo la licencia MIT. Ver licencia. MD.