이 문서는 가상 FPGA 실험실을 소개합니다. 별도의 문서가 다음에 도움이됩니다.

개요

Makerchip에 대해

Project Virtual FPGA Lab Special로 만드는 이유는 무엇입니까?

FPGA 보드가 시연되었습니다

FPGA 말초 거시 인스턴스화

예

비주얼 디버그

자체 FPGA 보드 및 주변 장치를 추가하는 방법

실제 FPGA에서 실행하는 단계

미래의 범위

기고자

기여

특허

FPGAS를 처음 접했습니까? FPGAS (Field-Programmable Gate Array)는 논리 작업을 수행하도록 프로그래밍 할 수있는 하드웨어 회로입니다. 소프트웨어에서 알고리즘 구현과 애플리케이션 별 통합 회로 (ASIC)를 제작하는 것 사이의 달콤한 지점을 제공합니다. 그들은 일반적으로 소프트웨어 구현보다 훨씬 더 나은 성능과 전력 효율성을 제공하며 ASIC보다 구현하는 데 훨씬 적은 시간과 비용이 필요합니다. 고객에게 배포 한 후에도 ( "필드") 기능을 업그레이드하거나 버그를 수정하는 데 필요에 따라 재 프로그래밍 할 수 있습니다. FPGA는 또한 프로토 타이핑 애플리케이션 별 통합 회로 (ASIC) 또는 프로세서에 도움이됩니다.

FPGA는 ASIC보다 훨씬 접근하기 쉬운하지만 초보자와 학생들에게는 여전히 비용이 많이 들고 배우기가 어려울 수 있습니다. 이 프로젝트가 시작되는 곳입니다. 초보자만을위한 것이 아닙니다.

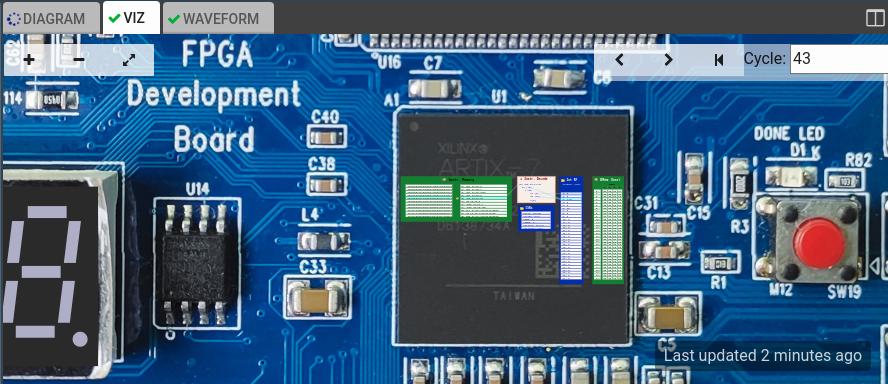

이 프로젝트는 Makerchip IDE의 모든 힘과 사용 편의성을 기반으로하며 FPGA 개발의 편의를 더합니다. 특히, 우리는 Makerchip의 시각적 디버그 기능을 활용하여 FPGA 및 주변 장치의 시각화를 제공하여 물리적 실험실 경험을 모방합니다. 그러나 물리적 경험보다 더 나은 시뮬레이션 기반 개발의 이점과 같은 빠른 편집 (합성, 장소 및 경로 및 비트 스트림), 모든 신호 값의 전체 가시성 및 시간 제어 기능도 있습니다.

Makerchip은 Verilog/SystemVerilog 외에도 TL-Verilog를 지원하는 경험을 더욱 단순화합니다. TL-Verilog 기능은 신규 이민자에게 더 접근하기 쉬운 것입니다 (전문가에게 수많은 이점은 말할 것도 없습니다).

요약 :

현재 우리는이 보드 만 사용하는 것을 보여 주며 앞으로 더 많은 보드를 추가 할 계획입니다. 자신의 FPGA 보드를 매우 쉽게 추가 할 수 있습니다. 기부금을 환영합니다.

여기를 클릭하고 가십시오! (새 탭에서 오른 마우스 오른쪽 버튼을 클릭하십시오.) 아래 지침이 안내합니다.

여기에서 예제 프로젝트에서 시작할 수도 있습니다.

또는 특히 로컬 FPGA 사용의 경우 MakerChip-App을 사용하여 로컬 컴퓨터의 파일을 편집 할 수 있습니다 (GIT 저장소를 유지 관리하고 FPGA 흐름을 실행할 수 있음).

시뮬레이션에서 논리가 실행되면이 지침을 사용하여 지원되는 물리적 FPGA 보드에 디자인을 내보낼 수 있습니다.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

m4+board(...) 매크로 (및 m4+lcd(...) 와 같은 주변 마크로가 하드웨어를 정의합니다).

m4_lab() I/O에 대한 신호를 제공합니다. 보드 또는 주변 장치에 해당 구성 요소가있는 사람은 구동/사용해야합니다. 여기에는 다음이 포함됩니다.

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

NAV-TLV 탭에서 m4_lab() 매크로 인스턴스화의 한 줄 확장에서 이러한 신호 선언을 볼 수 있습니다.

시작 템플릿에서 아래 세 번째 인수는 보드를 선택하는 데 사용될 수 있습니다.

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

보드에는 다음 구성 요소의 하위 집합이 포함되어 있으며

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

외부 및 기타 주변 장치는 UISNG m4+ 매크로를 인스턴스화 할 수 있습니다.

다음은 Makerchip에로드 할 수있는 몇 가지 예입니다. 이 저장소에서 예제 아래에서 소스 코드를 찾을 수 있습니다. (새 탭에서 열려 링크를 마우스 오른쪽 버튼으로 클릭하십시오.)

LED 모듈

7 개의 세그먼트가 표시됩니다

LCD 모듈

VGA 디스플레이

온도 센서

라이트 센서

푸시 버튼

슬라이드 스위치

RGB LED

RISC-V 신화 핵심

보드 정의는 fpga_includes.tlv 파일의 맨 위에 나타납니다. 이러한 매개 변수를 해석하고 예제로 새 보드를 추가하기에 충분히 쉬워야합니다. 사용 가능한 보드의 모든 목록 ( git grep -i zedboard 사용하여 찾을 수 있음)을 업데이트하십시오.

위의 단계는 가상 환경 만 업데이트합니다. 물리적 FPGA 빌드 흐름은 다른 문제이며 플랫폼 의존적이지만 오픈 소스 플랫폼 공수 빌드 흐름을 사용할 수 있지만 사용하고 싶습니다.

우리는 당신의 기여를 환영합니다.

Makerchip의 Visual Debug 기능은 가상 FPGA 실험실을 만드는 데 사용됩니다.

Visual deubg를 사용하여 FPGA 내부에서 실행되는 논리를 시각화 할 수도 있습니다.

TL-Verilog (Pure Verilog/SystemVerilog를 사용하지 않는 경우)에서 FPGA 논리를 정의하기 위해 코드를 구조화하면 논리에 시각화를 추가 할 수 있습니다.

다음은 샘플 코드 구조입니다.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

시각적 디버그 설명서 및 예제는 Makerchip IDE 내에서 찾을 수 있습니다.

이 링크에는 자세한 단계별 지침이 제공됩니다. 신용은 Mayank Kabra 에게이 부분을 구축하도록 도와줍니다.

LED 데모 : 링크

블로그 게시물

우리의 노력에서 우리는 다음과 관련된 프로젝트를 발견했습니다. (이 목록에 나타나는 것은 보증이 아니라 우리가 혼자가 아니라는 인식 일뿐입니다.) 다른 사람들과의 풀 요청을 제공하십시오.

이 작업은 OSFPGA Foundation 및 Google Summer of Code (GSOC) 2021 (GSOC (Free and Open Source Silicon Foundation) (GSOC Umbrella 조직으로), Redwood Eda, LLC의 멘토링 및 VLSI 시스템 설계의 교육 지원을 통해 후원되었습니다.

기부금은 오픈 소스 커뮤니티를 배우고, 영감을주고, 창조 할 수있는 놀라운 차량으로 만드는 것입니다. 당신이하는 모든 기여는 대단히 감사합니다 . 버그를 제출하기위한 Kudos. 새로운 기능과 새로운 보드에 대한 새로운 기능과 지원을 제공해 주셔서 감사합니다.

MIT 라이센스에 따라 배포됩니다. License.md를 참조하십시오.