Dokumen ini memperkenalkan lab FPGA virtual. Dokumen terpisah akan membantu Anda dengan:

Ringkasan

Tentang Makerchip

Apa yang membuat Project Virtual FPGA Lab Special?

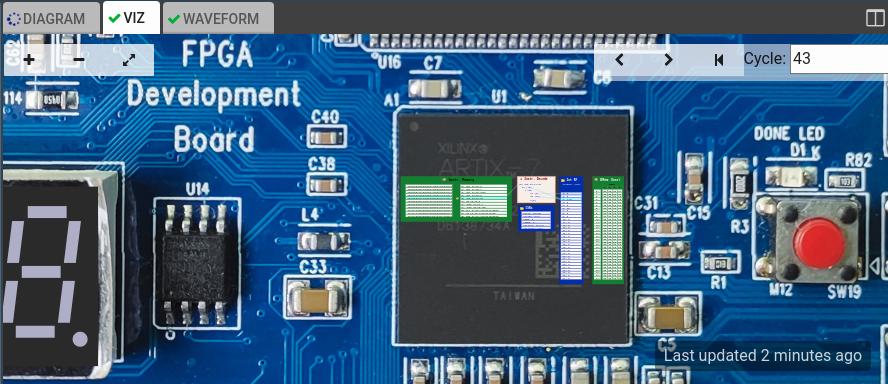

Papan FPGA ditunjukkan

Instantiasi makro perifer FPGA

Contoh

Visual Debug

Cara menambahkan papan dan periferal FPGA sendiri

Langkah untuk dijalankan dalam FPGA yang sebenarnya

Ruang lingkup masa depan

Kontributor

Berkontribusi

Lisensi

Baru di FPGA? Array gerbang yang dapat diprogram lapangan (FPGA) adalah sirkuit perangkat keras yang dapat diprogram untuk melakukan operasi logis. Mereka memberikan sweet spot antara algoritma implementasi dalam perangkat lunak dan membuat sirkuit terintegrasi khusus aplikasi (ASIC). Mereka umumnya memberikan kinerja dan efisiensi daya yang jauh lebih baik daripada implementasi perangkat lunak, dan mereka membutuhkan waktu dan biaya yang jauh lebih sedikit untuk diterapkan daripada ASIC. Mereka dapat diprogram ulang sesuai kebutuhan untuk meningkatkan fungsionalitas atau memperbaiki bug, bahkan setelah penyebaran kepada pelanggan (di "bidang"). FPGA juga bermanfaat untuk membuat prototipe sirkuit terintegrasi khusus aplikasi (ASIC) atau prosesor.

Meskipun jauh lebih mudah diakses daripada ASIC, FPGA masih bisa sedikit mahal dan sulit dipelajari untuk pemula dan siswa. Di situlah proyek ini masuk ... dan itu bukan hanya untuk pemula.

Proyek ini dibangun di atas semua kekuatan dan kemudahan penggunaan MakerChip IDE dan menambah kenyamanan untuk pengembangan FPGA. Secara khusus, kami memanfaatkan fitur debug visual MakerChip untuk memberikan visualisasi FPGA dan periferal mereka, sehingga meniru pengalaman lab fisik. Tetapi lebih baik dari pengalaman fisik, Anda juga memiliki manfaat dari pengembangan berbasis simulasi: kompilasi cepat (tidak ada sintesis, tempat-dan-rute, dan bitstream), visibilitas penuh dari semua nilai sinyal, dan kontrol penuh waktu.

MakerChip semakin menyederhanakan pengalaman dengan dukungan untuk TL-Verilog selain Verilog/SystemVerilog. Fitur TL-Verilog lebih mudah didekati untuk pendatang baru (belum lagi berbagai manfaat bagi para ahli).

Singkatnya:

Saat ini kami menunjukkan hanya menggunakan papan ini dan kami berencana untuk menambahkan lebih banyak papan di masa depan. Anda dapat dengan mudah menambahkan papan FPGA Anda sendiri. Kontribusi dipersilakan.

Cukup klik di sini, dan pergi! (Klik kanan untuk dibuka di tab baru.) Instruksi di bawah ini akan memandu Anda.

Anda juga dapat mulai dari salah satu contoh proyek di sini.

Bergantian, terutama untuk penggunaan FPGA lokal, Anda dapat menggunakan MakerChip-App untuk mengedit file pada mesin lokal Anda (di mana Anda dapat mempertahankan repositori git Anda dan menjalankan aliran FPGA).

Setelah Anda memiliki beberapa logika yang berjalan dalam simulasi, Anda dapat mengekspor desain Anda ke papan FPGA fisik yang didukung menggunakan instruksi ini.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

Makro m4+board(...) (dan makro perifer, seperti m4+lcd(...) , tentukan perangkat keras).

m4_lab() memberikan superset sinyal untuk I/OS. Mereka yang memiliki komponen yang sesuai di papan atau periferal harus didorong/digunakan. Ini termasuk:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

Anda dapat melihat deklarasi sinyal ini dalam ekspansi satu baris dari instantiasi makro m4_lab() di tab Nav-TLV.

Dalam templat awal, argumen ke -3 di bawah ini dapat digunakan untuk memilih papan:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

Papan berisi subset dari komponen berikut,

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

Perhiasan eksternal dan lainnya dapat dipakai macro UISNG m4+ .

Berikut adalah beberapa contoh yang dapat Anda muat di MakerChip. Anda akan menemukan kode sumber di repositori ini di bawah contoh. (Klik kanan tautan untuk dibuka di tab baru.)

Modul LED

Tujuh tampilan segmen

Modul LCD

Tampilan VGA

Sensor suhu

Sensor cahaya

Tombol tekan

Slide -slide

RGB LED

Inti mitos RISC-V

Definisi papan muncul di bagian atas file fpga_includes.tlv . Seharusnya cukup mudah untuk menafsirkan parameter ini dan menambahkan papan baru dengan contoh. Pastikan juga untuk memperbarui semua daftar papan yang tersedia (yang dapat Anda temukan menggunakan git grep -i zedboard ).

Langkah -langkah di atas memperbarui lingkungan virtual saja. Aliran FPGA Build fisik adalah masalah yang berbeda dan bergantung pada platform, meskipun arus build platform-sumber terbuka tersedia, dan kami ingin menggunakannya.

Kami menyambut kontribusi Anda.

Fitur Debug Visual MakerChip digunakan untuk membuat lab FPGA virtual.

Anda juga dapat menggunakan Visual Deubg untuk memvisualisasikan logika yang berjalan di dalam FPGA.

Dengan menyusun kode Anda untuk menentukan logika FPGA Anda di TL-Verilog (yang tidak menghalangi menggunakan Verilog/SystemVerilog murni), Anda dapat menambahkan visualisasi ke logika Anda.

Berikut struktur kode sampel.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

Dokumentasi dan contoh debug visual dapat ditemukan dalam IDE MakerChip.

Instruksi langkah demi langkah terperinci disediakan di tautan ini. Kredit diberikan kepada Mayank Kabra karena membantu saya membangun bagian ini.

Demo LED: Tautan

Posting Blog

Dalam upaya kami, kami telah menemukan proyek terkait berikut. (Penampilan dalam daftar ini bukan dukungan, hanya pengakuan bahwa kami tidak sendirian.) Beri kami permintaan tarik dengan yang lain.

Pekerjaan ini telah disponsori melalui OSFPGA Foundation dan Google Summer of Code (GSOC) 2021 (dengan Silicon Foundation (Fossi) gratis dan open source sebagai organisasi payung GSOC), dengan bimbingan dari Redwood EDA, LLC, dan dengan dukungan pelatihan dari desain sistem VLSI.

Kontribusi inilah yang membuat komunitas open source menjadi kendaraan yang luar biasa untuk dipelajari, menginspirasi, dan menciptakan. Kontribusi apa pun yang Anda buat sangat dihargai . Kudos untuk mengajukan bug. Terima kasih terdalam telah memperbaikinya dan telah menyumbangkan fitur baru dan dukungan untuk papan baru.

Didistribusikan di bawah lisensi MIT. Lihat lisensi.md.