يقدم هذا المستند مختبر FPGA الظاهري. ستساعدك المستندات المنفصلة في:

ملخص

حول Makerchip

ما الذي يجعل مشروع FPGA LAB Virtual Virtual FPGA خاصًا؟

أظهرت لوحات FPGA

FPGA الطرفية الكلية

أمثلة

تصحيح بصري

كيفية إضافة لوحات FPGA الخاصة والأجهزة الطرفية

خطوات للتشغيل في FPGA الفعلي

النطاق المستقبلي

المساهمين

المساهمة

رخصة

جديد على FPGAS؟ صفائف البوابة القابلة للبرمجة (FPGAs) هي دوائر الأجهزة التي يمكن برمجتها لتنفيذ عمليات منطقية. أنها توفر بقعة حلوة بين تنفيذ الخوارزميات في البرامج وتصنيع الدوائر المتكاملة الخاصة بالتطبيق (ASIC). أنها توفر عمومًا أداءً أفضل بكثير وكفاءة الطاقة من تطبيقات البرمجيات ، وتتطلب وقتًا أقل بكثير من الوقت والنفقات لتنفيذها من ASIC. يمكن إعادة برمجتها حسب الحاجة لترقية الوظائف أو إصلاح الأخطاء ، حتى بعد النشر للعملاء (في "الحقل"). تعتبر FPGAs مفيدة أيضًا للدوائر المتكاملة الخاصة بتطبيق النماذج الأولية (ASICS) أو المعالجات.

على الرغم من أنه يمكن الوصول إليه أكثر بكثير من ASIC ، إلا أنه لا يزال من المفيد بعض الشيء ويصعب تعلمه للمبتدئين والطلاب. هذا هو المكان الذي يأتي فيه هذا المشروع ... وليس فقط للمبتدئين.

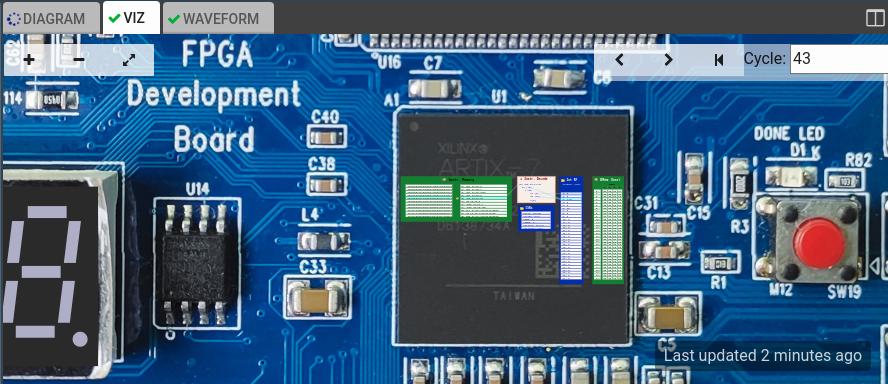

يعتمد هذا المشروع على كل قوة وسهولة استخدام MakerChip IDE ويضيف الراحة لتطوير FPGA. على وجه الخصوص ، نستفيد من ميزة التصحيح المرئي لـ MakerChip لتوفير تصورات FPGAs والأجهزة الطرفية الخاصة بها ، وبالتالي تحاكي تجربة المختبر المادي. ولكن أفضل من التجربة الفيزيائية ، لديك أيضًا فوائد التطوير القائم على المحاكاة: التجميع السريع (لا يوجد توليف ، مكان وتجارة ، و bitstreams) ، والرؤية الكاملة لجميع قيم الإشارة ، والتحكم الكامل للوقت.

يعمل MakerChip على تبسيط التجربة مع دعم TL-Verilog بالإضافة إلى Verilog/SystemVerilog. تعتبر ميزات TL-Verilog أكثر ودودة للقادمين الجدد (ناهيك عن الفوائد التي لا تعد ولا تحصى للخبراء).

في ملخص:

نوضح حاليًا استخدام هذه المجالس فقط ونخطط لإضافة المزيد من الألواح في المستقبل. يمكنك بسهولة إضافة لوحات FPGA الخاصة بك. المساهمات موضع ترحيب.

فقط انقر هنا ، واذهب! (انقر بزر الماوس الأيمن لفتح في علامة تبويب جديدة.) تعرّف الإرشادات أدناه.

يمكنك أيضًا البدء من أي من مشروع مثال هنا.

بالتناوب ، خاصة بالنسبة لاستخدام FPGA المحلي ، يمكنك استخدام تطبيق MakerChip-APP لتحرير الملفات على جهازك المحلي (حيث يمكنك الحفاظ على مستودع GIT وتشغيل تدفقات FPGA).

بمجرد قيامك ببعض المنطق في المحاكاة ، ستتمكن من تصدير التصميم الخاص بك إلى أي لوحة FPGA المادية المدعومة باستخدام هذه التعليمات.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

m4+board(...) Macro (و Mistipheral Macros ، مثل m4+lcd(...) ، تحديد الأجهزة).

يوفر m4_lab() مجموعة من الإشارات لإدخال/OS. يجب قيادة/استخدام تلك التي لديها مكونات مقابلة على اللوحة أو الأجهزة الطرفية. وتشمل هذه:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

يمكنك رؤية إعلانات الإشارات هذه في التوسع في الخط الواحد لاستئصال الماكرو m4_lab() في علامة التبويب NAV-TLV.

في قالب البداية ، يمكن استخدام الوسيطة الثالثة أدناه لتحديد اللوحة:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

تحتوي الألواح على مجموعة فرعية من المكونات التالية ،

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

يمكن إنشاء مثيل للأجهزة الطرفية الخارجية وغيرها من وحدات الماكرو m4+ .

إليك بعض الأمثلة التي يمكنك تحميلها في MakerChip. ستجد رمز المصدر في هذا المستودع ضمن أمثلة. (انقر بزر الماوس الأيمن فوق روابط لفتح في علامة تبويب جديدة.)

وحدة LED

سبعة شاشات شاشة

وحدة LCD

عرض VGA

مستشعر درجة الحرارة

مستشعر الضوء

أزرار الضغط

slideswitches

RGB LED

RISC-V الأسطورة الأساسية

تظهر تعريفات اللوحة في الجزء العلوي من ملف fpga_includes.tlv . يجب أن يكون من السهل بدرجة كافية تفسير هذه المعلمات وإضافة لوحات جديدة بالقدوة. تأكد أيضًا من تحديث جميع قوائم اللوحات المتاحة (والتي يمكنك العثور عليها باستخدام git grep -i zedboard ).

الخطوات المذكورة أعلاه تحديث البيئة الافتراضية فقط. يعد تدفق بناء FPGA المادي مسألة مختلفة ويعتمد على النظام الأساسي ، على الرغم من أن تدفقات البناء المنصوص عليها في المنصة المفتوحة متوفرة ، ونود استخدامها.

نرحب بمساهماتك.

يتم استخدام ميزة تصحيح التصحيح المرئي لـ MakerChip لإنشاء مختبر FPGA الظاهري.

يمكنك أيضًا استخدام Visual DeUBG لتصور المنطق الذي يعمل داخل FPGA.

من خلال هيكلة الكود الخاص بك لتحديد منطق FPGA الخاص بك في TL-Verilog (والذي لا يحول دون استخدام Verilog/SystemVerilog النقي) ، يمكنك إضافة التصور إلى منطقك.

إليك هيكل رمز عينة.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

يمكن العثور على وثائق التصحيح المرئي والأمثلة داخل MakerChip IDE.

يتم توفير إرشادات مفصلة خطوة بخطوة في هذا الرابط. يذهب الائتمان إلى Mayank Kabra لمساعدتي في بناء هذا الجزء.

LED Demo: Link

منشور المدونة

في جهودنا ، صادفنا المشاريع التالية ذات الصلة. (المظهر في هذه القائمة ليس تأييدًا ، مجرد اعتراف بأننا لسنا وحدنا.) أعطنا طلب سحب مع أي شخص آخر.

تم رعاية هذا العمل من خلال مؤسسة OSFPGA و Google Summer of Code (GSOC) 2021 (مع مؤسسة السيليكون المجانية والمفتوحة المصدر (FOSSI) كمنظمة مظلة GSOC) ، مع إرشادات من Redwood EDA ، LLC ، مع دعم التدريب من تصميم نظام VLSI.

المساهمات هي التي تجعل مجتمع المصدر المفتوح هذه السيارة المذهلة للتعلم وإلهامها وإنشائها. أي مساهمات تقدمها موضع تقدير كبير . مجد لتقديم الحشرات. أعمق شكر لإصلاحها والمساهمة بميزات جديدة ودعم لوحات جديدة.

موزعة تحت رخصة معهد ماساتشوستس للتكنولوجيا. انظر الترخيص.