Этот документ представляет виртуальную FPGA Lab. Отдельные документы помогут вам с:

Обзор

О MakerChip

Что делает проект виртуальной FPGA Lab Speect?

Партиты FPGA продемонстрированы

Периферические макроадциализации FPGA

Примеры

Визуальная отладка

Как добавить собственные платы FPGA и периферийные устройства

Шаги для работы в реальной FPGA

Будущая область

Участники

Внося

Лицензия

Новичок в FPGA? Полевые массивы затвора (FPGA) представляют собой аппаратные схемы, которые можно запрограммировать для выполнения логических операций. Они обеспечивают сладкое место между внедрением алгоритмов в программном обеспечении и изготовлением интегрированных цепей, специфичных для приложений (ASIC). Как правило, они обеспечивают гораздо лучшую производительность и энергоэффективность, чем реализации программного обеспечения, и они требуют гораздо меньшего времени и затрат для реализации, чем ASICS. Их можно перепрограммировать по мере необходимости для обновления функциональности или исправления ошибок, даже после развертывания для клиентов (в «поле»). FPGA также полезны для прототипирования интегрированных цепей (ASIC) или процессоров, специфичных для приложения.

Несмотря на то, что ASICS, хотя и гораздо более доступен, чем ASICS, все еще может быть немного дорогостоящим и трудно учиться для начинающих и студентов. Вот где этот проект входит ... и это не только для начинающих.

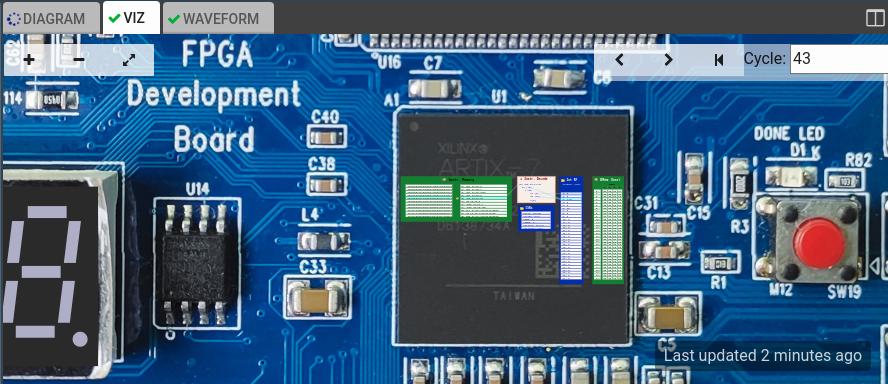

Этот проект основан на всей мощности и простоте использования MakerChip IDE и добавляет удобство для разработки FPGA. В частности, мы используем преимущества визуальной функции отладки MakerChip, чтобы обеспечить визуализации FPGA и их периферийных устройств, и тем самым имитируя физический опыт работы в лаборатории. Но лучше, чем физический опыт, у вас также есть преимущества развития на основе моделирования: быстрое компиляция (без синтеза, места и маршрутизации и бит-ремней), полной видимости всех значений сигналов и полного контроля времени.

MakerChip также упрощает опыт при поддержке TL-Verilog в дополнение к Verilog/SystemVerilog. Особенности TL-Verilog более доступны для новичков (не говоря уже о множестве преимуществ для экспертов).

В итоге:

В настоящее время мы демонстрируем использование только этих досок и планируем добавить больше плат в будущем. Вы можете очень легко добавить свои собственные доски FPGA. Взносы приветствуются.

Просто нажмите здесь, и иди! (Щелкните правой кнопкой мыши, чтобы открыть на новой вкладке.)

Вы также можете начать с любого из примера проекта здесь.

Альтернативно, особенно для локального использования FPGA, вы можете использовать MakerChip-App для редактирования файлов на вашей локальной машине (где вы можете поддерживать свой репозиторий GIT и запустить потоки FPGA).

После того, как у вас будет какая -то логика, работающая в моделировании, вы сможете экспортировать свой дизайн в любую поддерживаемую физическую плату FPGA, используя эти инструкции.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

m4+board(...) макро (и периферические макросы, такие как m4+lcd(...) , определяют аппаратное обеспечение).

m4_lab() предоставляет суперсет сигналов для I/OS. Те, у кого есть соответствующие компоненты на плате или периферийные устройства, должны быть приведены/используются. К ним относятся:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

Вы можете увидеть эти объявления сигнала в одном линии расширения макро-экземпляра m4_lab() на вкладке NAV-TLV.

В начальном шаблоне 3 -й аргумент ниже можно использовать для выбора платы:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

Доски содержат подмножество следующих компонентов,

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

Внешние и другие периферийные устройства могут быть созданы макросами UISNG m4+ .

Вот какой -то пример, который вы можете загрузить в MakerChip. Вы найдете исходный код в этом репозитории в примерах. (Щелкните правой кнопкой мыши ссылки, чтобы открыть на новой вкладке.)

Светодиодный модуль

Семь сегментных дисплеев

ЖК -модуль

VGA -дисплей

Датчик температуры

Световой датчик

Нажмите кнопки

Слайд -Смешивания

RGB LED

RISC-V Myth Core

Определения платы появляются в верхней части файла fpga_includes.tlv . Это должно быть достаточно легко интерпретировать эти параметры и добавлять новые платы по примеру. Обязательно обновите все списки доступных плат (которые вы можете найти, используя git grep -i zedboard ).

Приведенные выше шаги обновляют только виртуальную среду. Физический поток сборки FPGA-это другое дело и зависит от платформы, хотя доступны платформы с открытым исходным кодом платформы, и мы хотели бы использовать их.

Мы приветствуем ваш вклад.

Функция визуальной отладки MakerChip используется для создания виртуальной FPGA Lab.

Вы также можете использовать Visual Deubg для визуализации логики, работающей внутри FPGA.

Структурируя свой код для определения вашей логики FPGA в TL-Verilog (который не исключает, используя Pure Verilog/SystemVerilog), вы можете добавить визуализацию в свою логику.

Вот образец структуры кода.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

Документация и примеры визуальной отладки можно найти в IDE MakerChip.

Подробные пошаговые инструкции приведены в этой ссылке. Кредит доходит до Mayank Kabra за то, что он помогал мне построить эту часть.

Светодиодная демонстрация: ссылка

Пост в блоге

В наших усилиях мы столкнулись с следующими связанными проектами. (Появление в этом списке не является одобрением, просто признание того, что мы не одиноки.) Подайте нам запрос на привлечение с любыми другими.

Эта работа была спонсирована через Foundation OSFPGA и Google Summer of Code (GSOC) 2021 (с Фондом Free и с открытым исходным кодом (FOSSI) в качестве организации GSOC Uncerella), с наставничеством от Redwood Eda, LLC и с поддержкой обучения от дизайна системы VLSI.

Вклад - это то, что делает сообщество с открытым исходным кодом таким удивительным средством для изучения, вдохновления и создания. Любой вклад, которые вы вносите, высоко ценится . Престижность за подачу ошибок. Глубокая спасибо за то, что они исправят их и за то, что они внесли новые функции и поддержку для новых досок.

Распределено по лицензии MIT. Смотрите лицензию.md.