このドキュメントでは、仮想FPGAラボを紹介します。個別のドキュメントはあなたを支援します:

概要

Makerchipについて

プロジェクトが仮想FPGAラボを特別なものにしているのはなぜですか?

FPGAボードが実証されました

FPGA周辺マクロインスタンス

例

ビジュアルデバッグ

自分のFPGAボードと周辺機器を追加する方法

実際のFPGAで実行する手順

将来の範囲

貢献者

貢献

ライセンス

FPGASは初めてですか?フィールドプログラム可能なゲートアレイ(FPGA)は、論理操作を実行するようにプログラムできるハードウェア回路です。それらは、ソフトウェアでアルゴリズムを実装することと、アプリケーション固有の統合回路(ASIC)を製造する間のスイートスポットを提供します。通常、それらはソフトウェアの実装よりもはるかに優れたパフォーマンスと電力効率を提供し、ASICよりもはるかに少ない時間と費用が必要です。顧客への展開後(「フィールド」)に展開した後でも、機能性をアップグレードしたり、バグを修正するために、必要に応じて再プログラムできます。 FPGAは、アプリケーション固有の統合回路(ASIC)またはプロセッサのプロトタイピングにも有益です。

ASICよりもはるかにアクセスしやすいものの、FPGAは、初心者や学生のために少しコストがかかり、学ぶのが難しい場合があります。それがこのプロジェクトが登場する場所です...そしてそれは初心者だけのためではありません。

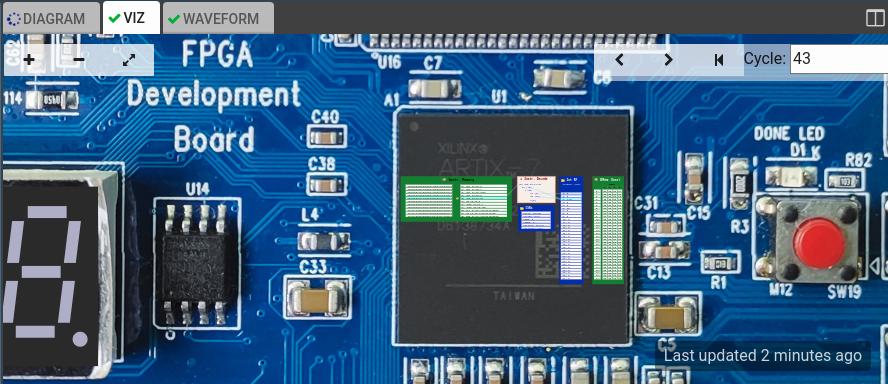

このプロジェクトは、MakerChip IDEのすべてのパワーと使いやすさに基づいており、FPGA開発の利便性を高めています。特に、MakerChipのビジュアルデバッグ機能を利用して、FPGAとその周辺機器の視覚化を提供し、それによって物理的なラボエクスペリエンスを模倣します。しかし、物理的な経験よりも優れている場合、シミュレーションベースの開発の利点もあります:高速コンパイル(合成、場所とルート、ビットストリームなし)、すべての信号値の完全な可視性、および時間の完全な制御。

MakerChipは、Verilog/SystemVerilogに加えて、TL-verilogのサポートでエクスペリエンスをさらに簡素化します。 TL-verilogの機能は、新人にとってより親しみやすいものです(専門家にとって無数の利点は言うまでもありません)。

要約すれば:

現在、これらのボードのみを使用してデモを行い、将来的にさらにボードを追加する予定です。独自のFPGAボードを簡単に追加できます。貢献は大歓迎です。

ここをクリックして行きましょう! (右クリックして新しいタブで開きます。)以下の手順では、ガイドされます。

ここでは、プロジェクトのサンプルから開始することもできます。

あるいは、特にローカルFPGAの使用の場合、MakerChip-Appを使用してローカルマシンでファイルを編集できます(Gitリポジトリを維持し、FPGAフローを実行できます)。

シミュレーションでいくつかのロジックを実行したら、これらの指示を使用してサポートされている物理FPGAボードにデザインをエクスポートできます。

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

m4+board(...)マクロ(およびm4+lcd(...)などの周辺マクロがハードウェアを定義します)。

m4_lab() I/OSの信号のスーパーセットを提供します。ボードまたは周辺機器に対応するコンポーネントがあるものは、駆動/使用する必要があります。これらには以下が含まれます:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

これらの信号宣言は、NAV-TLVタブでm4_lab()マクロインスタンス化の一つの拡張で見ることができます。

開始テンプレートでは、以下の3番目の引数を使用してボードを選択できます。

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

ボードには、次のコンポーネントのサブセットが含まれています。

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

外部およびその他の周辺機器は、uisng m4+マクロをインスタンス化できます。

MakerChipにロードできる例を以下に示します。このリポジトリには、例の下にソースコードがあります。 (リンクを右クリックして新しいタブで開きます。)

LEDモジュール

7つのセグメントディスプレイ

LCDモジュール

VGAディスプレイ

温度センサー

光センサー

ボタンを押します

スライドスイッチ

RGB LED

RISC-V Myth Core

ボードの定義は、 fpga_includes.tlvファイルの上部に表示されます。これらのパラメーターを解釈し、例で新しいボードを追加するのに十分簡単でなければなりません。また、利用可能なボードのすべてのリストを更新してください( git grep -i zedboardを使用して見つけることができます)。

上記の手順では、仮想環境のみを更新します。物理FPGAビルドフローは別の問題であり、プラットフォーム依存ですが、オープンソースプラットフォームに依存しないビルドフローが利用可能であるため、それらを使用したいと考えています。

貢献を歓迎します。

MakerChipのVisual Debug機能は、仮想FPGAラボを作成するために使用されます。

Visual Deubgを使用して、FPGA内で実行されているロジックを視覚化することもできます。

TL-verilogでFPGAロジックを定義するためにコードを構成することにより(純粋なVerilog/systemverilogの使用を妨げない)、ロジックに視覚化を追加できます。

これがサンプルコード構造です。

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

ビジュアルデバッグのドキュメントと例は、MakerChip IDE内にあります。

このリンクには、詳細なステップバイステップの指示が提供されています。クレジットは、私がこの部分を構築するのを手伝ってくれたマヤンク・カブラに送られます。

LEDデモ:リンク

ブログ投稿

私たちの取り組みにおいて、私たちは次の関連するプロジェクトに出くわしました。 (このリストの外観は承認ではなく、私たちが一人ではないという認識だけです。)他の人とのプルリクエストを教えてください。

この作業は、OSFPGA財団とGoogle Summer of Code(GSOC)2021(GSOC Umbrella組織として無料およびオープンソースのシリコン財団(Fossi)を介して、Redwood EDA、LLCのメンターシップを備えており、VLSIシステム設計からのトレーニングサポートを提供しています。

貢献は、オープンソースコミュニティを学び、インスピレーションを与え、作成するための素晴らしい手段にするものです。あなたがする貢献はどんな貢献も大歓迎です。バグを提出するための称賛。それらを修正し、新しい機能と新しいボードのサポートを提供してくれてありがとう。

MITライセンスの下で配布されます。 license.mdを参照してください。