Ce document présente le laboratoire FPGA virtuel. Des documents séparés vous aideront avec:

Aperçu

À propos de Makerchip

Qu'est-ce qui rend le projet Virtual FPGA Lab spécial?

Les conseils FPGA ont été démontrés

FPGA Macro instanciations périphériques

Exemples

Débogage visuel

Comment ajouter leurs propres planches FPGA et périphériques

Étapes pour fonctionner dans un FPGA réel

Portée future

Contributeurs

Contributif

Licence

Nouveau sur les FPGA? Les réseaux de portes programmables sur le terrain (FPGA) sont des circuits matériels qui peuvent être programmés pour effectuer des opérations logiques. Ils fournissent un point idéal entre la mise en œuvre d'algorithmes dans les logiciels et la fabrication de circuits intégrés spécifiques à l'application (ASIC). Ils offrent généralement de bien meilleures performances et efficacité électrique que les implémentations logicielles, et ils nécessitent beaucoup moins de temps et de dépenses à mettre en œuvre que les ASIC. Ils peuvent être reprogrammés au besoin pour mettre à niveau les fonctionnalités ou corriger les bogues, même après le déploiement aux clients (dans le "champ"). Les FPGA sont également bénéfiques pour le prototypage des circuits intégrés spécifiques à l'application (ASIC) ou des processeurs.

Bien que bien plus accessibles que les ASIC, les FPGA peuvent toujours être un peu coûteux et difficiles à apprendre pour les débutants et les étudiants. C'est là que ce projet arrive ... et ce n'est pas seulement pour les débutants.

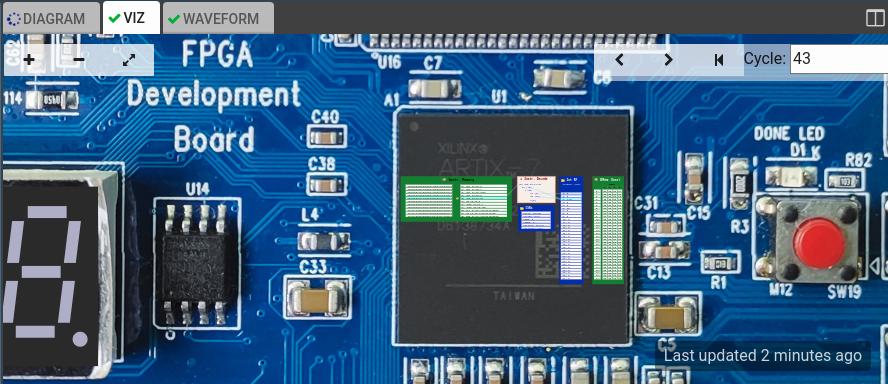

Ce projet s'appuie sur toute la puissance et la facilité d'utilisation de MakerChip IDE et ajoute la commodité du développement FPGA. En particulier, nous profitons de la fonctionnalité de débogage visuel de MakerChip pour fournir des visualisations des FPGA et de leurs périphériques, imitant ainsi l'expérience de laboratoire physique. Mais mieux que l'expérience physique, vous avez également les avantages du développement basé sur la simulation: compilation rapide (pas de synthèse, place et route et courants de bits), visibilité complète de toutes les valeurs du signal et contrôle total du temps.

MakerChip simplifie davantage l'expérience avec le support de Tl-Verilog en plus de Verilog / SystemVerilog. Les fonctionnalités TL-Verilog sont plus accessibles aux nouveaux arrivants (sans parler des innombrables avantages pour les experts).

En résumé:

Actuellement, nous démontrons en utilisant uniquement ces planches et nous prévoyons d'ajouter plus de planches à l'avenir. Vous pouvez très facilement ajouter vos propres cartes FPGA. Les contributions sont les bienvenues.

Cliquez ici et allez! (Cliquez avec le bouton droit pour ouvrir dans un nouvel onglet.) Les instructions ci-dessous vous guideront.

Vous pouvez également commencer à partir de l'un des exemples de projets ici.

Alternativement, en particulier pour l'utilisation de FPGA locale, vous pouvez utiliser MakerChip-App pour modifier des fichiers sur votre machine locale (où vous pouvez maintenir votre référentiel GIT et exécuter les flux FPGA).

Une fois que vous avez une logique en cours de simulation, vous serez en mesure d'exporter votre conception vers n'importe quelle carte FPGA physique prise en charge en utilisant ces instructions.

m4_TLV_version 1d: tl-x.org

SV

m4_include_lib(['https://raw.githubusercontent.com/BalaDhinesh/Virtual-FPGA-Lab/main/tlv_lib/fpga_includes.tlv'])

m4_lab()

// ... SystemVerilog or TL-Verilog FPGA logic goes here ...

TLV

/board

// Board selection:

// 0: M4_FIRST_CLAAS_ID

// 1: M4_ZEDBOARD_ID

// 2: M4_ARTIX7_ID

// 3: M4_BASYS3_ID

// 4: M4_ICEBREAKER_ID

// 5: M4_NEXYS_ID

// 6: M4_CLEAR_ID

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

SV

endmodule

La macro m4+board(...) (et les macros périphériques, telles que m4+lcd(...) , définissent le matériel).

m4_lab() fournit un superset de signaux pour les E / OS. Ceux qui ont des composants correspondants sur la carte ou les périphériques doivent être entraînés / utilisés. Ceux-ci incluent:

logic [15:0] led; // corresponding LEDs are lit when asserted

logic [6:0] sseg_segment_n; // corresponding segments are lit for selected digit(s) when deasserted

logic sseg_decimal_point_n; // decimal point is lit for selected digit(s) when deasserted

logic [7:0] sseg_digit_n; // corresponding digits are enabled when deasserted

Vous pouvez voir ces déclarations de signal dans l'expansion d'une ligne de l'instanciation macro m4_lab() dans l'onglet NAV-TLV.

Dans le modèle de départ, le 3ème argument ci-dessous peut être utilisé pour sélectionner la carte:

// Board selection:

// 0 - 1st CLaaS on AWS F1

// 1 - Zedboard

// 2 - Artix-7

// 3 - Basys3

// 4 - Icebreaker

// 5 - Nexys

// 6 - CLEAR

m4+board(/board, /fpga, 3, *) // 3rd arg selects the board.

Les cartes contiennent un sous-ensemble des composants suivants,

// Internal to FPGA - no need to instantiate

// Signals:

// *led - led signal

// Internal to FPGA - no need to instantiate

// Signals:

// *sseg_digit_n - common anode signal

// *sseg_segment_n - seven segments

// *sseg_decimal_point_n - decimal point

// Internal to FPGA - no need to instantiate

// Signals:

// *push - push button signal

// Internal to FPGA - no need to instantiate

// Signals:

// *slideswitch - switch signal

// External to FPGA - instantiated using

m4+fpga_lcd()

// Signals:

// *out - 8-bit data/command line

// *lcd_enable - lcd enable signal

// *lcd_reset - lcd reset signal, 0 for command and 1 for data

// External to FPGA - instantiated using

m4+fpga_vga()

// Signals:

// *vga_hsync - horizontal sync

// *vga_vsync - vertical sync

// *vga_r - red signal

// *vga_g - green signal

// *vga_b - blue signal

Les périphériques externes et autres peuvent être instanciés des macros Uisng m4+ .

Voici quelques exemples que vous pouvez charger dans MakerChip. Vous trouverez le code source de ce référentiel sous des exemples. (Cliquez avec le bouton droit sur les liens à ouvrir dans un nouvel onglet.)

Module LED

Sept affichages segments

Module LCD

Affichage VGA

Capteur de température

Capteur léger

Boutons appuyés

Glissade

RVB LED

RISC-V Myth Core

Les définitions de la carte apparaissent en haut du fichier fpga_includes.tlv . Il devrait être assez facile d'interpréter ces paramètres et d'ajouter de nouvelles cartes par exemple. Assurez-vous également de mettre à jour toutes les listes des cartes disponibles (que vous pouvez trouver à l'aide de git grep -i zedboard ).

Les étapes ci-dessus mettent à jour l'environnement virtuel uniquement. Le flux de build FPGA physique est une question différente et dépend de la plate-forme, bien que des flux de construction en plate-forme open-source-agnostique soient disponibles, et nous serions ravis de les utiliser.

Nous accueillons vos contributions.

La fonction de débogage visuel de MakerChip est utilisée pour créer le laboratoire VPGA virtuel.

Vous pouvez également utiliser Visual Deubg pour visualiser la logique en cours d'exécution à l'intérieur du FPGA.

En structurant votre code pour définir votre logique FPGA dans TL-Verilog (qui n'empêche pas d'utiliser Pure Verilog / SystemVerilog), vous pouvez ajouter une visualisation à votre logique.

Voici un exemple de structure de code.

...

SV

m4_lab()

TLV my_fpga_logic(/_fpga)

// ... Your TL-Verilog FPGA logic along with it's visualization ...

TLV

/board

m4+board(/board, /fpga, 3, *, , my_fpga_logic)

...

La documentation et des exemples de débogage visuel peuvent être trouvés dans l'IDE MakerChip.

Des instructions détaillées étape par étape sont fournies dans ce lien. Le crédit va à Mayank Kabra pour m'avoir aidé à construire cette partie.

Demo LED: lien

Article de blog

Dans nos efforts, nous avons rencontré les projets connexes suivants. (L'apparition sur cette liste n'est pas une approbation, juste une reconnaissance que nous ne sommes pas seuls.) Donnez-nous une demande de traction avec d'autres.

Ce travail a été parrainé par le biais de la Fondation OSFPGA et de Google Summer of Code (GSOC) 2021 (avec la Fondation gratuite et open source de Silicon (FOSSI) en tant qu'organisation parapluie de GSOC), avec le mentorat de Redwood Eda, LLC, et avec le soutien de la formation de la conception du système VLSI.

Les contributions font de la communauté open source un véhicule si étonnant pour apprendre, inspirer et créer. Toutes les contributions que vous faites sont grandement appréciées . Félicitations pour le dépôt de bogues. Merci les plus profonds de les avoir réparés et d'avoir contribué de nouvelles fonctionnalités et de support pour de nouveaux conseils.

Distribué sous la licence du MIT. Voir Licence.Md.