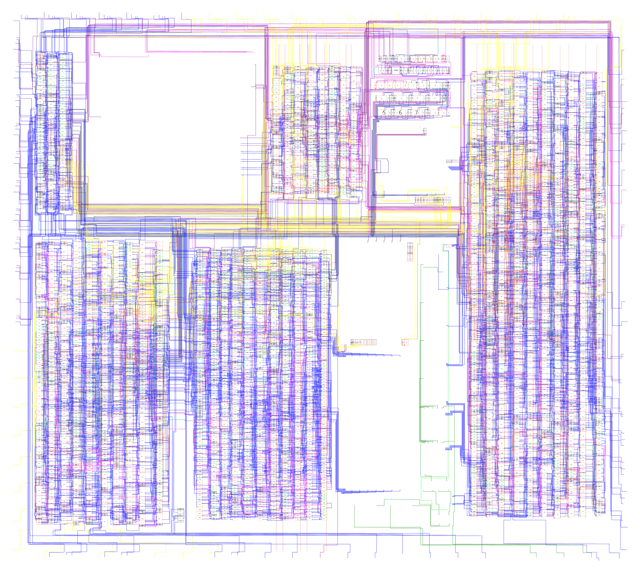

Ce dépôt contient une superposition annotée pour le jeu de puce Nintendo Game Boy DMG-CPU-B et les schémas extraits.

Cela a été fait manuellement avec seulement quelques chèques automatisés , il y a donc un risque élevé d'erreur . Je ne suis en aucun cas responsable si vous avez fait en sorte que la vie de quelqu'un en dépendait et que cela a foutu.

Il suffit de lire les schémas :)

Si vous souhaitez utiliser la superposition:

Les NET nommés FROM_CPU* et TO_CPU sont connectés au noyau du CPU mais ne sont pas clairement identifiés. Beaucoup d'entre eux sont déclencheurs et reconnaissent des signaux pour les interruptions. D'autres peuvent être des indicateurs d'État comme le Z80 / M1 ou Halt.

Certaines polarités d'horloge DFF doivent être vérifiées.

Les registres de décalage parallèle dans la série utilisée pour la liaison série et le rendu vidéo sont faits de chaînes de DFF compatibles à réinstallation. Leur logique de chargement nécessite beaucoup de cellules et semblent complexes, mais à la fin, elle forme quelque chose de assez simple.

Plutôt que d'utiliser des multiplexeurs, de nombreux bus internes sont plutôt capables à trois états. Les cellules "Tribuffer" sont largement utilisées pour cela.

Il est bien connu par les auteurs d'émulateurs que le Game Boy est plein de bizarreries. Savoir exactement comment et quand les signaux changent peuvent aider à atteindre une précision parfaite.

Parce que j'ai utilisé un logiciel de CAO propriétaire pour la vitesse et que je n'ai pas fini de faire le convertisseur pour le format Kicad. J'espère pouvoir le faire bientôt.

Ce sont des noms uniques aléatoires. La première lettre correspond à la colonne dans laquelle ils sont sur la mort du silicium.

Je n'ai pas pris la peine de tracer les lignes de ramification lorsque leur point final était assez proche pour le voir sur mon écran de 15 "au niveau du zoom que j'ai utilisé. Ils sont signalés sur le schéma, bien sûr.

C'est une façon de compromettre l'espace pour la vitesse, cela semble bizarre mais c'est utile. Recherchez la "duplication logique".

Jusqu'à ce que je fasse exporter les fichiers au format Kicad, veuillez ouvrir un problème et décrire ce qui ne va pas (nom de la cellule, nom de filet, position sur Die, ...).

J'ai dû faire des suppositions. Les entrées et les sorties sont facilement identifiées et la taille de la cellule donne quelques indices. Lorsque des connexions sont établies sur le schéma, cela devient rapidement évident lorsqu'une supposition est fausse. Découvrez le Zoo Cell.

L'identification des cellules, les isoler, le traçage des connexions et les schémas ont pris 191 heures.

Si vous le trouvez en vaut la peine, j'accepte les dons via PayPal: paypal.me/furrtek

Merci à Gekkio, Tanjent et Kevin Murphy pour l'aide.