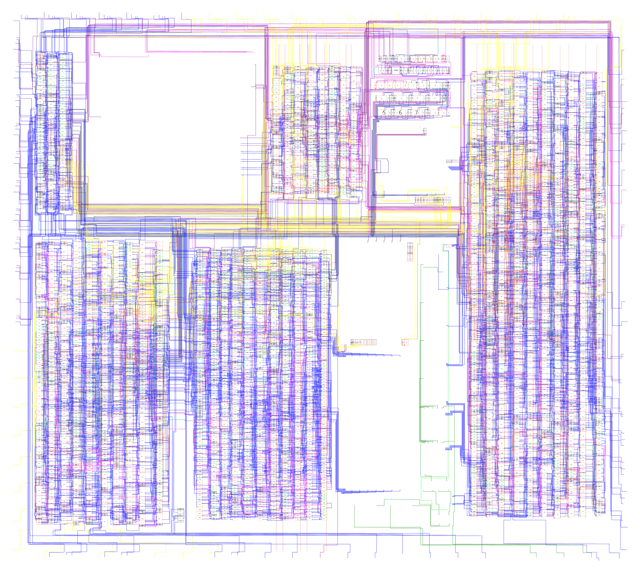

Dieses Repo enthält eine kommentierte Overlay für den Nintendo Game Boy DMG-CPU-B-Chip-Würfel und die extrahierte Schematik.

Dies wurde manuell mit nur wenigen automatisierten Schecks durchgeführt, sodass ein hohes Fehlerrisiko besteht . Ich bin in keiner Weise verantwortlich, wenn du das Leben eines Menschen davon abhängt und es versaut hat.

Lesen Sie einfach die Schemata :)

Wenn Sie das Overlay verwenden möchten:

Nets FROM_CPU* und TO_CPU werden mit dem CPU -Kern verbunden, sind jedoch nicht eindeutig identifiziert. Viele von ihnen sind Auslöser und erkennen Signale für Interrupts an. Andere können Staatsindikatoren wie Z80 /M1 oder Halt sein.

Einige DFF -Uhr -Polaritäten müssen überprüft werden.

Die für die serielle Verbindung und Video-Renderung verwendeten Verschiebungsregister der Parallel-in-serial-out-Out bestehen aus Ketten von Set-Reseet-fähigen DFFs. Ihre Ladelogik erfordern viele Zellen und wirkt komplex, aber am Ende bildet sie etwas ganz Einfaches.

Anstatt Multiplexer zu verwenden, sind viele interne Busse stattdessen Tri-State-fähig. Die "Tribuffer" -Zellen werden dafür ausgiebig verwendet.

Die Emulatorautoren sind bekannt, dass der Game Boy voller Macken ist. Wenn Sie genau wissen, wie und wann Signale sich ändern, können Sie eine perfekte Genauigkeit erreichen.

Weil ich eine proprietäre CAD -Software für Geschwindigkeit verwendet habe und den Konverter für das Kicad -Format nicht fertiggestellt habe. Ich hoffe, dass ich das bald tun kann.

Sie sind zufällige, eindeutige Namen. Der erste Buchstabe entspricht der Säule, in der sie sich auf dem Siliziumstempel befinden.

Ich habe mich nicht darum gekümmert, Verzweigungsleitungen zu verfolgen, als ihr Endpunkt nahe genug war, um ihn auf meinem 15 -Zoll -Bildschirm auf der von mir verwendeten Zoomebene zu sehen. Sie werden natürlich auf dem Schema gemeldet.

Es ist eine Möglichkeit, den Raum für Geschwindigkeit zu vertiefen, es erscheint seltsam, aber es ist nützlich. Schauen Sie nach "Logik Duplikation".

Bis ich die Dateien im KICAD -Format exportieren lasse, öffnen Sie bitte ein Problem und beschreiben, was falsch ist (Zellname, Netzname, Position auf Die ...).

Ich musste Vermutungen erraten. Eingänge und Ausgänge sind leicht zu identifizieren und die Zellgröße ergibt einige Hinweise. Wenn Verbindungen zum Schema hergestellt werden, wird schnell klar, wenn eine Vermutung falsch ist. Schauen Sie sich den Cell Zoo an.

Die Identifizierung der Zellen, die Isolierung, die Verfolgung der Verbindungen und die Schaltpläne dauerte 191 Stunden.

Wenn Sie es wert finden, akzeptiere ich Spenden über PayPal: paypal.me/furrtek

Vielen Dank an Gekkio, Tanjent und Kevin Murphy für die Hilfe.