Oreboot是Coreboot的下游叉,IE Oreboot是沒有“ C”的Coreboot。

Oreboot主要用Rust編寫,需要在需要的地方組裝。

Oreboot當前僅計劃支持Linuxboot有效載荷。

oreboot ?

v 13

cpu_pll fa001000

cpu_axi 5000100

cpu_axi 5000100

peri0_ctrl was: f8216300

peri0_ctrl lock en

peri0_ctrl PLLs

peri0_ctrl set: f8216300

DDR3@792MHz

test OK

512M ?

NOR flash: c2/2018

load 00018000 bytes to 40000000: ➡️.

load 00fc0000 bytes to 44000000: ➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️.

load 00010000 bytes to 41a00000: ➡️.

{ɕ serial uart0 initialized

RISC-V vendor 5b7 arch 0 imp 0

==== platform CSRs ====

MXSTATUS c0408000

MHCR 00000109

MCOR 00000002

MHINT 00004000

see C906 manual p581 ff

=======================

Set up extension CSRs

==== platform CSRs ====

MXSTATUS c0638000

MHCR 0000017f

MCOR 00000003

MHINT 0000610c

see C906 manual p581 ff

=======================

timer init

reset init

ipi init

RustSBI version 0.3.1

.______ __ __ _______.___________. _______..______ __

| _ | | | | / | | / || _ | |

| |_) | | | | | | (----`---| |----`| (----`| |_) || |

| / | | | | | | | _ < | |

| | ----.| `--' |.----) | | | .----) | | |_) || |

| _| `._____| ______/ |_______/ |__| |_______/ |______/ |__|

Platform Name: T-HEAD Xuantie Platform

Implementation: oreboot version 0.1.0

[rustsbi] misa: RV64ACDFIMSUVX

[rustsbi] mideleg: ssoftstimersext (0x222)

[rustsbi] medeleg: imaialmalasmasauecallipagelpagespage(0xb1f3)

[rustsbi] mie: msoft ssoft mtimer stimer mext sext (00000aaa)

PMP0 0x0 - 0x40000000 (A,R,W,X)

PMP1 0x40000000 - 0x40200000 (A,R)

PMP2 0x40200000 - 0x80000000 (A,R,W,X)

PMP3 0x80000000 - 0x80200000 (A,R)

PMP4 0x80200000 - 0xfffff800 (A,R,W,X)

PMP8 0x0 - 0x0 (A,R,W,X)

DTB looks fine, yay!

Decompress 12375521 bytes from 0x44000004 to 0x40200000, reserved 25165824 bytes

Success, decompressed 21910144 bytes :)

Payload looks like Linux Image, yay!

DTB still fine, yay!

Handing over to SBI, will continue at 0x40200000

enter supervisor at 40200000 with DTB from 41a00000

...

[ 0.000000] OF: fdt: Ignoring memory range 0x40000000 - 0x40200000

[ 0.000000] Machine model: Sipeed Lichee RV Dock

[ 0.000000] earlycon: sbi0 at I/O port 0x0 (options '')

[ 0.000000] printk: bootconsole [sbi0] enabled

[ 0.000000] Zone ranges:

[ 0.000000] DMA32 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Normal empty

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] riscv: SBI specification v1.0 detected

[ 0.000000] riscv: SBI implementation ID=0x4 Version=0x301

[ 0.000000] riscv: SBI TIME extension detected

[ 0.000000] riscv: SBI IPI extension detected

[ 0.000000] riscv: SBI SRST extension detected

[ 0.000000] riscv: base ISA extensions acdfim

[ 0.000000] riscv: ELF capabilities acdfim

[ 0.000000] percpu: Embedded 17 pages/cpu s31912 r8192 d29528 u69632

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 128520

[ 0.000000] Kernel command line: console=tty0 console=ttyS0,115200 loglevel=7 earlycon=sbi

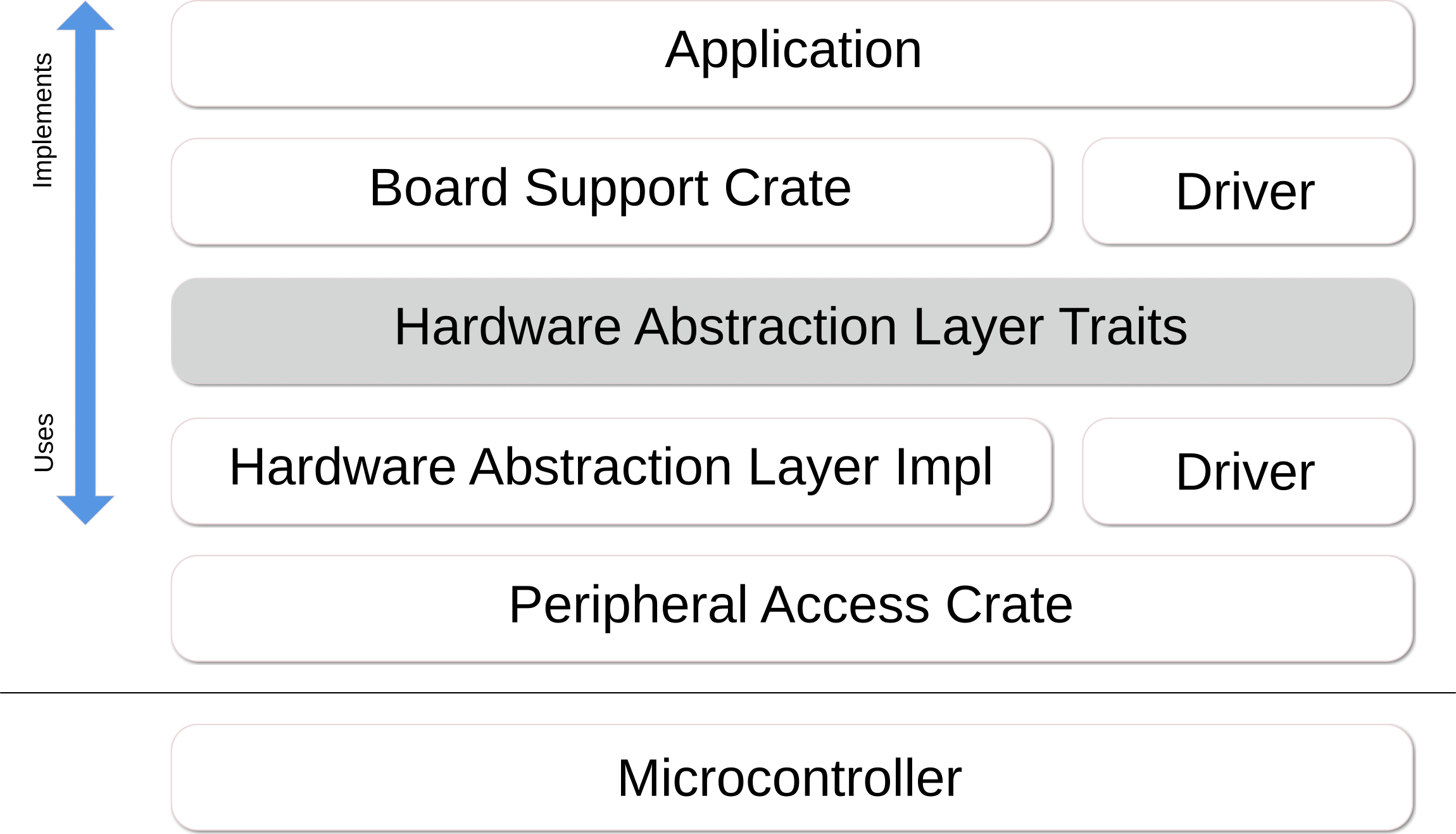

我們以其板條箱和特徵為基礎,基於Rust嵌入式工作組模型的抽像作用,這些模型在他們的書中詳細介紹了。

簡而言之:

期望SOC供應商為其內核,外圍設備以及其他塊和/或其SVD文件提供文檔,以便我們可以生成PAC和HAL Crates,或者理想情況下,供應商也應提供和維護這些文件。

Rust Embeded Book提供了設計模式和實施指南,以及詞彙表,以了解結構。

為了一般了解一般工作中的礦床和固件,請查看引導流文檔。它描述瞭如何存儲固件並將其啟動在平台 / SOC上。

請注意,Oreboot並非旨在變成自己的操作系統。因此,我們打算保持驅動程序低的數量和功能。但是,根據SOC的設計,我們必須實施一些東西來加載代碼:

在許多情況下,無需完整的驅動程序,因為我們只需要從存儲中讀取,而我們不需要豐富的文件系統。為了避免與操作系統的需求和細節相撞,我們建議明確分別將存放固件和操作系統的存儲零件分開。例如,將固件放入SPI閃光燈中,將操作系統放在NVME SSD上。

克隆此存儲庫並輸入其目錄,即:

git clone https://github.com/oreboot/oreboot.git

cd oreboot通常,您需要安裝以下軟件包:

device-tree-compilerpkg-configlibsslrustup對於基於Debian的系統,有一個可以安裝這些目標的目標,該目標可以從https://sh.rustup.rs curl拉出rustup :

make debiansysprepare否則,通過系統軟件包管理器安裝軟件包。

無論您使用哪種操作系統,您都需要為Oreboot安裝工具鏈。此命令只需要一次完成一次,但是可以重複執行此命令。

make firsttime每次您開始與Oreboot甚至每天一起工作時:

cd oreboot

make update在報告任何問題之前,您絕對應該這樣做。

項目中有兩件事:

src/mainboards/*實際目標;這些依賴並共享板條箱,這些箱子可以是驅動程序,SOC Init代碼以及類似的。對於主板,必須跟踪Cargo.lock 。src/*其他一切;這些是上述板條箱,為此,我們不跟踪Cargo.lock 。在成功構建時檢查主板的Cargo.lock 。 lock文件記錄其依賴關係的狀態,從而可重複可重複。理想情況下,鎖定文件已更新,在硬件上成功啟動。

有關更多信息,請參見:https://doc.rust-lang.org/cargo/faq.html#why-do-binaries-have-have-cargolock-cargolock-in-version-contion-control-control-control control but-not-libraries

創建新的主板時,查看如何為同一體系結構設置其他主板是一個良好的開始。請注意,Oreboot是針對裸金屬的,因此沒有標準庫。

要為特定平台構建Oreboot,請執行此操作:

# Go to the mainboard's directory

cd src/mainboard/sunxi/nezha

# Build the mainboard target

make mainboard

# View disassembly

make objdump

# Run from RAM without flashing

make run

# Flash to the board

make flash

Root Makefile允許您快速構建所有平台:

# build all mainboards

make mainboards

# build everything in parallel

make -j mainboards

# Install QEMU for your target platform, e.g. x86

sudo apt install qemu-system-x86

# Build release build and start with QEMU

cd src/mainboard/emulation/qemu-q35 && make run

# Quit qemu with CTRL-A X

從RISC-V來源構建QEMU:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-riscv64 && cd build-riscv64

../configure --target-list=riscv64-softmmu

make -j$(nproc)

# QEMU binary is at riscv64-softmmu/qemu-system-riscv64

從Aarch64的來源構建QEMU:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-aarch64 && cd build-aarch64

../configure --target-list=aarch64-softmmu

make -j$(nproc)

# QEMU binary is at aarch64-softmmu/qemu-system-aarch64

與CoreBoot類似,Oreboot中的結構是每個供應商和主板。分別支持多個體系結構和SOC,並且在董事會之間共享它們的共同代碼。如果較小的偏差否則會導致代碼重複過多,則董事會可能會有變化。

qemu-riscv作為參考,記錄了早期的方法。看看X86和ARM平台和主板的那些。

較早的仿真目標已停放在src.broken/mainboard/emulation/ 。他們應該對Oreboot尋求支持的每種體系結構提供一般的理解:

qemu-armv7qemu-aarch64qemu-q35Makefile S必須很簡單。使用xtask代替控制流,例如,將標題或校驗和添加到二進製文件,sitching圖像等。src/mainboard/$VENDOR/$BOARD (sub)目錄中的Cargo.toml允許特定於董事會的依賴項並並行構建所有階段。make format自動形式,沒有例外。 CI檢查將確定更改是否不遵守格式規則。Oreboot的版權歸大量的個人開發商和公司擁有。請檢查各個源文件以獲取詳細信息。

Oreboot已根據GNU通用公共許可證(GPL)的條款獲得許可。某些文件在“ GPL(版本2或任何後期版本)”下獲得許可,並且某些文件在“ GPL,版本2”下許可。對於某些來自其他項目的零件,其他(與GPL兼容的)許可可能適用。請檢查各個源文件以獲取詳細信息。

這使得由GPL版本2下的生成的牛仔圖像。