OreBootはCoreBootの下流のフォークです。つまり、Orebootは「C」のないCoreBootです。

鉱石は主に錆で書かれており、必要に応じてアセンブリがあります。

現在、OrebootはLinuxbootペイロードをサポートする予定です。

oreboot ?

v 13

cpu_pll fa001000

cpu_axi 5000100

cpu_axi 5000100

peri0_ctrl was: f8216300

peri0_ctrl lock en

peri0_ctrl PLLs

peri0_ctrl set: f8216300

DDR3@792MHz

test OK

512M ?

NOR flash: c2/2018

load 00018000 bytes to 40000000: ➡️.

load 00fc0000 bytes to 44000000: ➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️.

load 00010000 bytes to 41a00000: ➡️.

{ɕ serial uart0 initialized

RISC-V vendor 5b7 arch 0 imp 0

==== platform CSRs ====

MXSTATUS c0408000

MHCR 00000109

MCOR 00000002

MHINT 00004000

see C906 manual p581 ff

=======================

Set up extension CSRs

==== platform CSRs ====

MXSTATUS c0638000

MHCR 0000017f

MCOR 00000003

MHINT 0000610c

see C906 manual p581 ff

=======================

timer init

reset init

ipi init

RustSBI version 0.3.1

.______ __ __ _______.___________. _______..______ __

| _ | | | | / | | / || _ | |

| |_) | | | | | | (----`---| |----`| (----`| |_) || |

| / | | | | | | | _ < | |

| | ----.| `--' |.----) | | | .----) | | |_) || |

| _| `._____| ______/ |_______/ |__| |_______/ |______/ |__|

Platform Name: T-HEAD Xuantie Platform

Implementation: oreboot version 0.1.0

[rustsbi] misa: RV64ACDFIMSUVX

[rustsbi] mideleg: ssoftstimersext (0x222)

[rustsbi] medeleg: imaialmalasmasauecallipagelpagespage(0xb1f3)

[rustsbi] mie: msoft ssoft mtimer stimer mext sext (00000aaa)

PMP0 0x0 - 0x40000000 (A,R,W,X)

PMP1 0x40000000 - 0x40200000 (A,R)

PMP2 0x40200000 - 0x80000000 (A,R,W,X)

PMP3 0x80000000 - 0x80200000 (A,R)

PMP4 0x80200000 - 0xfffff800 (A,R,W,X)

PMP8 0x0 - 0x0 (A,R,W,X)

DTB looks fine, yay!

Decompress 12375521 bytes from 0x44000004 to 0x40200000, reserved 25165824 bytes

Success, decompressed 21910144 bytes :)

Payload looks like Linux Image, yay!

DTB still fine, yay!

Handing over to SBI, will continue at 0x40200000

enter supervisor at 40200000 with DTB from 41a00000

...

[ 0.000000] OF: fdt: Ignoring memory range 0x40000000 - 0x40200000

[ 0.000000] Machine model: Sipeed Lichee RV Dock

[ 0.000000] earlycon: sbi0 at I/O port 0x0 (options '')

[ 0.000000] printk: bootconsole [sbi0] enabled

[ 0.000000] Zone ranges:

[ 0.000000] DMA32 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Normal empty

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] riscv: SBI specification v1.0 detected

[ 0.000000] riscv: SBI implementation ID=0x4 Version=0x301

[ 0.000000] riscv: SBI TIME extension detected

[ 0.000000] riscv: SBI IPI extension detected

[ 0.000000] riscv: SBI SRST extension detected

[ 0.000000] riscv: base ISA extensions acdfim

[ 0.000000] riscv: ELF capabilities acdfim

[ 0.000000] percpu: Embedded 17 pages/cpu s31912 r8192 d29528 u69632

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 128520

[ 0.000000] Kernel command line: console=tty0 console=ttyS0,115200 loglevel=7 earlycon=sbi

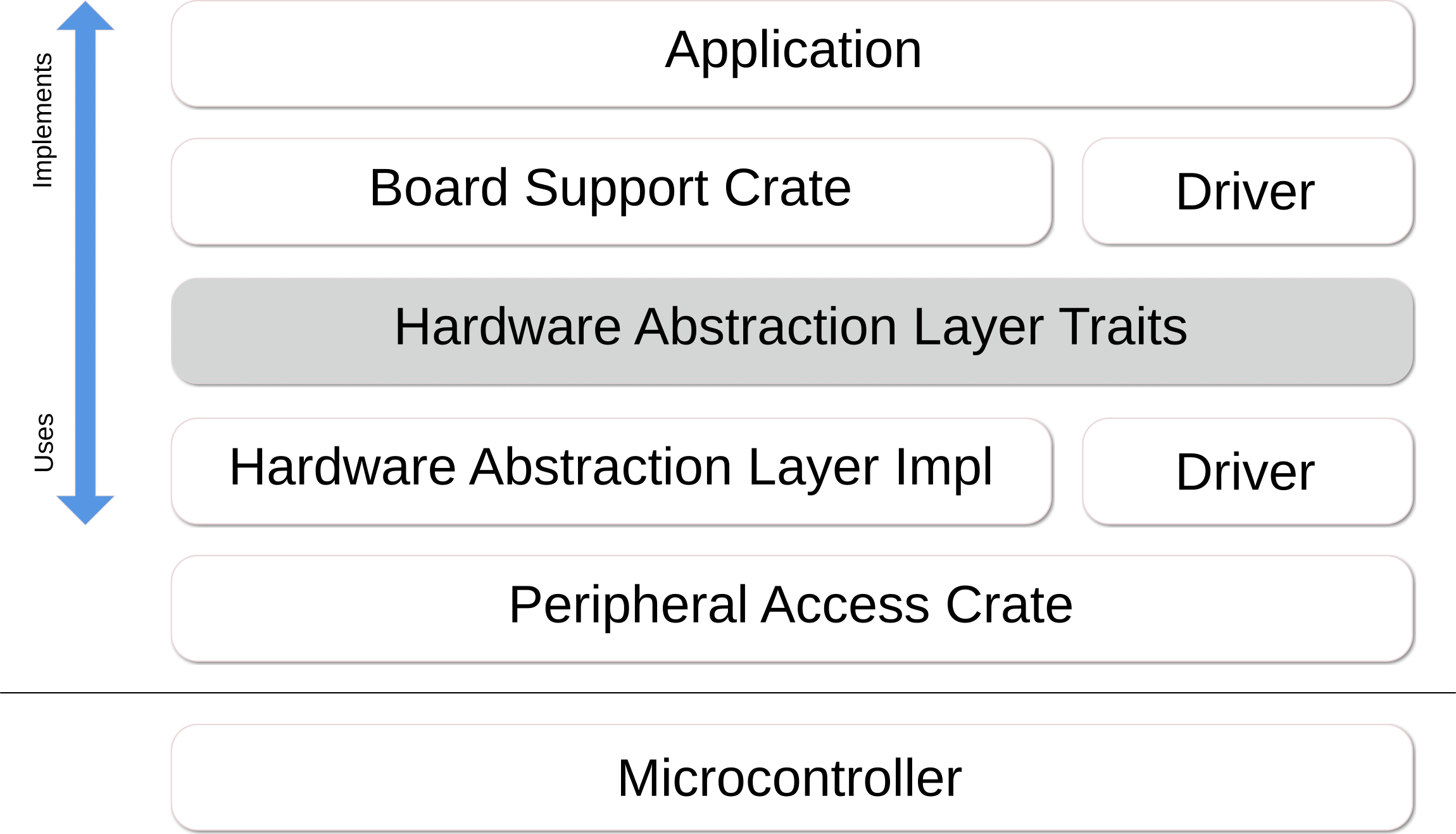

私たちは、本の中で詳述されているrust埋め込まれたワーキンググループのモデルからの抽象化の上に構築されています。

一言で言えば:

SOCベンダーは、PACとHALクレート、または理想的にはベンダーもそれらを提供および維持できるように、コア、周辺機器、その他のブロック、および/またはSVDファイルにドキュメントを提供することが期待されています。

錆びた本は、設計パターンと実装ガイドライン、および構造を理解するための用語集を提供します。

一般的なオレブットとファームウェアがどのように機能するかを一般的に理解するには、ブートフロードキュメントをご覧ください。ファームウェアがどのように保存され、プラットフォーム / SOCで起動するかについて説明します。

Orebootは独自のオペレーティングシステムに変わることを目指していないことに注意してください。したがって、ドライバーの量と機能を低く保つつもりです。ただし、SOCSの設計により、コードをロードするために何かを実装する必要があります。

多くの場合、ストレージから読むだけで、リッチなファイルシステムが必要であるため、完全なドライバーは必要ありません。 OSのニーズと詳細との衝突を避けるために、それぞれファームウェアとオペレーティングシステムを保持しているストレージ部品を明確に分離することをお勧めします。たとえば、ファームウェアをSPIフラッシュに、OSをNVME SSDに入れます。

このリポジトリをクローンして、そのディレクトリを入力します。

git clone https://github.com/oreboot/oreboot.git

cd oreboot一般に、次のパッケージをインストールする必要があります。

device-tree-compilerpkg-configlibsslrustup Debianベースのシステムの場合、それらをインストールするためのメーカーターゲットがあります。これにより、https://sh.rustup.rsからカールを介してrustupを引きます:

make debiansysprepareそれ以外の場合は、システムパッケージマネージャーからパッケージをインストールします。

OSに関係なく、Oreboot用のツールチェーンをインストールする必要があります。このコマンドは1回だけ行う必要がありますが、繰り返し行うのは安全です。

make firsttimeOrebootの作業を開始するたびに、または毎日:

cd oreboot

make update問題を報告する前に、間違いなくこれを行う必要があります。

プロジェクトには2つの異なることがあります。

src/mainboards/*実際のターゲット。それらは、ドライバー、SOC INITコードなどになる可能性のあるクレートに依存して共有します。メインボードの場合、 Cargo.lockを追跡する必要があります。src/*他のすべて;これらは前述の木枠であり、そのために、 Cargo.lockファイルを追跡しません。メインボードのCargo.lockをチェックインロックファイルは、ビルドの成功時にその依存関係の状態を記録し、再現性を可能にします。理想的には、ハードウェアで成功したブーツの後にロックファイルが更新されます。

詳細については、https://doc.rustlang.org/cargo/faq.html#why-do-binaries-have-cargolock-in-version-control-not-librariesを参照してください

新しいメインボードを作成するとき、同じアーキテクチャのために他の人がどのようにセットアップされるかを見るのは良いスタートです。 Orebootがベアメタルをターゲットにしていることに注意してください。そのため、利用可能な標準ライブラリはありません。

特定のプラットフォーム用の鉱石を構築するには、これを行います。

# Go to the mainboard's directory

cd src/mainboard/sunxi/nezha

# Build the mainboard target

make mainboard

# View disassembly

make objdump

# Run from RAM without flashing

make run

# Flash to the board

make flash

ルートMakefile使用すると、すべてのプラットフォームをすばやく構築できます。

# build all mainboards

make mainboards

# build everything in parallel

make -j mainboards

# Install QEMU for your target platform, e.g. x86

sudo apt install qemu-system-x86

# Build release build and start with QEMU

cd src/mainboard/emulation/qemu-q35 && make run

# Quit qemu with CTRL-A X

RISC-VのソースからQEMUを構築するには:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-riscv64 && cd build-riscv64

../configure --target-list=riscv64-softmmu

make -j$(nproc)

# QEMU binary is at riscv64-softmmu/qemu-system-riscv64

aarch64のソースからqemuを構築するには:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-aarch64 && cd build-aarch64

../configure --target-list=aarch64-softmmu

make -j$(nproc)

# QEMU binary is at aarch64-softmmu/qemu-system-aarch64

CoreBootと同様に、Orebootの構造はベンダーとメインボードごとです。それぞれ複数のアーキテクチャとSOCがサポートされており、その共通コードはボード間で共有されます。それ以外の場合は、マイナーな逸脱がコードの重複が多すぎる場合、ボードにバリアントがある場合があります。

qemu-riscv参照のために、以前のアプローチが文書化されています。 X86およびARMプラットフォームとメインボードのものをご覧ください。

以前のエミュレーションターゲットはsrc.broken/mainboard/emulation/に駐車されています。彼らは、オレブートがサポートしようとしている各アーキテクチャの一般的な理解を提供することになっています。

qemu-armv7qemu-aarch64qemu-q35Makefile sはシンプルでなければなりません。代わりにxtaskを使用して制御フローに使用します。src/mainboard/$VENDOR/$BOARD (サブ)ディレクトリのCargo.tomlは、ボード固有の依存関係を可能にし、すべてのステージを並行して構築します。make formatで自動フォーマットされています。 CIチェックは、変更がフォーマットルールに準拠していないかどうかを示します。Orebootの著作権は、非常に多数の個々の開発者と企業が所有しています。詳細については、個々のソースファイルを確認してください。

Orebootは、GNU General Public License(GPL)の条件に基づいてライセンスされています。一部のファイルは「GPL(バージョン2、または任意の後のバージョン)」に基づいてライセンスされ、一部のファイルは「GPL、バージョン2」の下でライセンスされています。他のプロジェクトから派生した一部の部分では、他の(GPL互換)ライセンスが適用される場合があります。詳細については、個々のソースファイルを確認してください。

これにより、GPLのバージョン2に基づいてライセンスされているOreboot画像が表示されます。