Oreboot เป็นส้อมดาวน์สตรีมของ CoreBoot นั่นคือ Oreboot คือ CoreBoot โดยไม่ต้อง 'C'

Oreboot ส่วนใหญ่เขียนเป็นสนิมโดยมีการประกอบตามที่จำเป็น

ปัจจุบัน Oreboot วางแผนที่จะสนับสนุน Payloads Linuxboot เท่านั้น

oreboot ?

v 13

cpu_pll fa001000

cpu_axi 5000100

cpu_axi 5000100

peri0_ctrl was: f8216300

peri0_ctrl lock en

peri0_ctrl PLLs

peri0_ctrl set: f8216300

DDR3@792MHz

test OK

512M ?

NOR flash: c2/2018

load 00018000 bytes to 40000000: ➡️.

load 00fc0000 bytes to 44000000: ➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️.

load 00010000 bytes to 41a00000: ➡️.

{ɕ serial uart0 initialized

RISC-V vendor 5b7 arch 0 imp 0

==== platform CSRs ====

MXSTATUS c0408000

MHCR 00000109

MCOR 00000002

MHINT 00004000

see C906 manual p581 ff

=======================

Set up extension CSRs

==== platform CSRs ====

MXSTATUS c0638000

MHCR 0000017f

MCOR 00000003

MHINT 0000610c

see C906 manual p581 ff

=======================

timer init

reset init

ipi init

RustSBI version 0.3.1

.______ __ __ _______.___________. _______..______ __

| _ | | | | / | | / || _ | |

| |_) | | | | | | (----`---| |----`| (----`| |_) || |

| / | | | | | | | _ < | |

| | ----.| `--' |.----) | | | .----) | | |_) || |

| _| `._____| ______/ |_______/ |__| |_______/ |______/ |__|

Platform Name: T-HEAD Xuantie Platform

Implementation: oreboot version 0.1.0

[rustsbi] misa: RV64ACDFIMSUVX

[rustsbi] mideleg: ssoftstimersext (0x222)

[rustsbi] medeleg: imaialmalasmasauecallipagelpagespage(0xb1f3)

[rustsbi] mie: msoft ssoft mtimer stimer mext sext (00000aaa)

PMP0 0x0 - 0x40000000 (A,R,W,X)

PMP1 0x40000000 - 0x40200000 (A,R)

PMP2 0x40200000 - 0x80000000 (A,R,W,X)

PMP3 0x80000000 - 0x80200000 (A,R)

PMP4 0x80200000 - 0xfffff800 (A,R,W,X)

PMP8 0x0 - 0x0 (A,R,W,X)

DTB looks fine, yay!

Decompress 12375521 bytes from 0x44000004 to 0x40200000, reserved 25165824 bytes

Success, decompressed 21910144 bytes :)

Payload looks like Linux Image, yay!

DTB still fine, yay!

Handing over to SBI, will continue at 0x40200000

enter supervisor at 40200000 with DTB from 41a00000

...

[ 0.000000] OF: fdt: Ignoring memory range 0x40000000 - 0x40200000

[ 0.000000] Machine model: Sipeed Lichee RV Dock

[ 0.000000] earlycon: sbi0 at I/O port 0x0 (options '')

[ 0.000000] printk: bootconsole [sbi0] enabled

[ 0.000000] Zone ranges:

[ 0.000000] DMA32 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Normal empty

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] riscv: SBI specification v1.0 detected

[ 0.000000] riscv: SBI implementation ID=0x4 Version=0x301

[ 0.000000] riscv: SBI TIME extension detected

[ 0.000000] riscv: SBI IPI extension detected

[ 0.000000] riscv: SBI SRST extension detected

[ 0.000000] riscv: base ISA extensions acdfim

[ 0.000000] riscv: ELF capabilities acdfim

[ 0.000000] percpu: Embedded 17 pages/cpu s31912 r8192 d29528 u69632

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 128520

[ 0.000000] Kernel command line: console=tty0 console=ttyS0,115200 loglevel=7 earlycon=sbi

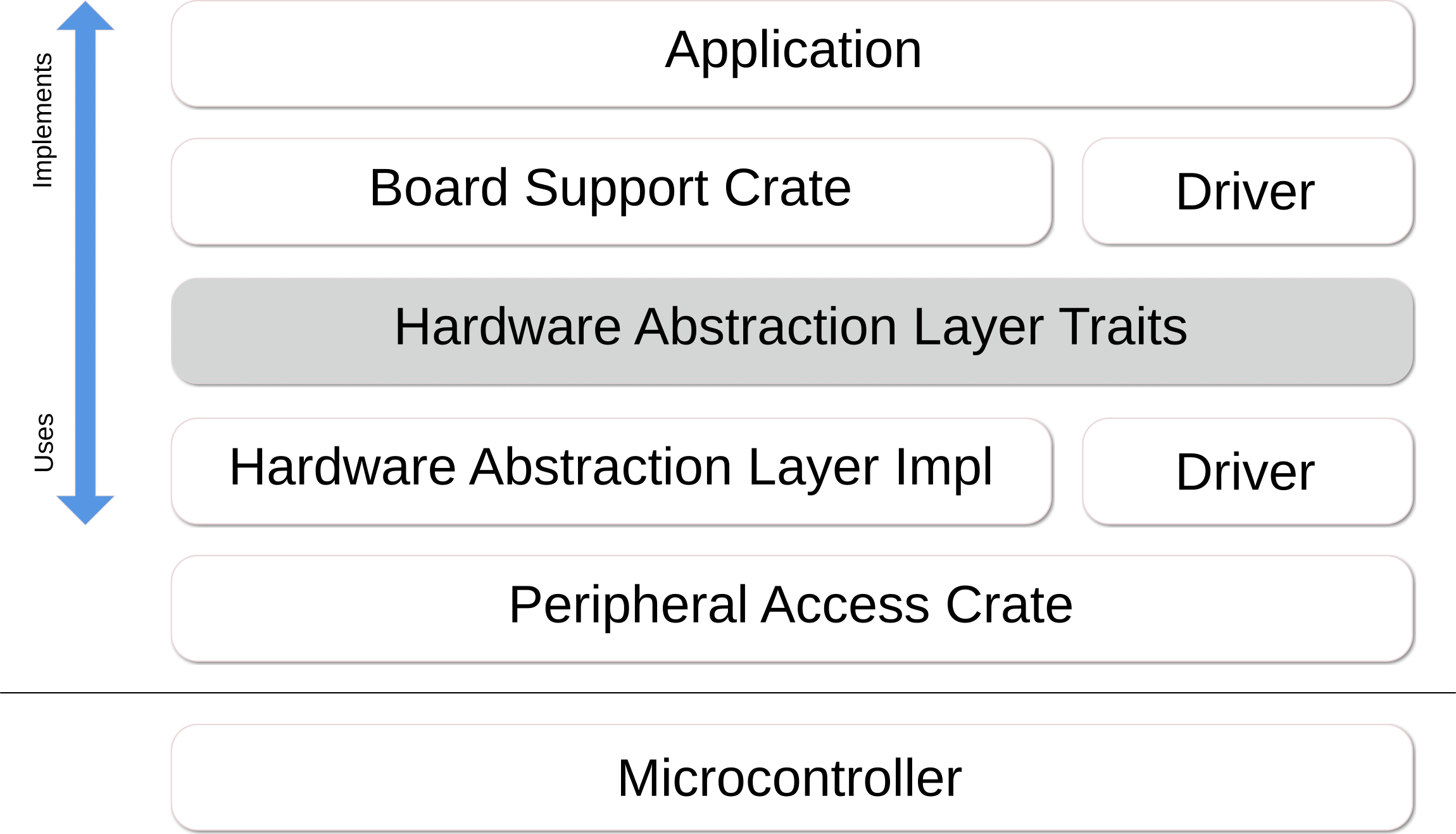

เราสร้างขึ้นมาจากสิ่งที่เป็นนามธรรมจากโมเดลของคณะทำงานที่ฝังอยู่ในสนิมด้วยลังและลักษณะของมันโดยมีรายละเอียดในหนังสือของพวกเขา

สั้น:

ผู้ขาย SOC คาดว่าจะจัดทำเอกสารเกี่ยวกับคอร์ของพวกเขาอุปกรณ์ต่อพ่วงและบล็อกอื่น ๆ และ/หรือไฟล์ SVD ของพวกเขาเพื่อให้เราสามารถสร้างลัง PAC และ HAL หรือในอุดมคติผู้ขายควร จัดหาและบำรุงรักษา เหล่านั้นเช่นกัน

หนังสือที่ฝังอยู่ในสนิมนำเสนอรูปแบบการออกแบบและแนวทางการใช้งานรวมถึงอภิธานศัพท์เพื่อทำความเข้าใจโครงสร้าง

เพื่อให้เข้าใจทั่วไปเกี่ยวกับวิธีการทำงานของ Oreboot และเฟิร์มแวร์ในงานทั่วไปให้ดูเอกสารประกอบการบูตโฟลว์ มันอธิบายถึงวิธีการจัดเก็บเฟิร์มแวร์และบูทบนแพลตฟอร์ม / SOC

โปรดทราบว่า Oreboot ไม่ได้ตั้งใจที่จะเปลี่ยนเป็นระบบปฏิบัติการของตัวเอง ดังนั้นเราจึงตั้งใจที่จะรักษาจำนวนและการทำงานของผู้ขับขี่ให้ต่ำ อย่างไรก็ตามโดยการออกแบบ SOCS เราต้องใช้บางสิ่งบางอย่างเพื่อโหลดรหัส:

ในหลายกรณีไม่จำเป็นต้องใช้ไดรเวอร์เต็มรูปแบบเนื่องจากเราจำเป็นต้องอ่านจากที่เก็บข้อมูลเท่านั้นและเราไม่จำเป็นต้องมีระบบไฟล์ที่หลากหลาย เพื่อหลีกเลี่ยงการชนกับความต้องการและข้อมูลเฉพาะของระบบปฏิบัติการเราขอแนะนำให้แยกชิ้นส่วนที่เก็บข้อมูลอย่างชัดเจนที่ถือเฟิร์มแวร์และระบบปฏิบัติการตามลำดับ ตัวอย่างเช่นใส่เฟิร์มแวร์ลงในแฟลช SPI และระบบปฏิบัติการบน NVME SSD

โคลน repo นี้และป้อนไดเรกทอรีเช่น:

git clone https://github.com/oreboot/oreboot.git

cd orebootโดยทั่วไปคุณจะต้องติดตั้งแพ็คเกจต่อไปนี้:

device-tree-compilerpkg-configlibsslrustup สำหรับระบบที่ใช้ Debian มีเป้าหมายในการติดตั้งเหล่านั้นซึ่งดึง rustup ผ่าน Curl จาก https://sh.rustup.rs:

make debiansysprepareมิฉะนั้นให้ติดตั้งแพ็คเกจผ่านตัวจัดการแพ็คเกจระบบของคุณ

โดยไม่คำนึงถึงระบบปฏิบัติการของคุณคุณจะต้องติดตั้ง Toolchain สำหรับ Oreboot คำสั่งนี้จะต้องทำเพียงครั้งเดียว แต่ปลอดภัยที่จะทำซ้ำ ๆ

make firsttimeทุกครั้งที่คุณเริ่มทำงานกับ Oreboot หรือแม้กระทั่งทุกวัน:

cd oreboot

make updateคุณควรทำสิ่งนี้ก่อนที่จะรายงานปัญหาใด ๆ

มีสองสิ่งที่แตกต่างกันในโครงการ:

src/mainboards/* เป้าหมายจริง; ผู้ที่ขึ้นอยู่กับและแชร์ลังซึ่งสามารถเป็นไดรเวอร์รหัส SOC Init และคล้ายกัน สำหรับ mainboards ต้อง ติดตาม Cargo.locksrc/* ทุกอย่างอื่น; นี่คือลังดังกล่าวซึ่งเราไม่ได้ติดตามไฟล์ Cargo.lock การตรวจสอบในสินค้าของ Cargo.lock ไฟล์ล็อคบันทึกสถานะของการพึ่งพาในช่วงเวลาของการสร้างที่ประสบความสำเร็จเปิดใช้งานการทำซ้ำ ตามหลักการแล้วไฟล์ล็อคจะได้รับการอัปเดตการบูตที่ประสบความสำเร็จบนฮาร์ดแวร์

สำหรับข้อมูลเพิ่มเติมดูที่: https://doc.rust-lang.org/cargo/faq.html#why-do-binaries-have-cargolock-in-version-control--not-libraries

เมื่อสร้างเมนบอร์ดใหม่การดูว่าคนอื่น ๆ ได้รับการตั้งค่าสำหรับสถาปัตยกรรมเดียวกันเป็นการเริ่มต้นที่ดี โปรดทราบว่า Oreboot กำลังกำหนดเป้าหมายโลหะเปลือยดังนั้นจึงไม่มีห้องสมุดมาตรฐาน

ในการสร้าง Oreboot สำหรับแพลตฟอร์มเฉพาะทำสิ่งนี้:

# Go to the mainboard's directory

cd src/mainboard/sunxi/nezha

# Build the mainboard target

make mainboard

# View disassembly

make objdump

# Run from RAM without flashing

make run

# Flash to the board

make flash

Root Makefile ช่วยให้คุณสามารถสร้างแพลตฟอร์มทั้งหมดได้อย่างรวดเร็ว:

# build all mainboards

make mainboards

# build everything in parallel

make -j mainboards

# Install QEMU for your target platform, e.g. x86

sudo apt install qemu-system-x86

# Build release build and start with QEMU

cd src/mainboard/emulation/qemu-q35 && make run

# Quit qemu with CTRL-A X

เพื่อสร้าง QEMU จากแหล่งที่มาสำหรับ RISC-V:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-riscv64 && cd build-riscv64

../configure --target-list=riscv64-softmmu

make -j$(nproc)

# QEMU binary is at riscv64-softmmu/qemu-system-riscv64

เพื่อสร้าง QEMU จากแหล่งที่มาสำหรับ Aarch64:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-aarch64 && cd build-aarch64

../configure --target-list=aarch64-softmmu

make -j$(nproc)

# QEMU binary is at aarch64-softmmu/qemu-system-aarch64

เช่นเดียวกับ CoreBoot โครงสร้างใน Oreboot เป็นต่อผู้ขายและเมนบอร์ด สถาปัตยกรรมและ SOC หลายแห่งได้รับการสนับสนุนตามลำดับและรหัสทั่วไปของพวกเขาจะถูกแชร์ระหว่างบอร์ด บอร์ดอาจมีตัวแปรหากการเบี่ยงเบนเล็กน้อยอาจทำให้เกิดการทำซ้ำรหัสมากเกินไป

qemu-riscvสำหรับการอ้างอิงวิธีการก่อนหน้านี้ได้รับการบันทึกไว้ ดูที่สำหรับ X86 และแพลตฟอร์ม ARM และ Mainboards

เป้าหมายการจำลองก่อนหน้านี้ได้รับการจอดใน src.broken/mainboard/emulation/ พวกเขาควรจะให้ความเข้าใจทั่วไปของแต่ละสถาปัตยกรรมที่ Oreboot พยายามสนับสนุน:

qemu-armv7qemu-aarch64qemu-q35Makefile S ต้องง่าย ใช้ xtask แทนการควบคุมการไหลเช่นการเพิ่มส่วนหัวหรือการตรวจสอบลงในไบนารีภาพ sitchting ฯลฯCargo.toml ในไดเรกทอรี src/mainboard/$VENDOR/$BOARD (SUB) ที่เกี่ยวข้องอนุญาตให้มีการพึ่งพาเฉพาะบอร์ดและสร้างทุกขั้นตอนในแบบคู่ขนานmake format โดยไม่มีข้อยกเว้น การตรวจสอบ CI จะบอกว่าการเปลี่ยนแปลงไม่ปฏิบัติตามกฎการจัดรูปแบบหรือไม่ลิขสิทธิ์บน Oreboot เป็นเจ้าของโดยนักพัฒนาและ บริษัท แต่ละรายจำนวนมาก โปรดตรวจสอบรายละเอียดไฟล์ต้นฉบับแต่ละไฟล์

Oreboot ได้รับใบอนุญาตภายใต้เงื่อนไขของใบอนุญาตสาธารณะ GNU ทั่วไป (GPL) ไฟล์บางไฟล์ได้รับอนุญาตภายใต้ "GPL (เวอร์ชัน 2 หรือเวอร์ชันใด ๆ ใหม่ ๆ )" และไฟล์บางไฟล์ได้รับอนุญาตภายใต้ "GPL, เวอร์ชัน 2" สำหรับบางส่วนซึ่งได้มาจากโครงการอื่น ๆ อาจมีการใช้ใบอนุญาตอื่น ๆ (GPL ที่เข้ากันได้) โปรดตรวจสอบรายละเอียดไฟล์ต้นฉบับแต่ละไฟล์

สิ่งนี้ทำให้ภาพ Oreboot ที่ได้รับอนุญาตภายใต้ GPL เวอร์ชัน 2