Oreboot adalah garpu hilir coreboot, yaitu oreboot adalah coreboot tanpa 'c'.

Oreboot sebagian besar ditulis dalam karat, dengan perakitan di mana diperlukan.

Oreboot saat ini hanya berencana untuk mendukung muatan linuxboot.

oreboot ?

v 13

cpu_pll fa001000

cpu_axi 5000100

cpu_axi 5000100

peri0_ctrl was: f8216300

peri0_ctrl lock en

peri0_ctrl PLLs

peri0_ctrl set: f8216300

DDR3@792MHz

test OK

512M ?

NOR flash: c2/2018

load 00018000 bytes to 40000000: ➡️.

load 00fc0000 bytes to 44000000: ➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️.

load 00010000 bytes to 41a00000: ➡️.

{ɕ serial uart0 initialized

RISC-V vendor 5b7 arch 0 imp 0

==== platform CSRs ====

MXSTATUS c0408000

MHCR 00000109

MCOR 00000002

MHINT 00004000

see C906 manual p581 ff

=======================

Set up extension CSRs

==== platform CSRs ====

MXSTATUS c0638000

MHCR 0000017f

MCOR 00000003

MHINT 0000610c

see C906 manual p581 ff

=======================

timer init

reset init

ipi init

RustSBI version 0.3.1

.______ __ __ _______.___________. _______..______ __

| _ | | | | / | | / || _ | |

| |_) | | | | | | (----`---| |----`| (----`| |_) || |

| / | | | | | | | _ < | |

| | ----.| `--' |.----) | | | .----) | | |_) || |

| _| `._____| ______/ |_______/ |__| |_______/ |______/ |__|

Platform Name: T-HEAD Xuantie Platform

Implementation: oreboot version 0.1.0

[rustsbi] misa: RV64ACDFIMSUVX

[rustsbi] mideleg: ssoftstimersext (0x222)

[rustsbi] medeleg: imaialmalasmasauecallipagelpagespage(0xb1f3)

[rustsbi] mie: msoft ssoft mtimer stimer mext sext (00000aaa)

PMP0 0x0 - 0x40000000 (A,R,W,X)

PMP1 0x40000000 - 0x40200000 (A,R)

PMP2 0x40200000 - 0x80000000 (A,R,W,X)

PMP3 0x80000000 - 0x80200000 (A,R)

PMP4 0x80200000 - 0xfffff800 (A,R,W,X)

PMP8 0x0 - 0x0 (A,R,W,X)

DTB looks fine, yay!

Decompress 12375521 bytes from 0x44000004 to 0x40200000, reserved 25165824 bytes

Success, decompressed 21910144 bytes :)

Payload looks like Linux Image, yay!

DTB still fine, yay!

Handing over to SBI, will continue at 0x40200000

enter supervisor at 40200000 with DTB from 41a00000

...

[ 0.000000] OF: fdt: Ignoring memory range 0x40000000 - 0x40200000

[ 0.000000] Machine model: Sipeed Lichee RV Dock

[ 0.000000] earlycon: sbi0 at I/O port 0x0 (options '')

[ 0.000000] printk: bootconsole [sbi0] enabled

[ 0.000000] Zone ranges:

[ 0.000000] DMA32 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Normal empty

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] riscv: SBI specification v1.0 detected

[ 0.000000] riscv: SBI implementation ID=0x4 Version=0x301

[ 0.000000] riscv: SBI TIME extension detected

[ 0.000000] riscv: SBI IPI extension detected

[ 0.000000] riscv: SBI SRST extension detected

[ 0.000000] riscv: base ISA extensions acdfim

[ 0.000000] riscv: ELF capabilities acdfim

[ 0.000000] percpu: Embedded 17 pages/cpu s31912 r8192 d29528 u69632

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 128520

[ 0.000000] Kernel command line: console=tty0 console=ttyS0,115200 loglevel=7 earlycon=sbi

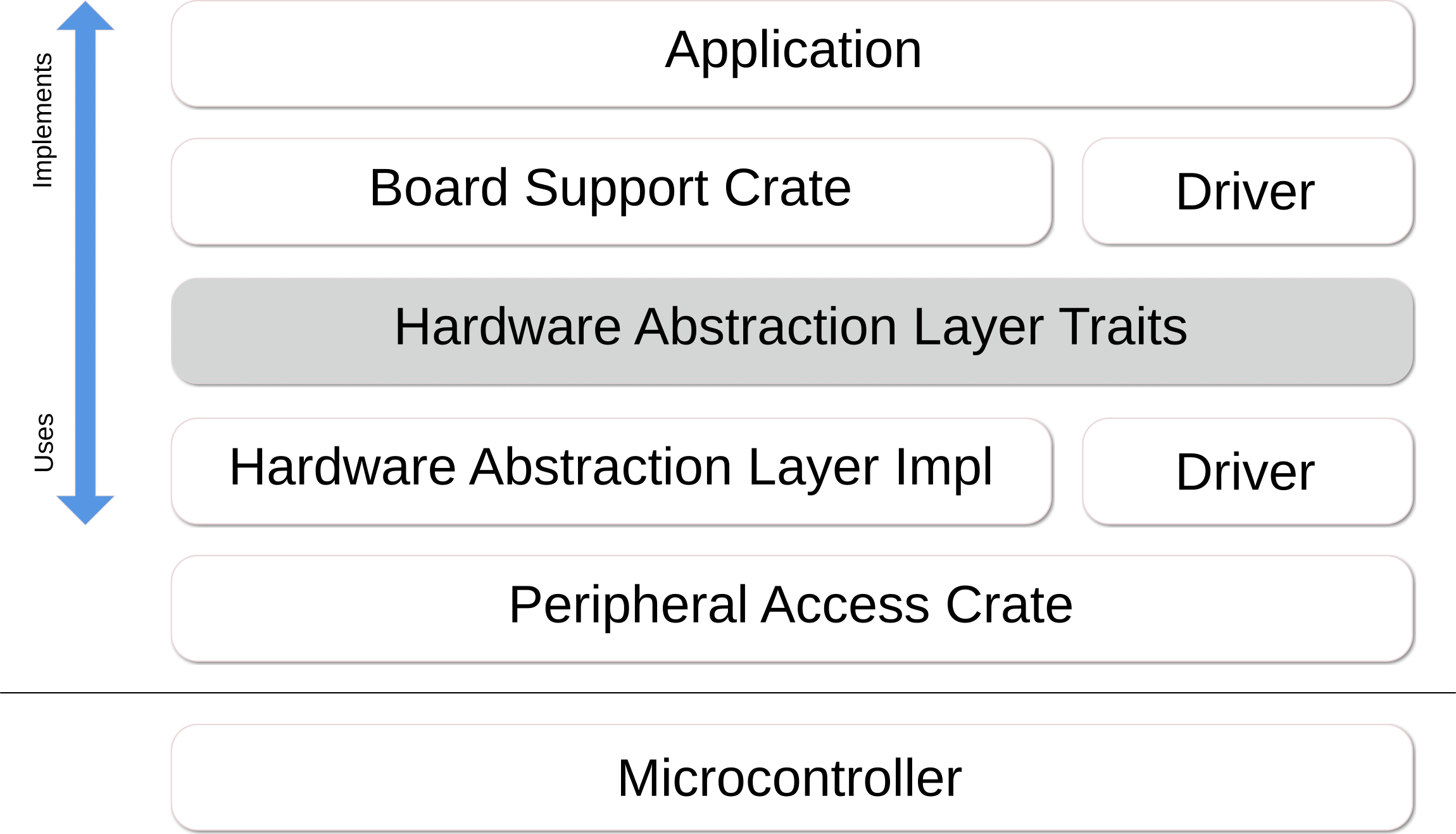

Kami membangun di atas abstraksi dari model kelompok kerja yang tertanam karat dengan peti dan sifatnya, yang dirinci dalam buku mereka.

Pendeknya:

Vendor SOC diharapkan memberikan dokumentasi kepada inti, periferal dan blok lainnya dan/atau file SVD mereka, sehingga kami dapat menghasilkan peti PAC dan HAL, atau idealnya, vendor harus menyediakan dan memeliharanya juga.

Buku tertanam karat menawarkan pola desain dan pedoman implementasi serta glosarium untuk mendapatkan pemahaman tentang struktur.

Untuk mendapatkan pemahaman umum tentang bagaimana oreboot dan firmware secara umum berfungsi, lihat dokumentasi aliran boot. Ini menjelaskan bagaimana firmware disimpan dan memicu platform / SOC.

Perhatikan bahwa oreboot tidak bertujuan untuk berubah menjadi sistem operasinya sendiri. Dengan demikian, kami bermaksud menjaga jumlah dan fungsionalitas pengemudi rendah. Namun, dengan desain SOC, kami harus menerapkan sesuatu untuk memuat kode:

Dalam banyak kasus, tidak diperlukan driver penuh, karena kita hanya perlu membaca dari penyimpanan, dan kita tidak membutuhkan sistem file yang kaya. Untuk menghindari bertabrakan dengan kebutuhan dan spesifik OS, kami sarankan untuk memisahkan bagian penyimpanan dengan jelas memegang firmware dan sistem operasi, masing -masing. Misalnya, letakkan firmware di flash SPI dan OS pada SSD NVME.

Klone repo ini dan masukkan direktori, yaitu:

git clone https://github.com/oreboot/oreboot.git

cd orebootSecara umum, Anda akan membutuhkan paket berikut yang diinstal:

device-tree-compilerpkg-configlibsslrustup Untuk sistem berbasis Debian, ada target membuat untuk menginstal itu, yang menarik rustup melalui ikal dari https://sh.rustup.rs:

make debiansysprepareJika tidak, instal paket melalui manajer paket sistem Anda.

Terlepas dari OS Anda, Anda perlu menginstal toolchain untuk oreboot. Perintah ini hanya perlu dilakukan sekali tetapi aman untuk melakukannya berulang kali.

make firsttimeSetiap kali Anda mulai bekerja dengan oreboot, atau bahkan setiap hari:

cd oreboot

make updateAnda harus melakukan ini sebelum melaporkan masalah apa pun.

Ada dua hal berbeda dalam proyek:

src/mainboards/* target aktual; Itu bergantung pada dan berbagi peti, yang dapat berupa driver, kode init SOC, dan serupa. Untuk papan utama, Cargo.lock harus dilacak.src/* yang lainnya; Ini adalah peti yang disebutkan di atas, yang, kami tidak melacak file Cargo.lock . Memeriksa file Cargo.lock mainboard mencatat keadaan ketergantungannya pada saat pembangunan yang berhasil, memungkinkan reproduktifitas. Idealnya, file kunci diperbarui dari boot sukses pada perangkat keras.

Untuk lebih lanjut, lihat: https://doc.rust-lang.org/cargo/faq.html#why-do-binaries-have-cargolock-in-version-control-but-not-libraries

Saat membuat mainboard baru, melihat bagaimana orang lain diatur untuk arsitektur yang sama adalah awal yang baik. Ketahuilah bahwa oreboot menargetkan logam telanjang, jadi tidak ada perpustakaan standar yang tersedia.

Untuk membangun oreboot untuk platform tertentu, lakukan ini:

# Go to the mainboard's directory

cd src/mainboard/sunxi/nezha

# Build the mainboard target

make mainboard

# View disassembly

make objdump

# Run from RAM without flashing

make run

# Flash to the board

make flash

Root Makefile memungkinkan Anda untuk dengan cepat membangun semua platform:

# build all mainboards

make mainboards

# build everything in parallel

make -j mainboards

# Install QEMU for your target platform, e.g. x86

sudo apt install qemu-system-x86

# Build release build and start with QEMU

cd src/mainboard/emulation/qemu-q35 && make run

# Quit qemu with CTRL-A X

Untuk membangun qemu dari sumber untuk risc-v:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-riscv64 && cd build-riscv64

../configure --target-list=riscv64-softmmu

make -j$(nproc)

# QEMU binary is at riscv64-softmmu/qemu-system-riscv64

Untuk membangun qemu dari sumber untuk aarch64:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-aarch64 && cd build-aarch64

../configure --target-list=aarch64-softmmu

make -j$(nproc)

# QEMU binary is at aarch64-softmmu/qemu-system-aarch64

Mirip dengan coreboot, struktur dalam oreboot adalah per vendor dan mainboard. Beberapa arsitektur dan SOC masing -masing didukung, dan kode umum mereka dibagi di antara dewan. Dewan mungkin memiliki varian jika penyimpangan kecil akan menyebabkan terlalu banyak duplikasi kode.

qemu-riscvUntuk referensi, pendekatan sebelumnya didokumentasikan. Lihatlah itu untuk platform x86 dan lengan dan papan utama.

Target emulasi sebelumnya telah diparkir di src.broken/mainboard/emulation/ . Mereka seharusnya memberikan pemahaman umum tentang setiap arsitektur yang ingin didukung Oreboot:

qemu-armv7qemu-aarch64qemu-q35Makefile S harus sederhana. Gunakan xtask sebagai gantinya untuk aliran kontrol, misalnya, menambahkan header atau checksum ke binari, gambar tersimpan, dll.Cargo.toml di direktori src/mainboard/$VENDOR/$BOARD (sub) masing-masing memungkinkan dependensi khusus papan dan membangun semua tahap secara paralel.make format tanpa pengecualian. Pemeriksaan CI akan memberi tahu apakah perubahan tidak mematuhi aturan pemformatan.Hak cipta di oreboot dimiliki oleh sejumlah besar pengembang dan perusahaan individu. Silakan periksa file sumber individual untuk detailnya.

Oreboot dilisensikan berdasarkan ketentuan Lisensi Publik Umum GNU (GPL). Beberapa file dilisensikan di bawah "GPL (versi 2, atau versi selanjutnya)", dan beberapa file dilisensikan di bawah "GPL, Versi 2". Untuk beberapa bagian, yang berasal dari proyek lain, lisensi lain (kompatibel GPL) mungkin berlaku. Silakan periksa file sumber individual untuk detailnya.

Ini membuat gambar oreboot yang dihasilkan dilisensikan di bawah GPL, versi 2.