Oreboot - это нисходящая вилка Coreboot, то есть Oreboot - это Coreboot без 'c'.

Oreboot в основном написан в ржавчине, с сборкой, где это необходимо.

В настоящее время Oreboot планирует только поддерживать полезные нагрузки LinuxBoot.

oreboot ?

v 13

cpu_pll fa001000

cpu_axi 5000100

cpu_axi 5000100

peri0_ctrl was: f8216300

peri0_ctrl lock en

peri0_ctrl PLLs

peri0_ctrl set: f8216300

DDR3@792MHz

test OK

512M ?

NOR flash: c2/2018

load 00018000 bytes to 40000000: ➡️.

load 00fc0000 bytes to 44000000: ➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️.

load 00010000 bytes to 41a00000: ➡️.

{ɕ serial uart0 initialized

RISC-V vendor 5b7 arch 0 imp 0

==== platform CSRs ====

MXSTATUS c0408000

MHCR 00000109

MCOR 00000002

MHINT 00004000

see C906 manual p581 ff

=======================

Set up extension CSRs

==== platform CSRs ====

MXSTATUS c0638000

MHCR 0000017f

MCOR 00000003

MHINT 0000610c

see C906 manual p581 ff

=======================

timer init

reset init

ipi init

RustSBI version 0.3.1

.______ __ __ _______.___________. _______..______ __

| _ | | | | / | | / || _ | |

| |_) | | | | | | (----`---| |----`| (----`| |_) || |

| / | | | | | | | _ < | |

| | ----.| `--' |.----) | | | .----) | | |_) || |

| _| `._____| ______/ |_______/ |__| |_______/ |______/ |__|

Platform Name: T-HEAD Xuantie Platform

Implementation: oreboot version 0.1.0

[rustsbi] misa: RV64ACDFIMSUVX

[rustsbi] mideleg: ssoftstimersext (0x222)

[rustsbi] medeleg: imaialmalasmasauecallipagelpagespage(0xb1f3)

[rustsbi] mie: msoft ssoft mtimer stimer mext sext (00000aaa)

PMP0 0x0 - 0x40000000 (A,R,W,X)

PMP1 0x40000000 - 0x40200000 (A,R)

PMP2 0x40200000 - 0x80000000 (A,R,W,X)

PMP3 0x80000000 - 0x80200000 (A,R)

PMP4 0x80200000 - 0xfffff800 (A,R,W,X)

PMP8 0x0 - 0x0 (A,R,W,X)

DTB looks fine, yay!

Decompress 12375521 bytes from 0x44000004 to 0x40200000, reserved 25165824 bytes

Success, decompressed 21910144 bytes :)

Payload looks like Linux Image, yay!

DTB still fine, yay!

Handing over to SBI, will continue at 0x40200000

enter supervisor at 40200000 with DTB from 41a00000

...

[ 0.000000] OF: fdt: Ignoring memory range 0x40000000 - 0x40200000

[ 0.000000] Machine model: Sipeed Lichee RV Dock

[ 0.000000] earlycon: sbi0 at I/O port 0x0 (options '')

[ 0.000000] printk: bootconsole [sbi0] enabled

[ 0.000000] Zone ranges:

[ 0.000000] DMA32 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Normal empty

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] riscv: SBI specification v1.0 detected

[ 0.000000] riscv: SBI implementation ID=0x4 Version=0x301

[ 0.000000] riscv: SBI TIME extension detected

[ 0.000000] riscv: SBI IPI extension detected

[ 0.000000] riscv: SBI SRST extension detected

[ 0.000000] riscv: base ISA extensions acdfim

[ 0.000000] riscv: ELF capabilities acdfim

[ 0.000000] percpu: Embedded 17 pages/cpu s31912 r8192 d29528 u69632

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 128520

[ 0.000000] Kernel command line: console=tty0 console=ttyS0,115200 loglevel=7 earlycon=sbi

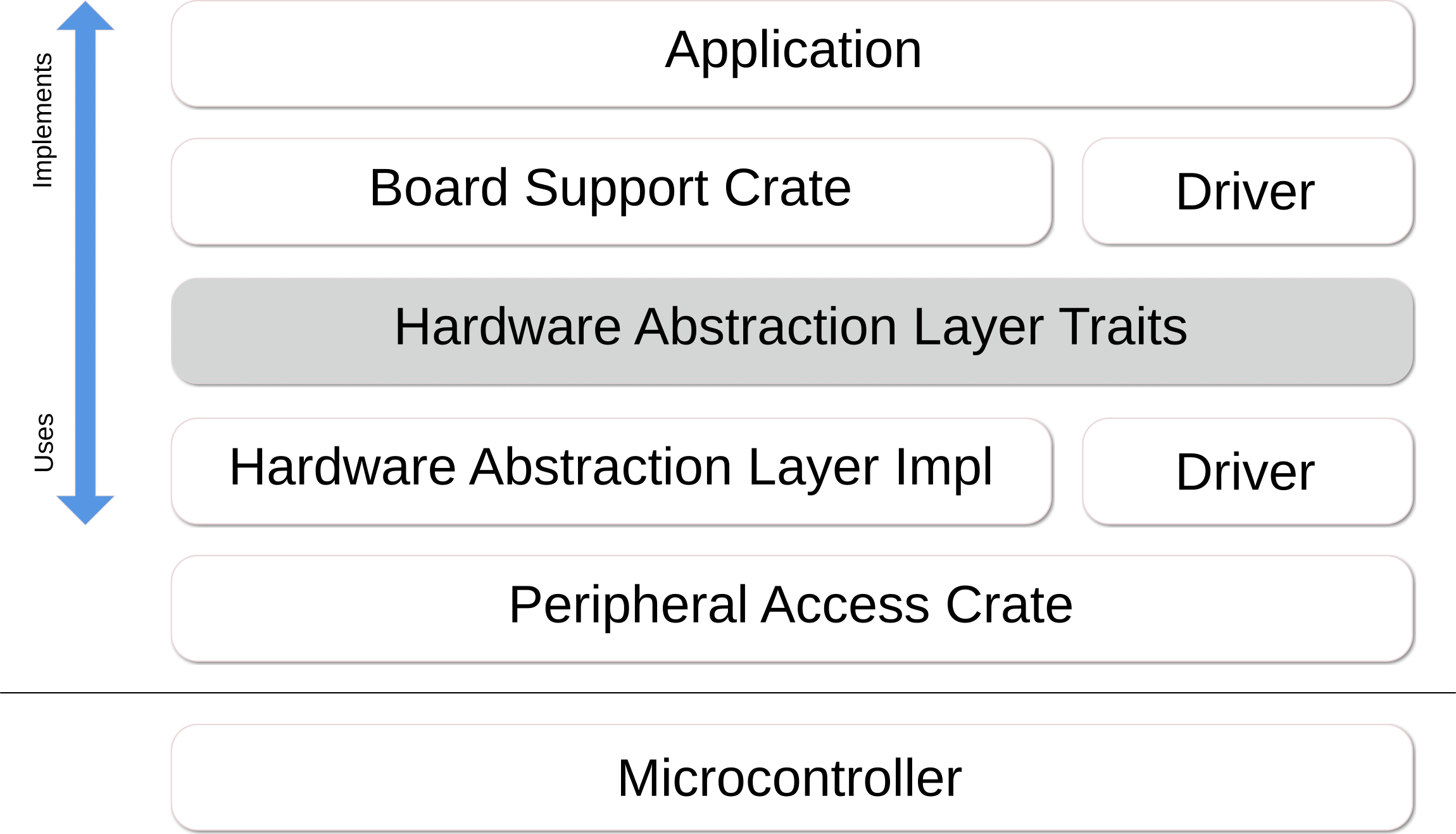

Мы строим на вершине абстракций из модели рабочей группы встроенной ржавчины с ее ящиками и чертами, подробно описанными в их книге.

В двух словах:

Ожидается, что поставщики SOC предоставит документацию своим ядрам, периферийным устройствам и другим блокам и/или своим файлам SVD, чтобы мы могли генерировать ящики PAC и HAL, или в идеале, поставщик должен также предоставлять и поддерживать их.

Книга встроенной ржавчины предлагает шаблоны проектирования и руководящие принципы реализации, а также глоссарий, чтобы получить понимание структуры.

Чтобы получить общее представление о том, как Oreboot и прошивка в целом, посмотрите на документацию по потоку загрузки. Он описывает, как хранится прошивка и загружается на платформе / Soc.

Обратите внимание, что Oreboot не стремится превратиться в свою собственную операционную систему. Соответственно, мы намерены сохранить низкую сумму и функциональность водителей. Однако, по проектированию SOC, мы должны реализовать что -то для загрузки кода:

Во многих случаях нет полного драйвера, так как нам нужно только читать, например, с хранения, и нам не нужны богатые файловые системы. Чтобы избежать столкновения с потребностями и спецификой ОС, мы рекомендуем четко отделить детали хранения, удерживающие прошивку и операционную систему, соответственно. Например, поместите прошивку в вспышку SPI и ОС на SSD NVME.

Клонировать это репо и введите его каталог, т.е.

git clone https://github.com/oreboot/oreboot.git

cd orebootВ общем, вам понадобятся следующие установленные пакеты:

device-tree-compilerpkg-configlibsslrustup Для систем на базе Debian существует цель для их установки, которая вытаскивает rustup через Curl от https://sh.rustup.rs:

make debiansysprepareВ противном случае установите пакет через диспетчер пакетов системы.

Независимо от вашей ОС, вам нужно будет установить набор инструментов для Oreboot. Эта команда должна быть выполнена только один раз, но это безопасно сделать это неоднократно.

make firsttimeКаждый раз, когда вы начинаете работать с Oreboot или даже ежедневно:

cd oreboot

make updateВы обязательно должны сделать это, прежде чем сообщать о каких -либо проблемах.

В проекте есть две разные вещи:

src/mainboards/* Фактические цели; Они зависят от ящиков и обмена ящиками, которые могут быть драйверами, кодом инициирования SOC и аналогичными. Для материнских досок, Cargo.lock должен отслеживать.src/* все остальное; Это вышеупомянутые ящики, для которых мы не отслеживаем файлы Cargo.lock . Проверка в файле Cargo.lock Записывает состояние его зависимостей во время успешной сборки, что обеспечивает воспроизводимость. В идеале, файл блокировки обновляется, Follwoing Успешная загрузка на аппаратном обеспечении.

Подробнее см.: Https://doc.rust-lang.org/cargo/faq.html#why-do-binary-have-cargolock-in-version-control-but-not-libraries

При создании новой материнской платы взглянуть на то, как другие настроены для той же архитектуры, - хорошее начало. Имейте в виду, что Oreboot нацелена на голое металл, поэтому стандартной библиотеки нет.

Чтобы создать Oreboot для конкретной платформы, сделайте это:

# Go to the mainboard's directory

cd src/mainboard/sunxi/nezha

# Build the mainboard target

make mainboard

# View disassembly

make objdump

# Run from RAM without flashing

make run

# Flash to the board

make flash

Корневой Makefile позволяет быстро построить все платформы:

# build all mainboards

make mainboards

# build everything in parallel

make -j mainboards

# Install QEMU for your target platform, e.g. x86

sudo apt install qemu-system-x86

# Build release build and start with QEMU

cd src/mainboard/emulation/qemu-q35 && make run

# Quit qemu with CTRL-A X

Чтобы построить QEMU из источника для RISC-V:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-riscv64 && cd build-riscv64

../configure --target-list=riscv64-softmmu

make -j$(nproc)

# QEMU binary is at riscv64-softmmu/qemu-system-riscv64

Чтобы построить QEMU из источника для Aarch64:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-aarch64 && cd build-aarch64

../configure --target-list=aarch64-softmmu

make -j$(nproc)

# QEMU binary is at aarch64-softmmu/qemu-system-aarch64

Подобно Coreboot, структура в Oreboot состоит из поставщика и материнской платы. Многочисленные архитектуры и SOC поддерживаются соответственно, и их общий код делятся между досками. У советов могут быть варианты, если в противном случае незначительные отклонения приведут к слишком большому количеству дублирования кода.

qemu-riscvДля справки, более ранние подходы задокументированы. Посмотрите на них на платформы x86 и ARM и материальные доски.

Более ранние цели эмуляции были припаркованы в src.broken/mainboard/emulation/ . Они должны предоставить общее понимание каждой архитектуры, которую Oreboot стремится поддержать:

qemu-armv7qemu-aarch64qemu-q35Makefile S должен быть простым. Вместо этого используйте xtask для управления, например, добавление заголовков или контролей в двоичные файлы, прикалывание изображений и т. Д.Cargo.toml в соответствующих каталогах src/mainboard/$VENDOR/$BOARD (SUB) позволяет ориентироваться на зависимости и строить все этапы параллельно.make format без исключений. Проверка CI покажет, не придерживается ли изменение правила форматирования.Авторское право на Oreboot принадлежит довольно большому количеству отдельных разработчиков и компаний. Пожалуйста, проверьте отдельные исходные файлы для получения подробной информации.

Oreboot лицензирован в соответствии с условиями общей публичной лицензии GNU (GPL). Некоторые файлы лицензированы в рамках «GPL (версия 2 или любой более поздней версии)», а некоторые файлы лицензированы в «GPL, версии 2». Для некоторых частей, которые были получены из других проектов, могут применяться другие (совместимые с GPL) лицензией. Пожалуйста, проверьте отдельные исходные файлы для получения подробной информации.

Это делает полученные изображения Oreboot, лицензированные под GPL, версия 2.