Oreboot هو شوكة في اتجاه مجرى CoreBoot ، أي oreboot هو CoreBoot بدون 'c'.

أوريبوت مكتوب في الغالب في الصدأ ، مع التجميع عند الحاجة.

تخطط Oreboot حاليًا فقط لدعم حمولات Linuxboot.

oreboot ?

v 13

cpu_pll fa001000

cpu_axi 5000100

cpu_axi 5000100

peri0_ctrl was: f8216300

peri0_ctrl lock en

peri0_ctrl PLLs

peri0_ctrl set: f8216300

DDR3@792MHz

test OK

512M ?

NOR flash: c2/2018

load 00018000 bytes to 40000000: ➡️.

load 00fc0000 bytes to 44000000: ➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️➡️.

load 00010000 bytes to 41a00000: ➡️.

{ɕ serial uart0 initialized

RISC-V vendor 5b7 arch 0 imp 0

==== platform CSRs ====

MXSTATUS c0408000

MHCR 00000109

MCOR 00000002

MHINT 00004000

see C906 manual p581 ff

=======================

Set up extension CSRs

==== platform CSRs ====

MXSTATUS c0638000

MHCR 0000017f

MCOR 00000003

MHINT 0000610c

see C906 manual p581 ff

=======================

timer init

reset init

ipi init

RustSBI version 0.3.1

.______ __ __ _______.___________. _______..______ __

| _ | | | | / | | / || _ | |

| |_) | | | | | | (----`---| |----`| (----`| |_) || |

| / | | | | | | | _ < | |

| | ----.| `--' |.----) | | | .----) | | |_) || |

| _| `._____| ______/ |_______/ |__| |_______/ |______/ |__|

Platform Name: T-HEAD Xuantie Platform

Implementation: oreboot version 0.1.0

[rustsbi] misa: RV64ACDFIMSUVX

[rustsbi] mideleg: ssoftstimersext (0x222)

[rustsbi] medeleg: imaialmalasmasauecallipagelpagespage(0xb1f3)

[rustsbi] mie: msoft ssoft mtimer stimer mext sext (00000aaa)

PMP0 0x0 - 0x40000000 (A,R,W,X)

PMP1 0x40000000 - 0x40200000 (A,R)

PMP2 0x40200000 - 0x80000000 (A,R,W,X)

PMP3 0x80000000 - 0x80200000 (A,R)

PMP4 0x80200000 - 0xfffff800 (A,R,W,X)

PMP8 0x0 - 0x0 (A,R,W,X)

DTB looks fine, yay!

Decompress 12375521 bytes from 0x44000004 to 0x40200000, reserved 25165824 bytes

Success, decompressed 21910144 bytes :)

Payload looks like Linux Image, yay!

DTB still fine, yay!

Handing over to SBI, will continue at 0x40200000

enter supervisor at 40200000 with DTB from 41a00000

...

[ 0.000000] OF: fdt: Ignoring memory range 0x40000000 - 0x40200000

[ 0.000000] Machine model: Sipeed Lichee RV Dock

[ 0.000000] earlycon: sbi0 at I/O port 0x0 (options '')

[ 0.000000] printk: bootconsole [sbi0] enabled

[ 0.000000] Zone ranges:

[ 0.000000] DMA32 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Normal empty

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040200000-0x000000005fffffff]

[ 0.000000] riscv: SBI specification v1.0 detected

[ 0.000000] riscv: SBI implementation ID=0x4 Version=0x301

[ 0.000000] riscv: SBI TIME extension detected

[ 0.000000] riscv: SBI IPI extension detected

[ 0.000000] riscv: SBI SRST extension detected

[ 0.000000] riscv: base ISA extensions acdfim

[ 0.000000] riscv: ELF capabilities acdfim

[ 0.000000] percpu: Embedded 17 pages/cpu s31912 r8192 d29528 u69632

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 128520

[ 0.000000] Kernel command line: console=tty0 console=ttyS0,115200 loglevel=7 earlycon=sbi

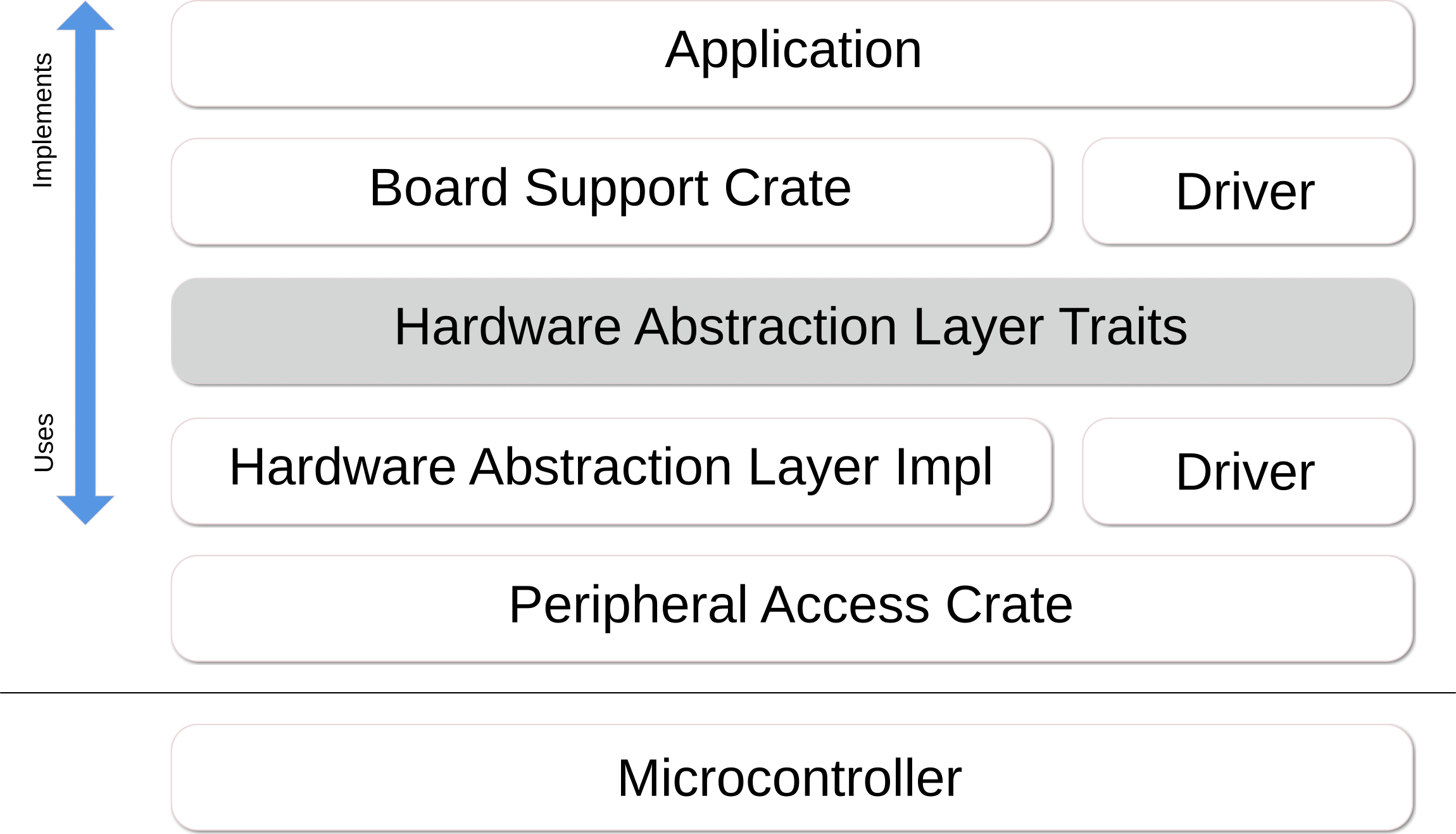

نحن نبني على أعلى التجريدات من نموذج مجموعة العمل المضمّن الصدأ مع صناديقها وسماتها ، مفصلة في كتابهم.

باختصار:

من المتوقع أن يوفر بائعو SOC وثائق إلى النوى والأجهزة الطرفية و/أو ملفات SVD الخاصة بهم ، حتى نتمكن من إنشاء صناديق PAC و HAL ، أو من الناحية المثالية ، يجب على البائع توفيرها وصيانتها أيضًا.

يوفر الكتاب المضمّن Rust أنماط تصميم وإرشادات التنفيذ بالإضافة إلى مسرد لاكتساب فهم للهيكل.

للحصول على فهم عام لكيفية عمل Oreboot والبرامج الثابتة بشكل عام ، إلقاء نظرة على وثائق تدفق التمهيد. يصف كيفية تخزين البرامج الثابتة وتجمعها على منصة / SOC.

لاحظ أن Oreboot لا يهدف إلى التحول إلى نظام التشغيل الخاص به. وفقًا لذلك ، نعتزم الحفاظ على كمية ووظائف السائقين منخفضة. ومع ذلك ، من خلال تصميم SOCs ، يتعين علينا تنفيذ شيء لتحميل الكود:

في كثير من الحالات ، لا توجد حاجة إلى برنامج تشغيل كامل ، لأننا نحتاج فقط إلى القراءة من التخزين ، ولا نحتاج إلى أنظمة ملفات غنية. لتجنب الاصطدام باحتياجات وتفاصيل نظام التشغيل ، نوصي بوضوح بفصل أجزاء التخزين التي تحمل البرامج الثابتة ونظام التشغيل ، على التوالي. على سبيل المثال ، ضع البرامج الثابتة في فلاش SPI ونظام التشغيل على NVME SSD.

استنساخ هذا الريبو وأدخل دليله ، أي:

git clone https://github.com/oreboot/oreboot.git

cd orebootبشكل عام ، ستحتاج إلى تثبيت الحزم التالية:

device-tree-compilerpkg-configlibsslrustup بالنسبة للأنظمة المستندة إلى Debian ، هناك هدف لجعل تثبيت تلك ، التي تسحب rustup من خلال حليقة من https://sh.rustup.rs:

make debiansysprepareخلاف ذلك ، قم بتثبيت الحزمة من خلال مدير حزمة النظام الخاص بك.

بغض النظر عن نظام التشغيل الخاص بك ، ستحتاج إلى تثبيت أدوات الأدوات لـ Oreboot. يجب القيام بهذا الأمر فقط مرة واحدة ولكن من الآمن القيام بذلك مرارًا وتكرارًا.

make firsttimeفي كل مرة تبدأ العمل مع Oreboot ، أو حتى يوميًا:

cd oreboot

make updateيجب عليك بالتأكيد القيام بذلك قبل الإبلاغ عن أي قضايا.

هناك شيئان مختلفان في المشروع:

src/mainboards/* الأهداف الفعلية ؛ هؤلاء يعتمدون على الصناديق ومشاركتها ، والتي يمكن أن تكون برامج تشغيل ، رمز init SOC ، ومماثلة. بالنسبة للألواح الرئيسية ، يجب تتبع Cargo.lock .src/* كل شيء آخر ؛ هذه هي الصناديق المذكورة أعلاه ، والتي لا نتعقب ملفات Cargo.lock . التحقق من ملف Cargo.lock من لوحة Mainboard. يسجل حالة تبعياته في وقت البناء الناجح ، مما يتيح التكاثر. من الناحية المثالية ، يتم تحديث ملف القفل follwoing التمهيد الناجح على الأجهزة.

لمعرفة المزيد ، راجع: https://doc.rust-lang.org/cargo/faq.html#why-do-binaries-have-cargolock-

عند إنشاء لوحة رئيسية جديدة ، فإن النظر إلى كيفية إعداد الآخرين لنفس الهندسة المعمارية يعد بداية جيدة. انتبه إلى أن Oreboot يستهدف المعدن العاري ، لذلك لا توجد مكتبة قياسية متاحة.

لبناء oreboot لمنصة معينة ، قم بذلك:

# Go to the mainboard's directory

cd src/mainboard/sunxi/nezha

# Build the mainboard target

make mainboard

# View disassembly

make objdump

# Run from RAM without flashing

make run

# Flash to the board

make flash

يسمح لك Makefile الجذر ببناء جميع المنصات بسرعة:

# build all mainboards

make mainboards

# build everything in parallel

make -j mainboards

# Install QEMU for your target platform, e.g. x86

sudo apt install qemu-system-x86

# Build release build and start with QEMU

cd src/mainboard/emulation/qemu-q35 && make run

# Quit qemu with CTRL-A X

لبناء QEMU من مصدر RISC-V:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-riscv64 && cd build-riscv64

../configure --target-list=riscv64-softmmu

make -j$(nproc)

# QEMU binary is at riscv64-softmmu/qemu-system-riscv64

لبناء QEMU من مصدر AARCH64:

git clone https://github.com/qemu/qemu && cd qemu

mkdir build-aarch64 && cd build-aarch64

../configure --target-list=aarch64-softmmu

make -j$(nproc)

# QEMU binary is at aarch64-softmmu/qemu-system-aarch64

على غرار CoreBoot ، الهيكل في oreboot هو لكل بائع ولوحة رئيسية. يتم دعم البنى المتعددة و SOCs على التوالي ، ويتم مشاركة رمزها المشترك بين المجالس. قد يكون للوحات متغيرات إذا كانت الانحرافات البسيطة قد تسبب الكثير من تكرار الكود.

qemu-riscvللرجوع إليها ، تم توثيق النهج السابقة. إلقاء نظرة على تلك الخاصة بمنصات X86 و ARM والألواح الرئيسية.

تم إيقاف أهداف المحاكاة السابقة في src.broken/mainboard/emulation/ . من المفترض أن يوفروا فهمًا عامًا لكل بنية تسعى Oreboot إلى دعمها:

qemu-armv7qemu-aarch64qemu-q35Makefile بسيطًا. استخدم xtask بدلاً من ذلك لتدفق التحكم ، على سبيل المثال ، إضافة رؤوس أو اختبارات إلى الثنائيات ، صور Sitchting ، إلخ ..Cargo.toml في أدلة src/mainboard/$VENDOR/$BOARD (Sub) بتبعيات خاصة بالوحة وبناء جميع المراحل بالتوازي.make format مع عدم وجود استثناءات. سيحدد فحص CI ما إذا كان التغيير لا يلتزم بقواعد التنسيق.حقوق الطبع والنشر على Oreboot مملوكة عدد كبير من المطورين والشركات الفردية. يرجى التحقق من ملفات المصدر الفردية للحصول على التفاصيل.

تم ترخيص Oreboot بموجب شروط رخصة GNU العامة العامة (GPL). يتم ترخيص بعض الملفات ضمن "GPL (الإصدار 2 ، أو أي إصدار لاحق)" ، وبعض الملفات مرخصة بموجب "GPL ، الإصدار 2". بالنسبة لبعض الأجزاء ، التي تم اشتقاقها من مشاريع أخرى ، قد يتم تطبيق تراخيص أخرى (متوافقة مع GPL). يرجى التحقق من ملفات المصدر الفردية للحصول على التفاصيل.

هذا يجعل صور Oreboot الناتجة مرخصة بموجب GPL ، الإصدار 2.