การมี FPGAs (อาร์เรย์ประตูที่สามารถจัดเรียงได้จากสนาม) มีอยู่ในศูนย์ข้อมูลแสดงให้เห็นถึงศักยภาพมหาศาลสำหรับโมเดลการคำนวณใหม่และน่าตื่นเต้น แต่สำหรับระบบนิเวศที่เกิดขึ้นใหม่นี้เราต้องการโครงสร้างพื้นฐานเพื่อพัฒนาตัวเร่งฮาร์ดแวร์ที่กำหนดเองสำหรับแพลตฟอร์มเหล่านี้และรวมเข้ากับเว็บแอปพลิเคชันและโครงสร้างพื้นฐานคลาวด์ Framework Claas 1st นำคลาวด์ FPGAs อยู่ไม่ไกลจากชุมชนโอเพนซอร์สสตาร์ทอัพและทุกคน

readme นี้ให้ภาพรวมของโครงการ นอกจากนี้ยังมีเอกสารต่อไปนี้ หลังจาก readme นี้รับมือกับ การเริ่มต้นใช้งาน

เพื่อการพัฒนาในท้องถิ่น:

สำหรับการเพิ่มประสิทธิภาพและการปรับใช้เคอร์เนลที่กำหนดเองของคุณโดยใช้ AWS F1 ด้วยเครื่องมือ Xilinx

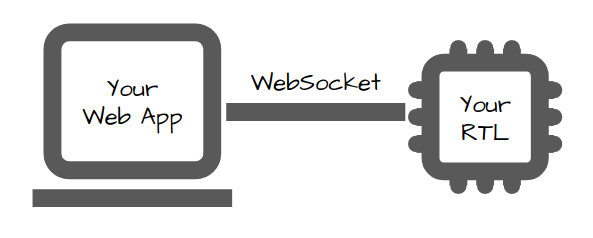

ด้วย CLAA ที่ 1 คุณสามารถสตรีมบิตโดยตรงไปยังและจากเคอร์เนล FPGA ที่กำหนดเองของคุณโดยใช้โปรโตคอลเว็บมาตรฐาน (WebSockets หรือ REST) ในกรณีการใช้งานที่ง่ายที่สุดซอฟต์แวร์ทั้งหมดอยู่ฝั่งไคลเอ็นต์ในเว็บเบราว์เซอร์และตรรกะเซิร์ฟเวอร์และการจัดเก็บข้อมูลทั้งหมดถูกนำไปใช้ใน FPGA เคอร์เนลของคุณใช้อินเทอร์เฟซที่ง่ายมากในการสตรีมข้อมูลและสามารถพัฒนาได้ใน Verilog (หรือภาษาใด ๆ ที่รวบรวมได้กับ Verilog)

CLAA ที่ 1 เหมาะสำหรับการใช้งานฟังก์ชั่นในฮาร์ดแวร์ที่มีการคำนวณ จำกัด แต่ทนต่อความล่าช้าทางอินเทอร์เน็ตและ bandwith แอปพลิเคชันที่ต้องการการแบ่งพาร์ติชันที่ซับซ้อนยิ่งขึ้นของความรับผิดชอบสามารถขยายรหัสโฮสต์ C ++ หรือเว็บเซิร์ฟเวอร์ Python เพื่อประมวลผลข้อมูลระหว่างเว็บแอปพลิเคชันและ FPGA

โดเมนแอปพลิเคชันที่เป็นไปได้อาจรวมถึง:

ใบสมัครของคุณอาจเป็น:

CLAAS 1st รองรับการพัฒนาเคอร์เนลฮาร์ดแวร์โดยใช้เครื่องมือฟรีและโอเพ่นซอร์สบน Linux (Ubuntu และ Centos ปัจจุบัน) ปัจจุบันการปรับใช้มีการกำหนดเป้าหมายไปยังอินสแตนซ์ F1 FPGA ของ Amazon เรายินดีต้อนรับการมีส่วนร่วมในการขยาย Claas ที่ 1 ไปยังแพลตฟอร์มอื่น ๆ และระบบปฏิบัติการ

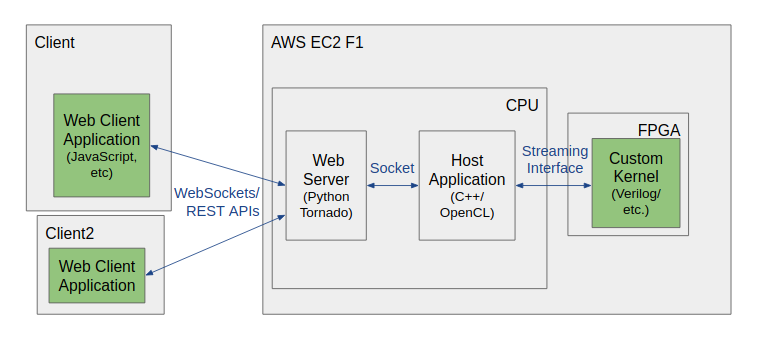

แอปพลิเคชันเว็บเร่งฮาร์ดแวร์ที่ใช้เฟรมเวิร์กนี้ประกอบด้วย::

ข้อมูลถูกส่งจากแอปพลิเคชันเว็บไคลเอ็นต์ในชิ้น 512 บิต (ปัจจุบัน) JavaScript เรียกวิธีการส่งและรับข้อมูลจากเคอร์เนลที่กำหนดเองในการโทรกลับ Custom Kernel มีอินเทอร์เฟซสตรีมมิ่งอย่างง่ายพร้อมบัส 512 บิตของข้อมูลอินพุตและบัส 512 บิตสำหรับข้อมูลเอาต์พุต ข้อมูลเดินทางจาก JavaScript:

ประสิทธิภาพการสื่อสารไม่ได้เป็นจุดสนใจในปัจจุบัน แอพพลิเคชั่นที่เหมาะสมกับสถาปัตยกรรมนี้มีการ จำกัด การคำนวณโดยเนื้อแท้ดังนั้นการเพิ่มประสิทธิภาพการสื่อสารจึงไม่สำคัญ แต่การใช้งานสามารถปรับให้เหมาะสมได้ตามความต้องการที่เกิดขึ้น

ในกรณีง่ายๆคุณให้เฉพาะส่วนประกอบสีเขียวในแผนภาพด้านบนและการประมวลผลข้อมูลที่กำหนดเองทั้งหมดดำเนินการโดยเคอร์เนลที่กำหนดเอง แต่แอปพลิเคชันโฮสต์ C ++/OpenCl และ/หรือเว็บเซิร์ฟเวอร์ Python สามารถขยายได้ตามที่ต้องการ

ก่อนหน้าโครงการนี้การรวมการเร่งความเร็วฮาร์ดแวร์ FPGA เข้ากับเว็บและแอพพลิเคชั่นคลาวด์เป็นงานที่น่ากลัวที่ต้องใช้:

ด้วยการจัดหาเว็บเซิร์ฟเวอร์รหัสแอปพลิเคชันโฮสต์และเคอร์เนลเชลล์ตรรกะเพื่อสตรีมข้อมูลระหว่างเว็บแอปพลิเคชันและเคอร์เนล FPGA รวมถึงการสร้างอินสแตนซ์และการกำหนดค่าคลาวด์โดยอัตโนมัติ CLAAS ที่ 1 ช่วยลดการทำงานของคุณเป็น:

[CC BY-SA 2.0, Lumaxart, Modified]

[CC BY-SA 2.0, Lumaxart, Modified]

ค่าใช้จ่ายในการพัฒนาโครงสร้างพื้นฐานจะลดลงจากหลายเดือนจนถึงชั่วโมง

เมื่อมองดูที่แพลตฟอร์ม Amazon F1 โดยเฉพาะ F1 ให้บริการเครื่องมือพัฒนา Xilinx FPGAs และ Xilinx ที่ทรงพลังในการจ่ายต่อการใช้งานซึ่งค่อนข้างน่าสนใจ แต่แพลตฟอร์มนั้นมีเลือดออกและต้องการความเชี่ยวชาญที่สำคัญในการใช้ประโยชน์ ประสบการณ์ของเราเกี่ยวกับแพลตฟอร์มนี้เป็นหนึ่งที่ค่อนข้างเจ็บปวด (และค่อนข้างแพง) ด้วยเหตุผลหลายประการ:

เราต้องผ่านความเจ็บปวดนี้ แต่เรารวมงานของเราดังนั้นคุณจะไม่ต้องทำ

เพื่อปรับปรุงการพัฒนาต่อไปลดต้นทุนและหลีกเลี่ยงการพึ่งพาแพลตฟอร์ม F1 และ Xilinx Tool Stack เราสนับสนุนการพัฒนาเครื่องจักรในพื้นที่ของคุณซึ่งเคอร์เนลได้รับการจำลองด้วยการจำลอง RTL โดยใช้เครื่องจำลอง RTL ของ Verilator Open-Source เครื่องมือ AWS และ Xilinx เป็นสิ่งจำเป็นสำหรับการเพิ่มประสิทธิภาพเคอร์เนลและการปรับใช้เท่านั้น ในฐานะที่เป็นโบนัสเพิ่มเติมการจำลอง Verilator ทำงานอย่างมีนัยสำคัญ (~ 100x?!) เร็วกว่าการจำลองโดยใช้การไหลของฮาร์ดแวร์ Xilinx "ส่วนหนึ่งเป็นเพราะ Verilator นั้นเร็วและบางส่วนเพราะเราจำลองเคอร์เนลที่กำหนดเองเท่านั้น

การลดปัญหาในการพัฒนาเว็บและการพัฒนา RTL ไม่ใช่เส้นชัยสำหรับเรา 1st Claas เป็นส่วนหนึ่งของความพยายามที่กว้างขึ้นในการกำหนดอุตสาหกรรมซิลิคอนใหม่และนำซิลิคอนมาสู่มวลชน การผ่านความซับซ้อนของการสร้างแบบจำลอง RTL เป็นส่วนหนึ่งของสิ่งนั้น 1st Claas ถูกขับเคลื่อนโดยผู้สนับสนุนตัวยงของ TL-Verilog ร่วมกับ Redwood EDA TL-Verilog แนะนำวิธีการออกแบบวงจรดิจิตอลที่จำเป็นมากด้วยการสร้างแบบจำลองที่ง่ายและมีประสิทธิภาพยิ่งขึ้น Claas ที่ 1 ไม่ได้ผูกติดอยู่กับ TL-Verilog คุณสามารถใช้ Verilog/SystemVerilog หรือภาษาคำอธิบายฮาร์ดแวร์ใด ๆ ที่สามารถเปลี่ยนเป็น Verilog ได้ แต่ส่วนขยายของ TL-Verilog lnguage ได้รับการสนับสนุนนอกกรอบและเราขอแนะนำให้คุณใช้ประโยชน์จากพวกเขาและช่วยเราขับเคลื่อนนวัตกรรมนี้ไปข้างหน้า Redwood EDA ให้บริการ IDE ออนไลน์ฟรีสำหรับการพัฒนา TL-Verilog ที่ makerchip.com คุณสามารถค้นหาสื่อการฝึกอบรมใน IDE อ่านเรื่องราวที่สมบูรณ์มากขึ้นจาก Steve Hoover ผู้ก่อตั้ง Redwood EDA

ในเชิงพาณิชย์ CLAAS 1 ถูกใช้โดย Tripputer, Inc. เพื่อให้การจำแนกข้อมูลแบบไดนามิกของข้อมูลสตรีมมิ่ง

1ST CLAAS แสดงผล Fractals เรียลไทม์สำหรับ fractalvalley.net

พื้นที่เก็บข้อมูลนี้ใช้งานได้โดยทั่วไปและการผลักดันการพัฒนาเบื้องต้นกำลังคดเคี้ยว

ทุกอย่างและทุกอย่างอาจมีการเปลี่ยนแปลง ณ จุดนี้โดยเฉพาะอย่างยิ่งเกี่ยวกับอินเทอร์เฟซที่จัดทำโดยเฟรมเวิร์กเพื่อให้แอปพลิเคชันสร้างขึ้น ดังนั้นคุณควรสร้างเฟรมเวิร์กรุ่นเฉพาะและคาดว่าจะทำการดีบักบางอย่างหากคุณเลือกที่จะอัพเกรดโดยการดึงจากอาจารย์

อืม ... เรายังไม่ได้คิดมาก แค่พูดอะไรดีๆและเราจะมีความสุข

เครื่องหมายการค้าทั้งหมดที่อ้างถึงภายในที่เก็บนี้เป็นทรัพย์สินของเจ้าของที่เกี่ยวข้อง