데이터 센터에서 FPGA (Field-Progammable Gate Array)를 사용할 수 있으면 새롭고 흥미로운 컴퓨팅 모델에 대한 엄청난 잠재력이 나타납니다. 그러나이 새로운 생태계가 번성하기 위해서는 이러한 플랫폼에 대한 사용자 정의 하드웨어 가속기를 개발하고 웹 응용 프로그램 및 클라우드 인프라와 통합하기위한 인프라가 필요합니다. 첫 번째 Claas 프레임 워크는 Open-Source 커뮤니티, 스타트 업 및 모든 사람의 범위 내에서 Cloud FPGA를 제공합니다.

이 readme는 프로젝트에 대한 개요를 제공합니다. 다음 문서도 제공됩니다. 이 readme 후에 시작하기 시작 하면서 손을 뻗으십시오.

지역 개발을 위해 :

XilInx 도구와 함께 AWS F1을 사용하여 사용자 정의 커널의 최적화 및 배포를 위해.

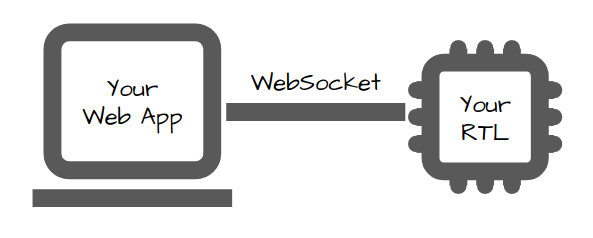

1st Claas를 사용하면 표준 웹 프로토콜 (Websockets 또는 REST)을 사용하여 사용자 정의 FPGA 커널로 직접 비트를 스트리밍 할 수 있습니다. 가장 간단한 유스 케이스에서 모든 소프트웨어는 웹 브라우저의 클라이언트면이며 모든 서버 로직 및 데이터 저장소는 FPGA에서 구현됩니다. 커널은 매우 간단한 인터페이스를 사용하여 데이터를 스트리밍하며 Verilog (또는 Verilog에 편집 할 수있는 언어)에서 개발할 수 있습니다.

1st Claas는 컴퓨팅 제한이지만 인터넷 대기 시간 및 대역에 허용되는 하드웨어에서 기능을 구현하는 데 이상적입니다. 보다 정교한 분할이 필요한 응용 프로그램은 호스트 C ++ 코드 또는 Python 웹 서버를 확장하여 웹 응용 프로그램과 FPGA 간의 데이터를 처리 할 수 있습니다.

가능한 응용 프로그램 도메인에는 다음이 포함될 수 있습니다.

귀하의 응용 프로그램은 다음과 같습니다.

1st Claas는 Linux (Ubuntu 및 Centos, 현재)에서 무료 및 오픈 소스 도구를 사용하여 하드웨어 커널 개발을 지원합니다. 배포는 현재 Amazon의 F1 FPGA 인스턴스를 대상으로합니다. 우리는 1st Claas를 다른 플랫폼 및 운영 체제로 확장하기위한 기여를 환영합니다.

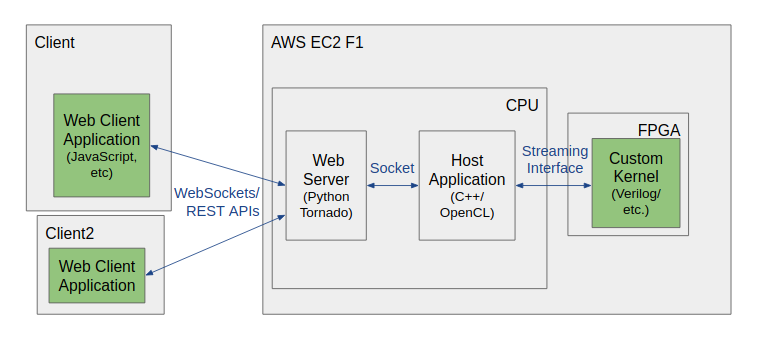

이 프레임 워크를 사용하는 하드웨어 가속 웹 애플리케이션은 다음으로 구성됩니다.

데이터는 웹 클라이언트 응용 프로그램에서 512 비트 (현재)의 청크로 전송됩니다. JavaScript는 보내기 메소드를 호출하고 콜백에서 사용자 정의 커널에서 데이터를 수신합니다. Custom Kernel에는 512 비트의 입력 데이터 버스와 출력 데이터를 위해 512 비트 버스가있는 간단한 스트리밍 인터페이스가 있습니다. JavaScript에서 데이터 여행 :

커뮤니케이션 성능은 현재 초점이 아닙니다. 이 아키텍처에 적합한 애플리케이션은 본질적으로 계산 제한이므로 커뮤니케이션을 최적화하는 것은 종종 중요하지 않지만 구현은 필요에 따라 최적화 될 수 있습니다.

간단한 경우 위의 다이어그램에서 녹색 구성 요소 만 제공하며 모든 사용자 정의 데이터 처리는 사용자 정의 커널에 의해 수행됩니다. 그러나 C ++/OpenCL 호스트 애플리케이션 및/또는 Python 웹 서버는 원하는대로 확장 될 수 있습니다.

이 프로젝트 전에는 FPGA 하드웨어 가속을 웹 및 클라우드 애플리케이션과 통합하는 것이 필요했습니다.

웹 서버, 호스트 애플리케이션 코드 및 커널 쉘 로직을 제공하여 클라우드 인스턴스 생성 및 구성을 자동화 할뿐만 아니라 웹 애플리케이션과 FPGA 커널 사이의 데이터를 스트리밍하여 1st Claas를 제공합니다.

[CC By-SA 2.0, Lumaxart, 수정]

[CC By-SA 2.0, Lumaxart, 수정]

인프라 개발 오버 헤드는 여러 사람에서 몇 시간으로 줄어 듭니다.

F1은 Amazon F1 플랫폼을 구체적으로 살펴보면 강력한 Xilinx FPGA 및 Xilinx Development Tools를 사용하여 유료로 제공합니다. 그러나 플랫폼은 출혈 에지이며 활용하려면 상당한 전문 지식이 필요합니다. 이 플랫폼에 대한 우리의 경험은 여러 가지 이유로 다소 고통스럽고 다소 비싸다.

우리는이 고통을 겪어야했지만, 우리는 당신이 할 필요가 없도록 우리의 일을 번들로 묶었습니다.

개발 개발을 더욱 간소화하고 비용을 줄이며 F1 플랫폼 및 Xilinx 도구 스택에 대한 의존성을 피하기 위해 Verilator Open-Source RTL 시뮬레이터를 사용하여 커널이 RTL 시뮬레이션으로 모방되는 로컬 시스템의 개발을 지원합니다. AWS 및 Xilinx 도구는 커널 최적화 및 배포에만 필요합니다. 추가 보너스로서 Verilator Simulation은 Xilinx "하드웨어 에뮬레이션 흐름"을 사용하여 시뮬레이션보다 훨씬 빠르고 (~ 100x?!) 더 빠르게 실행됩니다. Verilator는 크고 부분적으로 커스크를 둘러싼 쉘 로직을 포함하지 않기 때문에 Verilator가 빠르고 부분적으로는 빠르기 때문에 부분적으로 실행됩니다.

웹 및 RTL 개발로 문제를 줄이는 것은 결승선이 아닙니다. 1st Claas는 실리콘 산업을 재정의하고 실리콘을 대중에게 가져 오려는 광범위한 노력의 일부입니다. RTL 모델링의 복잡성을 극복하는 것이 그 일부입니다. 1st Claas는 Redwood Eda와 관련하여 TL-Verilog의 열렬한 지지자들에 의해 운전됩니다. TL-Verilog는 더 단순하고 강력한 모델링 구성으로 필요한 디지털 회로 설계 방법론 이동을 도입합니다. 1st Claas는 TL-Verilog에 묶이지 않습니다. Verilog/SystemVerilog 또는 Verilog로 바꿀 수있는 하드웨어 설명 언어를 사용할 수 있습니다. 그러나 TL-Verilog lnguage 확장은 상자 밖으로 지원되며,이를 활용 하고이 혁신을 추진하도록 도와주는 것이 좋습니다. Redwood EDA는 Makerchip.com에서 TL-Verilog Development를위한 무료 온라인 IDE를 제공합니다. IDE에서 교육 자료를 찾을 수 있습니다. Redwood Eda 창립자 Steve Hoover의보다 완전한 이야기를 읽으십시오.

상업적으로, 1st Claas는 Stringputer, Inc.에서 스트리밍 데이터의 동적 분류를 제공하기 위해 사용됩니다.

1st Claas는 FractalValley.net의 실시간 프랙탈을 렌더링합니다.

이 저장소는 일반적으로 작동하며 초기 개발 푸시가 감소하고 있습니다.

이 시점에서 모든 것이 변경 될 수 있으며, 특히 응용 프로그램을 구축하기위한 프레임 워크가 제공하는 인터페이스와 관련하여 변경 될 수 있습니다. 따라서 특정 버전의 프레임 워크를 구축하고 마스터에서 끌어 당겨 업그레이드하기로 선택한 경우 디버깅을해야합니다.

흠 ... 우리는 아직 그렇게 많은 생각을하지 않았다. 좋은 말을하면 행복 할 것입니다.

이 저장소 내에서 인용 된 모든 상표는 해당 소유자의 속성입니다.