Tener FPGA (matrices de puerta progammables de campo) disponibles en el centro de datos presenta un enorme potencial para modelos de cómputo nuevos y emocionantes. Pero, para que este ecosistema emergente prospere, necesitamos infraestructura para desarrollar aceleradores de hardware personalizados para estas plataformas e integrarlos con aplicaciones web e infraestructura en la nube. El primer marco de Claas lleva a Cloud FPGA al alcance de la comunidad de código abierto, nuevas empresas y todos.

Este ReadMe proporciona una visión general del proyecto. Los siguientes documentos también están disponibles. Después de este readme, comprenda la mano con comenzar .

Para el desarrollo local:

Para la optimización e implementación de su núcleo personalizado utilizando AWS F1 con herramientas Xilinx.

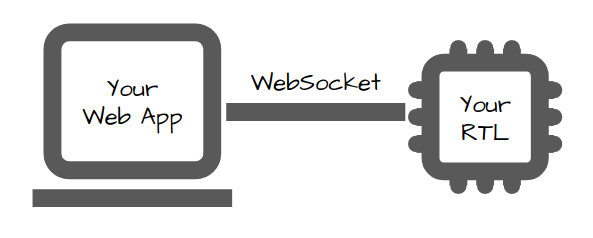

Con el 1er CLAA, puede transmitir bits directamente hacia y desde su núcleo FPGA personalizado utilizando protocolos web estándar (websockets o REST). En el caso de uso más simple, todo el software es del lado del cliente en el navegador web, y toda la lógica del servidor y el almacenamiento de datos se implementan en el FPGA. Su kernel utiliza una interfaz muy simple para transmitir los datos, y se puede desarrollar en Verilog (o cualquier lenguaje compilable para Verilog).

1st Claas es ideal para implementar funciones en hardware que son limitadas por cómputo pero tolerantes a la latencia de Internet y la banda. Las aplicaciones que requieren una partición más sofisticada de las responsabilidades pueden extender el código Host C ++ o el servidor web de Python para procesar datos entre la aplicación web y FPGA.

Los posibles dominios de la aplicación pueden incluir:

Su aplicación podría ser:

1st Claas admite el desarrollo del núcleo de hardware utilizando herramientas de código libre y de código abierto en Linux (Ubuntu y CentOS, actualmente). La implementación está actualmente dirigida a las instancias F1 FPGA de Amazon. Agradecemos contribuciones para extender el 1er CLAA a otras plataformas y sistemas operativos.

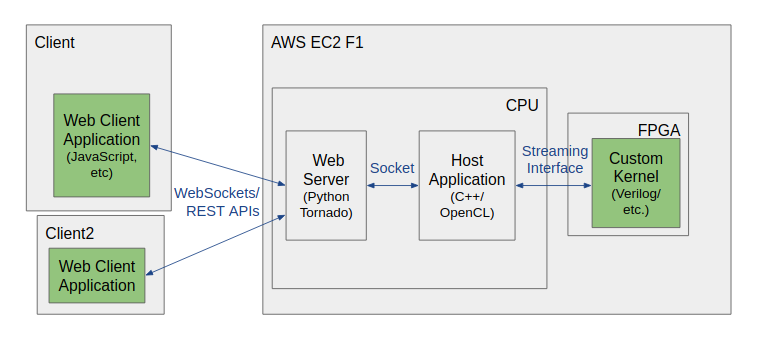

Una aplicación web acelerada de hardware que utiliza este marco consiste en:

Los datos se transmiten desde la aplicación del cliente web en fragmentos de 512 bits (actualmente). JavaScript llama a un método de envío y recibe datos del kernel personalizado en una devolución de llamada. El kernel personalizado tiene una interfaz de transmisión simple con un bus de datos de entrada de 512 bits y un bus de 512 bits para datos de salida. Viajes de datos desde JavaScript:

El rendimiento de la comunicación no es actualmente el foco. Las aplicaciones que se adaptan bien a esta arquitectura son inherentemente limitadas por el cálculo, por lo que optimizar la comunicación a menudo no es importante, pero la implementación puede optimizarse a medida que surge la necesidad.

En el caso simple, usted solo proporciona los componentes verdes en el diagrama anterior, y el núcleo personalizado realiza todo el procesamiento personalizado de datos. Pero la aplicación host C ++/OpenCL y/o el servidor web de Python se pueden extender según lo desee.

Antes de este proyecto, la integración de la aceleración de hardware FPGA con aplicaciones web y en la nube fue una empresa desalentadora que requirió:

Al proporcionar el servidor web, el código de la aplicación de host y la lógica del kernel shell para transmitir los datos entre la aplicación web y el núcleo FPGA, así como la automatización de la creación y configuración de instancias en la nube, el 1er Claas reduce su trabajo a:

[CC BY-SA 2.0, Lumaxart, modificado]

[CC BY-SA 2.0, Lumaxart, modificado]

La sobrecarga de desarrollo de infraestructura se reduce de varios meses de personas a horas.

Mirando específicamente la plataforma Amazon F1, F1 proporciona potentes herramientas de desarrollo de Xilinx FPGA y Xilinx sobre una base de pago por uso, que es bastante convincente. Pero la plataforma es sangrante y requiere una experiencia significativa para utilizar. Nuestra experiencia con esta plataforma ha sido bastante dolorosa (y algo costosa) por varias razones:

Tuvimos que pasar por este dolor, pero agrupamos nuestro trabajo para que no tuviera que hacerlo.

Para optimizar aún más el desarrollo, reducir los costos y evitar cualquier dependencia de la plataforma F1 y la pila de herramientas Xilinx, admitimos el desarrollo de su máquina local donde el kernel se emula con simulación RTL utilizando el simulador RTL de código abierto Verilator. Las herramientas AWS y Xilinx solo se requieren para la optimización y la implementación del núcleo. Como una ventaja adicional, la simulación de verilator funciona significativamente (~ 100x?

Reducir el problema al desarrollo web y RTL no es la línea de meta para nosotros. 1st Claas es parte de un esfuerzo más amplio para redefinir la industria de silicio y traer silicio a las masas. Pasar las complejidades del modelado RTL es parte de eso. El 1er Claas es impulsado por ávidos partidarios de TL-Verilog, en asociación con Redwood EDA. TL-Verilog presenta un cambio de metodología de diseño de circuito digital muy necesario con construcciones de modelado más simples y potentes. El 1er Claas de ninguna manera está vinculado a TL-VERILOG. Puede usar Verilog/SystemVerilog o cualquier idioma de descripción de hardware que pueda convertirse en Verilog. Pero las extensiones TL-VERILOG LNGUGE son compatibles con la caja, y le recomendamos encarecidamente que se aproveche de ellas y nos ayude a impulsar esta innovación. Redwood EDA proporciona un IDE gratuito en línea para el desarrollo de TL-Verilog en makerchip.com. Puede encontrar materiales de capacitación en el IDE. Lea la historia más completa del fundador de Redwood EDA, Steve Hoover.

Comercialmente, el primer CLAA es utilizado por Worler, Inc. para proporcionar una clasificación dinámica de los datos de transmisión.

El 1er Claas representa fractales en tiempo real para fractalvalley.net.

Este repositorio generalmente está funcionando, y el empuje de desarrollo inicial está disminuyendo.

Cualquier cosa y todo está sujeto a cambios en este punto, especialmente con respecto a la interfaz proporcionada por el marco para las aplicaciones para construir. Por lo tanto, debe aprovechar una versión específica del marco y esperar hacer una depuración si elige actualizar al sacar del maestro.

Hmmmm ... todavía no hemos pensado tanto. Solo diga algo bueno y seremos felices.

Todas las marcas comerciales citadas dentro de este repositorio son propiedad de sus respectivos propietarios.