Memiliki FPGA (array gerbang yang dapat diprogammable) tersedia di pusat data menyajikan potensi besar untuk model komputasi baru dan menarik. Tetapi, untuk ekosistem yang muncul ini untuk berkembang, kita membutuhkan infrastruktur untuk mengembangkan akselerator perangkat keras khusus untuk platform ini dan mengintegrasikannya dengan aplikasi web dan infrastruktur cloud. Kerangka kerja CLAAS pertama membawa Cloud FPGA dalam jangkauan komunitas open-source, startup, dan semua orang.

Readme ini memberikan gambaran tentang proyek. Dokumen -dokumen berikut juga tersedia. Setelah readme ini, bersiaplah dengan memulai .

Untuk pengembangan lokal:

Untuk optimasi dan penyebaran kernel khusus Anda menggunakan AWS F1 dengan alat Xilinx.

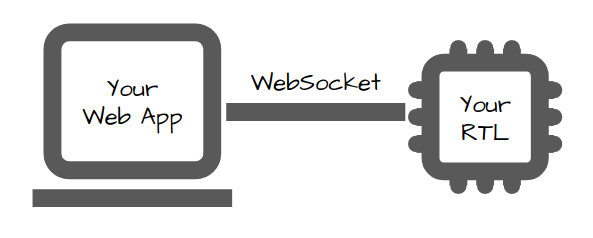

Dengan 1st CLAA, Anda dapat melakukan streaming bit langsung ke dan dari kernel FPGA khusus Anda menggunakan protokol web standar (websockets atau istirahat). Dalam kasus penggunaan yang paling sederhana, semua perangkat lunak adalah sisi klien di browser web, dan semua logika server dan penyimpanan data diimplementasikan dalam FPGA. Kernel Anda menggunakan antarmuka yang sangat sederhana untuk mengalirkan data, dan dapat dikembangkan di Verilog (atau bahasa apa pun yang dapat dikompilasi untuk Verilog).

1ST CLAAS sangat ideal untuk menerapkan fungsi dalam perangkat keras yang terbatas komputasi tetapi toleran terhadap latensi internet dan bandwith. Aplikasi yang membutuhkan partisi tanggung jawab yang lebih canggih dapat memperluas kode C ++ host atau server web Python untuk memproses data antara aplikasi web dan FPGA.

Kemungkinan domain aplikasi mungkin termasuk:

Aplikasi Anda mungkin:

1st CLAAS mendukung pengembangan kernel perangkat keras menggunakan alat sumber terbuka dan terbuka di Linux (Ubuntu dan Centos, saat ini). Penyebaran saat ini ditargetkan untuk instance FPGA F1 Amazon. Kami menyambut kontribusi untuk memperluas CLAA 1 ke platform lain dan sistem operasi.

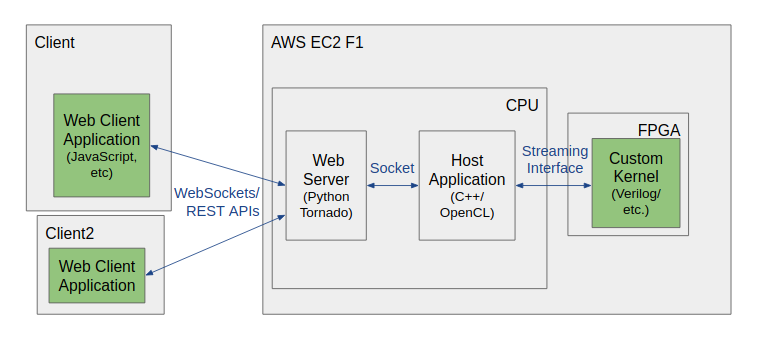

Aplikasi web yang dipercepat perangkat keras yang menggunakan kerangka kerja ini terdiri dari:

Data ditransmisikan dari aplikasi klien web dalam potongan 512 bit (saat ini). JavaScript memanggil metode Kirim dan menerima data dari kernel khusus dalam panggilan balik. Kernel khusus memiliki antarmuka streaming sederhana dengan bus 512bit dari data input dan bus 512-bit untuk data output. Data bepergian dari JavaScript:

Kinerja komunikasi saat ini tidak menjadi fokus. Aplikasi yang cocok untuk arsitektur ini secara inheren terbatas, sehingga komunikasi yang dioptimalkan seringkali tidak penting, tetapi implementasinya dapat dioptimalkan saat kebutuhan muncul.

Dalam kasus sederhana, Anda hanya menyediakan komponen hijau dalam diagram di atas, dan semua pemrosesan data khusus dilakukan oleh kernel khusus. Tetapi aplikasi host C ++/OpenCL dan/atau server web Python dapat diperpanjang seperti yang diinginkan.

Sebelum proyek ini, mengintegrasikan akselerasi perangkat keras FPGA dengan aplikasi web dan cloud adalah upaya yang menakutkan yang membutuhkan:

Dengan menyediakan server web, kode aplikasi host, dan logika shell kernel untuk mengalirkan data antara aplikasi web dan kernel FPGA serta mengotomatisasi pembuatan dan konfigurasi instance cloud, CLAAS pertama mengurangi pekerjaan Anda menjadi:

[CC BY-SA 2.0, Lumaxart, dimodifikasi]

[CC BY-SA 2.0, Lumaxart, dimodifikasi]

Overhead pengembangan infrastruktur berkurang dari beberapa bulan ke jam.

Melihat secara khusus pada platform Amazon F1, F1 menyediakan alat pengembangan Xilinx FPGA dan Xilinx yang kuat berdasarkan bayar per penggunaan, yang cukup menarik. Tetapi platform ini mendarahi tepi dan membutuhkan keahlian yang signifikan untuk digunakan. Pengalaman kami dengan platform ini telah menjadi yang agak menyakitkan (dan agak mahal) karena beberapa alasan:

Kami harus melalui rasa sakit ini, tetapi kami menggabungkan pekerjaan kami sehingga Anda tidak perlu melakukannya.

Untuk merampingkan pengembangan lebih lanjut, mengurangi biaya, dan menghindari ketergantungan pada platform F1 dan tumpukan alat Xilinx, kami mendukung pengembangan pada mesin lokal Anda di mana kernel ditiru dengan simulasi RTL menggunakan simulator RTL sumber terbuka verilator. Alat AWS dan Xilinx hanya diperlukan untuk optimasi dan penyebaran kernel. Sebagai bonus tambahan, simulasi verilator berjalan secara signifikan (~ 100x?!) Lebih cepat daripada simulasi menggunakan xilinx "aliran emulasi perangkat keras," sebagian karena verilator cepat dan sebagian karena kami hanya mensimulasikan kernel khusus, tidak termasuk logika shell yang mengelilingi kernel.

Mengurangi masalah untuk pengembangan Web dan RTL bukanlah garis finish bagi kami. 1 CLAAS adalah bagian dari upaya yang lebih luas untuk mendefinisikan kembali industri silikon dan membawa silikon ke massa. Melewati kompleksitas pemodelan RTL adalah bagian dari itu. 1ST CLAAS didorong oleh pendukung Avid TL-Verilog, bekerja sama dengan Redwood EDA. TL-Verilog memperkenalkan pergeseran metodologi desain sirkuit digital yang sangat dibutuhkan dengan konstruksi pemodelan yang lebih sederhana dan lebih kuat. 1 CLAAS sama sekali tidak terkait dengan TL-Verilog. Anda dapat menggunakan Verilog/SystemVerilog atau bahasa deskripsi perangkat keras apa pun yang dapat diubah menjadi Verilog. Tetapi ekstensi lnguage TL-Verilog didukung di luar kotak, dan kami sangat mendorong Anda untuk memanfaatkannya dan membantu kami mendorong inovasi ini ke depan. Redwood EDA menyediakan IDE online gratis untuk pengembangan TL-Verilog di MakerChip.com. Anda dapat menemukan materi pelatihan di IDE. Baca kisah yang lebih lengkap dari pendiri Redwood EDA, Steve Hoover.

Secara komersial, CLAA 1 digunakan oleh Throughputer, Inc. untuk memberikan klasifikasi dinamis data streaming.

1st Claas membuat fraktal realtime untuk fractalvalley.net.

Repositori ini umumnya berfungsi, dan dorongan pengembangan awal mereda.

Apa saja dan semuanya dapat berubah pada saat ini, terutama sehubungan dengan antarmuka yang disediakan oleh kerangka kerja untuk aplikasi untuk dibangun. Jadi, Anda harus membangun versi kerangka kerja tertentu dan berharap untuk melakukan beberapa debugging jika Anda memilih untuk meningkatkan dengan menarik dari master.

Hmmmm ... kami belum memikirkan sebanyak itu. Katakan saja sesuatu yang menyenangkan, dan kami akan bahagia.

Semua merek dagang yang dikutip dalam repositori ini adalah milik pemiliknya masing -masing.