Ter FPGAs (matrizes de portões progamíveis de campo) disponível no data center apresenta um enorme potencial para modelos de computação novos e emocionantes. Mas, para que esse ecossistema emergente prospere, precisamos de infraestrutura para desenvolver aceleradores de hardware personalizados para essas plataformas e integrá -los a aplicativos da Web e infraestrutura em nuvem. A 1ª estrutura do CLAAS traz FPGAs em nuvem ao alcance da comunidade de código aberto, startups e todos.

Este ReadMe fornece uma visão geral do projeto. Os seguintes documentos também estão disponíveis. Após esse readme, fique de mãos dadas para começar .

Para desenvolvimento local:

Para otimização e implantação do seu kernel personalizado usando o AWS F1 com as ferramentas Xilinx.

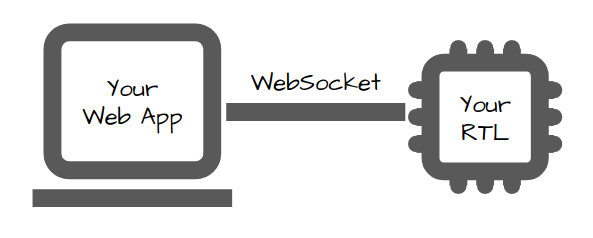

Com o 1º CLAAS, você pode transmitir bits diretamente para e para o seu kernel FPGA personalizado usando protocolos da Web padrão (Websockets ou REST). No caso de uso mais simples, todo o software é do lado do cliente no navegador da Web e toda a lógica do servidor e o armazenamento de dados são implementados no FPGA. Seu kernel usa uma interface muito simples para transmitir os dados e pode ser desenvolvida no Verilog (ou em qualquer idioma compilável ao Verilog).

O 1º CLAAS é ideal para implementar funções em hardware que são limitados por computação, mas tolerantes à latência da Internet e à banda. Os aplicativos que exigem uma partição mais sofisticada de responsabilidades podem estender o código C ++ do host ou o servidor da Web Python para processar dados entre o aplicativo da Web e o FPGA.

Possíveis domínios de aplicação podem incluir:

Seu aplicativo pode ser:

O 1st Claas suporta o desenvolvimento do kernel de hardware usando ferramentas gratuitas e de código aberto no Linux (Ubuntu e CentOS, atualmente). Atualmente, a implantação é direcionada para as instâncias F1 FPGA da Amazon. Congratulamo -nos com contribuições para estender o 1º CLAAS a outras plataformas e sistemas operacionais.

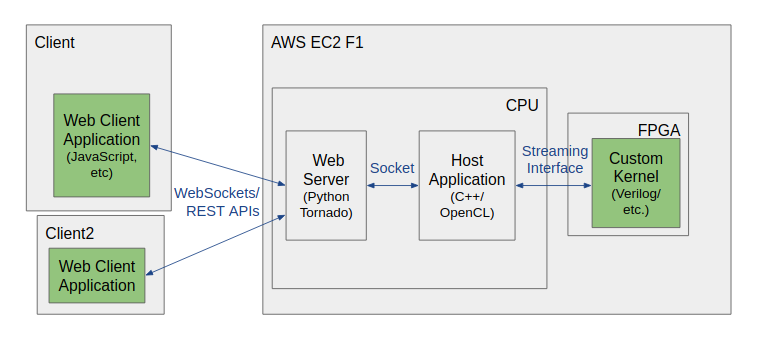

Um aplicativo da web acelerado de hardware utilizando essa estrutura consiste em:

Os dados são transmitidos a partir do aplicativo Web Client em pedaços de 512 bits (atualmente). O JavaScript chama um método de envio e recebe dados do kernel personalizado em um retorno de chamada. O kernel personalizado possui uma interface de streaming simples com um barramento de 512 bits de dados de entrada e um barramento de 512 bits para dados de saída. Os dados viajam do JavaScript:

Atualmente, o desempenho da comunicação não é o foco. Os aplicativos que são adequados a essa arquitetura são inerentemente limitados, portanto, a otimizar a comunicação geralmente não é importante, mas a implementação pode ser otimizada à medida que surgir a necessidade.

No caso simples, você fornece apenas os componentes verdes no diagrama acima e todo o processamento personalizado de dados é realizado pelo kernel personalizado. Mas o aplicativo host C ++/OpenCL e/ou o servidor Web Python podem ser estendidos conforme desejado.

Antes deste projeto, a integração da aceleração de hardware do FPGA com aplicativos da Web e em nuvem era um empreendimento assustador exigindo:

Ao fornecer o servidor da web, o código do aplicativo de host e a lógica do shell do kernel para transmitir os dados entre o aplicativo da web e o kernel do FPGA, além de automatizar a criação e configuração de instância em nuvem, o 1º Claas reduz seu trabalho para:

[CC BY-SA 2.0, LumaXart, modificado]

[CC BY-SA 2.0, LumaXart, modificado]

O sobrecarga do desenvolvimento de infraestrutura é reduzido de vários meses de idade para horas.

Observando especificamente a plataforma Amazon F1, a F1 fornece poderosas ferramentas de desenvolvimento Xilinx FPGAs e Xilinx em uma base de pagamento por uso, o que é bastante atraente. Mas a plataforma está sangrando e requer experiência significativa para utilizar. Nossa experiência com esta plataforma tem sido bastante dolorosa (e um tanto cara) por vários motivos:

Tivemos que passar por essa dor, mas agrupamos nosso trabalho para que você não precisasse.

Para otimizar ainda mais o desenvolvimento, reduzir o custo e evitar qualquer dependência da plataforma F1 e da pilha de ferramentas Xilinx, apoiamos o desenvolvimento da sua máquina local, onde o kernel é emulado com simulação RTL usando o simulador RTL de código aberto verilator. As ferramentas AWS e XILINX são necessárias apenas para a otimização e implantação do kernel. Como um bônus adicional, a simulação verilator funciona significativamente (~ 100x?!) Mais rápida que a simulação usando o fluxo de emulação de hardware Xilinx, em parte porque o verilator é rápido e em parte porque simulamos apenas o kernel personalizado, sem incluir a lógica da concha em torno do kernel.

Reduzir o problema para o desenvolvimento da Web e RTL não é a linha de chegada para nós. O 1º Claas faz parte de um esforço mais amplo para redefinir a indústria de silício e levar o silício para as massas. Superar as complexidades da modelagem RTL faz parte disso. O 1º Claas é impulsionado por ávidos apoiadores do TL-Verilog, em associação com Redwood EDA. A TL-Verilog apresenta uma mudança de metodologia de design de circuito digital muito necessário com construções de modelagem mais simples e mais poderosas. O 1º Claas não está de forma alguma ligado ao TL-Verilog. Você pode usar o Verilog/SystemVerilog ou qualquer idioma de descrição do hardware que possa ser transformado em Verilog. Mas as extensões do TL-Verilog LnGuage são suportadas para fora da caixa, e recomendamos fortemente que você a aproveite e nos ajude a impulsionar essa inovação. A Redwood EDA fornece um IDE online gratuito para o desenvolvimento da TL-Verilog em Makerchip.com. Você pode encontrar materiais de treinamento no IDE. Leia a história mais completa do fundador da Redwood EDA, Steve Hoover.

Comercialmente, o 1º CLAAS é usado pelo rendimento, Inc. para fornecer classificação dinâmica de dados de streaming.

O 1º Claas renderiza fractais em tempo real para FractalValley.net.

Esse repositório geralmente está funcionando, e o impulso inicial do desenvolvimento está diminuindo.

Tudo e qualquer coisa está sujeita a alteração neste momento, especialmente com relação à interface fornecida pela estrutura para os aplicativos se basearem. Portanto, você deve desenvolver uma versão específica da estrutura e esperar fazer alguma depuração se optar por atualizar, retirando -se do mestre.

Hmmmm ... ainda não pensamos tanto. Basta dizer algo bom, e ficaremos felizes.

Todas as marcas registradas citadas neste repositório são propriedade de seus respectivos proprietários.