データセンターで利用可能なFPGA(フィールドプロガンマブルゲートアレイ)を使用すると、新しいエキサイティングなコンピューティングモデルに大きな可能性があります。しかし、この新しいエコシステムが繁栄するためには、これらのプラットフォームのカスタムハードウェアアクセラレータを開発し、それらをWebアプリケーションおよびクラウドインフラストラクチャと統合するためのインフラストラクチャが必要です。最初のCLAASフレームワークは、オープンソースコミュニティ、スタートアップ、およびすべての人の範囲内にクラウドFPGAをもたらします。

このREADMEは、プロジェクトの概要を提供します。次のドキュメントも利用できます。このreadmeの後、開始して手に入れてください。

ローカル開発のため:

Xilinxツールを使用してAWS F1を使用してカスタムカーネルを最適化して展開するため。

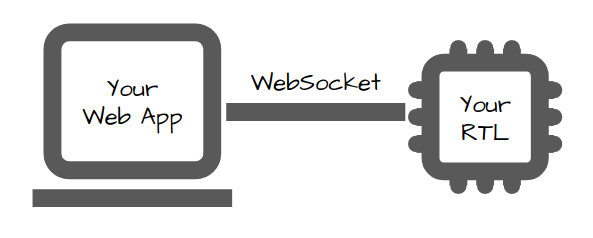

1番目のCLAAを使用すると、標準のWebプロトコル(WebSocketまたはREST)を使用して、カスタムFPGAカーネルと直接ビットをストリーミングできます。最も単純なユースケースでは、すべてのソフトウェアはWebブラウザーのクライアント側であり、すべてのサーバーロジックとデータストレージがFPGAに実装されています。カーネルは非常にシンプルなインターフェイスを使用してデータをストリーミングし、Verilog(またはVerilogに統合可能な言語)で開発できます。

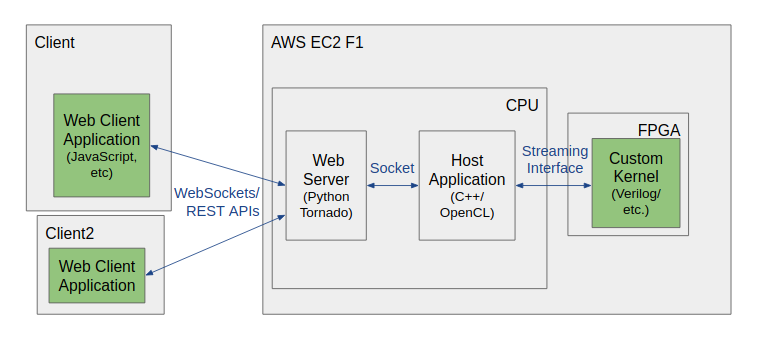

1番目のCLAASは、計算が制限されているがインターネットの遅延や帯域に耐性のあるハードウェアに関数を実装するのに最適です。より洗練された責任のパーティションを必要とするアプリケーションでは、ホストC ++コードまたはPython Webサーバーを拡張して、WebアプリケーションとFPGA間のデータを処理できます。

可能なアプリケーションドメインには以下が含まれる場合があります。

あなたのアプリケーションは次のかもしれません:

第1 Claasは、Linux(現在はUbuntuとCentos、Centos)の無料およびオープンソースツールを使用して、ハードウェアカーネル開発をサポートしています。展開は現在、AmazonのF1 FPGAインスタンスを対象としています。第1 Claasを他のプラットフォームやオペレーティングシステムに拡張するための貢献を歓迎します。

このフレームワークを使用して、ハードウェアが加速されたWebアプリケーションは次のとおりです。

データは、512ビット(現在)のチャンクでWebクライアントアプリケーションから送信されます。 JavaScriptは送信メソッドを呼び出し、コールバックでカスタムカーネルからデータを受信します。カスタムカーネルには、入力データの512ビットバスと、出力データ用の512ビットバスを備えたシンプルなストリーミングインターフェイスがあります。データはJavaScriptから移動します:

現在、コミュニケーションのパフォーマンスは焦点ではありません。このアーキテクチャに適したアプリケーションは本質的に計算されているため、通信を最適化することは重要ではないことがよくありますが、ニーズが生じるにつれて実装を最適化できます。

簡単な場合、上記の図の緑色のコンポーネントのみを提供し、データのすべてのカスタム処理はカスタムカーネルによって実行されます。ただし、C ++/OpenCLホストアプリケーションおよび/またはPython Webサーバーは、必要に応じて拡張できます。

このプロジェクトに先立ち、FPGAハードウェアアクセラレーションをWebおよびクラウドアプリケーションと統合することは、次のことを必要とする困難な事業でした。

Webサーバー、ホストアプリケーションコード、およびカーネルシェルロジックを提供して、WebアプリケーションとFPGAカーネル間のデータをストリーミングし、クラウドインスタンスの作成と構成を自動化することにより、第1 Claasは次のように削減します。

[CC by-sa 2.0、lumaxart、修正]

[CC by-sa 2.0、lumaxart、修正]

インフラストラクチャの開発オーバーヘッドは、数ヶ月から数時間まで減少します。

特にAmazon F1プラットフォームを見ると、F1は強力なXilinx FPGASおよびXilinx開発ツールを利用して、非常に説得力があります。しかし、プラットフォームはエッジを出血させており、利用するには重要な専門知識が必要です。このプラットフォームでの私たちの経験は、いくつかの理由でかなり苦痛な(そしてやや高価な)ものでした。

私たちはこの痛みを経験しなければなりませんでしたが、あなたがそうする必要がないように私たちは仕事を束ねました。

開発をさらに合理化し、コストを削減し、F1プラットフォームとXilinxツールスタックへの依存を回避するために、Verilator Open-Source RTLシミュレーターを使用してカーネルがRTLシミュレーションでエミュレートされるローカルマシンの開発をサポートします。 AWSおよびXilinxツールは、カーネルの最適化と展開にのみ必要です。追加のボーナスとして、Verilator Simulationは、Verilatorが高速であるため、Xilinxの「ハードウェアエミュレーションフロー」を使用してシミュレーションよりも大幅に速く実行されます(〜100倍!)。

問題をWebとRTL開発に削減することは、私たちにとってフィニッシュラインではありません。第1 Claasは、シリコン産業を再定義し、大衆にシリコンをもたらすためのより広範な努力の一部です。 RTLモデリングの複雑さを乗り越えることはその一部です。第1 Claasは、Redwood Edaと共同で、TL-Verilogの熱心な支持者によって推進されています。 TL-verilogは、よりシンプルで強力なモデリングコンストラクトを備えた非常に必要なデジタル回路設計方法のシフトを導入します。 1番目のClaasは、TL-verilogに結び付けられていません。 Verilog/SystemVerilogまたはverilogに変換できるハードウェア説明言語を使用できます。しかし、TL-verilog lnguage拡張機能は箱から出してサポートされています。それらを利用して、このイノベーションを前進させるのを支援することを強くお勧めします。 Redwood EDAは、Makerchip.comでTL-Verilog開発のための無料のオンラインIDEを提供しています。 IDEでトレーニング資料を見つけることができます。 Redwood EDAの創設者であるSteve Hooverのより完全なストーリーを読んでください。

商業的には、1番目のCLAASは、Streamputer、Inc。で使用され、ストリーミングデータの動的な分類を提供します。

1番目のClaasは、Fractalvalley.netのリアルタイムフラクタルをレンダリングします。

このリポジトリは一般的に機能しており、最初の開発の推進が終了しています。

この時点で、特にビルドのためのフレームワークによって提供されるインターフェイスに関して、すべてが変更される可能性があります。したがって、フレームワークの特定のバージョンに基づいて構築し、マスターから引っ張ってアップグレードすることを選択した場合はデバッグを行うことを期待する必要があります。

うーん...私たちはまだそれほど多くの考えを与えていません。いいことを言うだけで、私たちは幸せになります。

このリポジトリ内で引用されているすべての商標は、それぞれの所有者の財産です。