Conversor Buck Síncrono de 3 níveis com controle médio de modo de corrente com balanceamento de tensão do capacitor voador adaptativo

Vista superior

Este exemplo de código demonstra uma implementação de controle médio de modo de corrente de circuito fechado para DSPIC33CK. Ele foi desenvolvido especificamente para o design de referência de conversor de buck de 3 níveis EPC9148.

A placa inicia o conversor Buck automaticamente quando a energia é aplicada à placa, fornecendo uma tensão de saída regulada de 12 V na saída do conversor. O procedimento de inicialização é controlado e executado pela máquina de estado do controlador de energia e inclui um procedimento de inicialização configurável com atraso de potência, período de aumento e bom atraso antes de entrar no modo de regulamentação constante. Uma rotina adicional de manipulador de falhas monitora continuamente os dados do ADC recebido e os bits de status periférico e desligará a fonte de alimentação se a tensão de entrada estiver fora do intervalo definido ou se a tensão de saída for superior a +/- 0,5 V fora da regulação por mais de 10 milissegundos.

Microchip Technology Products em destaque:

Produtos de conversão de energia eficiente (EPC) em destaque:

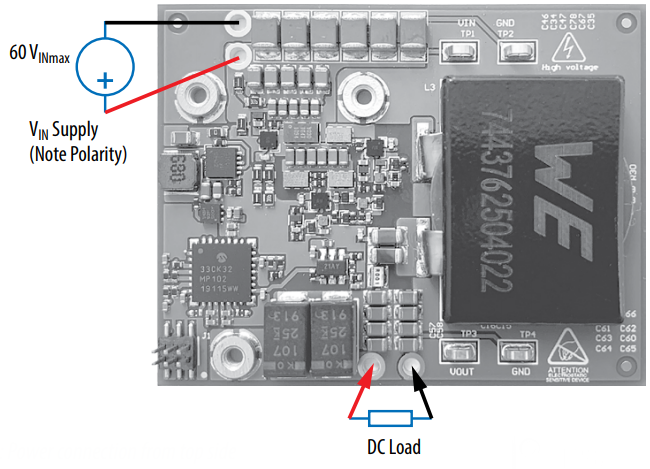

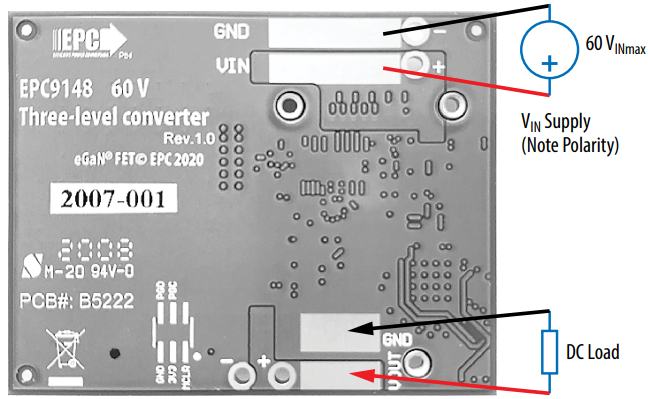

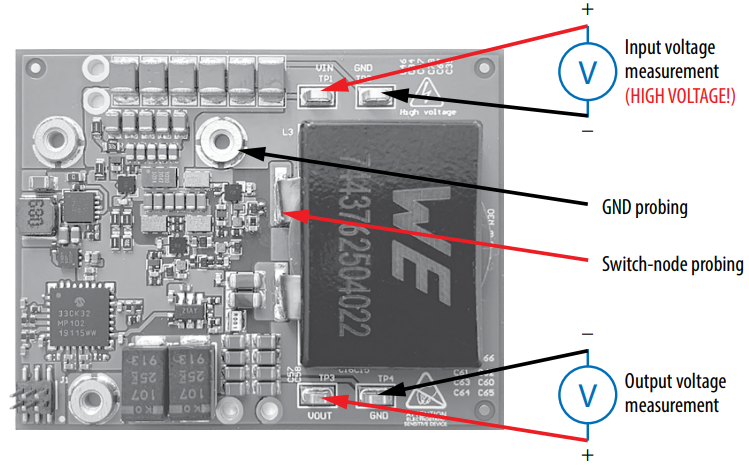

O módulo Conversor Síncrono de Buck de 3 níveis EPC9148 fornece todas as interfaces necessárias para programar e depurar o DSPIC33CK32MP102 DSC, bem como pontos de teste e conectores de tomada de banana para manuseio fácil e seguro do kit durante os testes de bancada. O EPC9148 QSG fornece instruções detalhadas do procedimento operacional.

A placa vem programada e pronta para ser usada quando descompactada. Nenhuma reprogramação do dispositivo de destino é necessária para operar a placa, a menos que os recursos ou configurações, como a tensão de saída nominal ou o tempo de inicialização, precisem ser modificados.

Caso os recursos baseados em firmware precisam ser alterados, o controlador Microchip DSPIC33CK pode ser reprogramado usando a porta de programação serial (ICSP) disponível na interface de programação RJ-11, bem como o cabeçalho de 5 pinos. É necessário um cabo de fita para conectar o kit de programação e o EPC9148. Essas interfaces suportam todos os programadores/depuradores de circuitos do Microchip, como MPLAB® ICD4, MPLAB® Real Ice ou MPLAB® Pickit4 e derivativos anteriores. Consulte EPC9148 Guia de início rápido para obter detalhes.

O conversor está iniciando automaticamente quando mais de 16,6 V DC são aplicados nos terminais de entrada do EPC9148. Leia o guia de início rápido EPC9148 para obter informações detalhadas sobre os requisitos para configuração e operação desse design de referência.

A máquina de estado passa pelas seguintes etapas em ordem cronológica:

a) inicialização

Nesta etapa, os parâmetros do loop de controle são redefinidos para seus padrões, as saídas do PWM são desligadas, mas o PWM ainda está em execução, acionando continuamente o ADC para manter a tensão de entrada e saída, bem como a temperatura da placa.

b) Redefinir este é o estado de 'capa de outono' a partir do qual o conversor BUCK será reiniciado assim que for iniciado com sucesso e for fechado devido a uma condição de falha (por exemplo, entrada sob/acima da tensão ou condição de temperatura)

c) em espera após a redefinição, a máquina de estado aguarda que todos os sinalizadores de falha sejam limpos e os bits de habilitação e vão para serem definidos.

d) Atraso de potência (POD) Uma vez que o conversor buck for limpo, a máquina de estado executará o procedimento de inicialização, começando com a energia no atraso. Este é apenas um atraso simples durante o qual o conversor permanecerá inativo, mas o manipulador de falhas observará os valores gerados pelo ADC para ocorrer condições de falha.

e) Lançar a rampa de tensão após o atraso de potência expirado, a tensão de entrada e saída será medida. Caso a saída do conversor seja pré-tendenciosa (tensão = diferente de zero), o controlador de energia será "pré-carregado" com um histórico de controle artificial e saída de PWM para aumentar suavemente a tensão de saída de seu nível mais recente.

f) Ramp-up de tensão agora o loop de feedback digital e o PWM estão ativados e o valor de referência do sistema de loop fechado é incrementado com todas as execuções da máquina de estado (intervalo de 100 µs). O loop de controle foi ajustado para operar com uma frequência transversal de> 10 kHz correspondendo à frequência máxima de perturbação permitida para manter o sistema de controle estável.

g) Bom atraso de energia após a tensão de referência ter sido aumentada para o nível nominal predefinido, a máquina de estado muda para o período de bom atraso de potência. Esse é outro atraso simples, onde o loop de controle está em estado estacionário, aguardando o expiração do período de atraso.

h) Online após o expedido de bom atraso, o conversor cai em operação nominal. Nesta condição, observa continuamente o valor de referência para alterações. Se qualquer outra parte do firmware alterar a referência do controlador, a máquina de estado sintonizará suavemente o novo nível, em vez de trocar-se com a referência.

i) Suspenda/erro Se o controlador de energia for desligado e redefinido por comandos externos (por exemplo, manipulador de falhas detectando uma condição de falha ou através da interação do usuário), a máquina de estado está mudando para o estado de suspensão, que desativa as saídas do PWM e a execução do loop de controle, limpa os históricos de controle e redefine a máquina de estado de volta para reastar

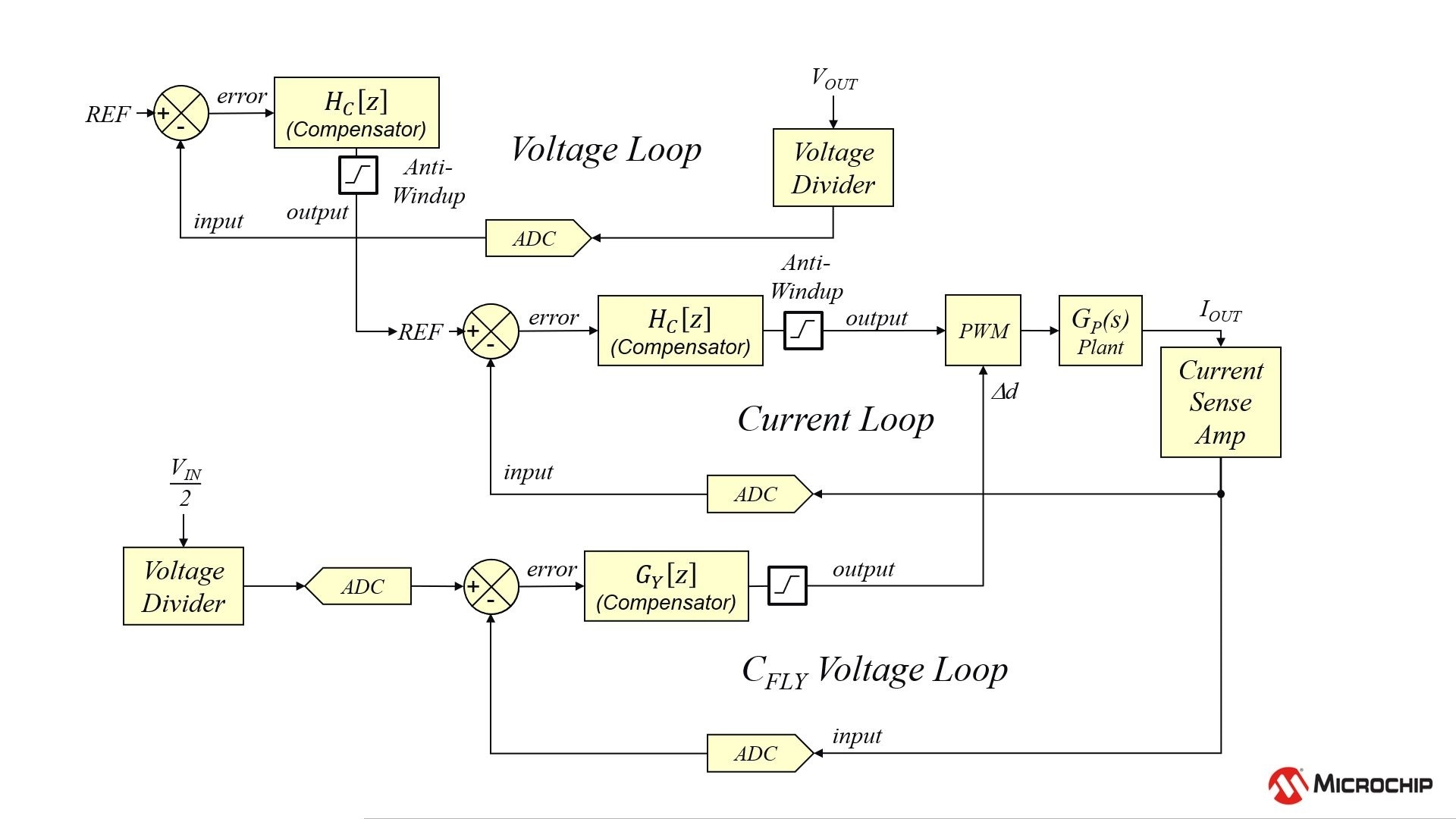

Este firmware usa dois controladores digitais do tipo II para fechar o loop de feedback no controle médio do modo atual. O controlador é composto por dois loops em cascata. O loop de feedback de tensão externa determina o erro de tensão de saída e calcula a referência necessária para o loop de feedback atual médio interno. O loop atual médio interno determina o desvio mais recente entre a nova referência e o sinal de feedback mais recente e ajusta o ciclo de trabalho da PWM para atender à demanda de energia e corrigir o erro de tensão de saída. A saída numérica de cada loop é verificada com os mínimos e os limiares máximos definidos e, quando necessário, fixados nesses limites definidos pelo usuário para proteger o hardware e impedir a saturação do loop.

Além da implementação básica do controle de modo atual médio, é introduzido um terceiro loop, monitorando e equilibrando a tensão do capacitor voador. Esse loop rastreia o pico de tensão e o vale do capacitor voador oscilante e sintoniza o tempo do PWM para compensar os desvios sobre tolerâncias, carga e temperatura de componentes. O filtro de compensação é baseado em um filtro passa-baixo simples, limitando a taxa de mudança do fator de compensação de erro de balanceamento para evitar oscilações internas durante respostas transitórias rápidas. O fator de correção é então incorporado na saída de loop atual em todos os ciclos de comutação.

Este sistema de controle pode ser ativado/desativado usando o bit de ativação na palavra de status da estrutura de dados do controlador CNPNZ_T.

O código -fonte do Loop de controle é configurado e gerado pelo software PowerSmart ™ - Digital Control Control Library Designer (DCLD).

Este software de design adicional está disponível para download nas páginas do Github:

Depois de instalado, a configuração do controlador pode ser modificada. A configuração mais recente pode ser aberta no MPLAB X® IDE clicando com o botão direito do mouse no respectivo arquivo de configuração de loop de controle 'xxx_loop.dcld' localizado na pasta de arquivos importantes do gerenciador de projetos. Cada loop de controle é configurado em seu arquivo de configuração individual chamado 'v_loop.dcld' para loops de tensão e 'i_loop.dcld' para loops atuais. Ao clicar com o botão direito do mouse, selecione 'Open in System' para abrir a configuração no PowerSmart ™ DCLD.

Consulte o Guia do Usuário do PowerSmart ™ DCLD, incluído no software e pode ser aberto no menu de ajuda do aplicativo.

Nenhuma interface de controle de usuário foi adicionada ao firmware. Qualquer alteração no firmware e a operação fundamental do design de referência, incluindo a reprogramação da tensão de saída nominal, pode ser feita editando os valores específicos de hardware no arquivo de cabeçalho da descrição do hardware 'EPC9148_R10_HWDESCR.H' localizado em 'Project Manager => Cabeçalho/Config'

As configurações do conversor neste arquivo são definidas como valores físicos como Volt, Ampere, Ohm, etc. Cada valor definido é convertido em números binários pelas chamadas macros, no momento da compilação. Assim, os usuários não precisam converter valores manualmente.

Para programar o conversor para fornecer uma tensão de saída nominal diferente do conjunto de 20 V DC por padrão, siga estas etapas:

A configuração para a tensão de saída nominal é definida usando essas define

#define BUCK_VOUT_NOMINAL (float)12.000 // Nominal output voltage

#define BUCK_VOUT_TOLERANCE_MAX (float)0.500 // Output voltage tolerance [+/-]

#define BUCK_VOUT_TOLERANCE_MIN (float)0.100 // Output voltage tolerance [+/-]

As configurações de tolerância acima incluem a resposta transitória em uma etapa máxima de carga. O valor para a tolerância máxima à tensão de saída 'buck_vout_tolerance_max' é observada pelo manipulador de falhas. Se a tensão de saída desviar do valor de tensão de referência mais recente por mais do que o intervalo especificado, o conversor será desligado e um erro de regulamentação será indicado. A fonte de alimentação se recuperará automaticamente assim que a condição de falha for limpa e o período de atraso de recuperação especificado por buck_regerr_recovery_delay, declarado no arquivo de cabeçalho do hardware EPC9148, expirou. A sensibilidade à viagem de falha pode ser ajustada alterando a declaração buck_regerr_trip_delay.

(Os números de linha fornecidos podem estar sujeitos a alterações)

Esses exemplos de código incluem um loop de controle proporcional alternativo, que é comumente usado durante as medições da resposta de frequência da usina. Quando o seguinte define é definido como true, o loop de controle principal comum é substituído pelo controlador proporcional.

app_power_control.c: #define PLANT_MEASUREMENT false

Os controladores proporcionais são, por padrão, instáveis e não são adequados para regular a saída de uma fonte de alimentação em condições operacionais normais. Durante uma medição da planta, é obrigatório que a tensão e a carga de entrada permaneçam estáveis e não mudem.

Para obter mais informações sobre como realizar uma medição da usina de energia, consulte a Seção 6.1 do Guia do Usuário do PowerSmart ™ DCLD.

(c) 2020, Microchip Technology Inc.