アダプティブフライングコンデンサ電圧バランスを備えた平均電流モード制御を備えた3レベルの同期バックコンバーター

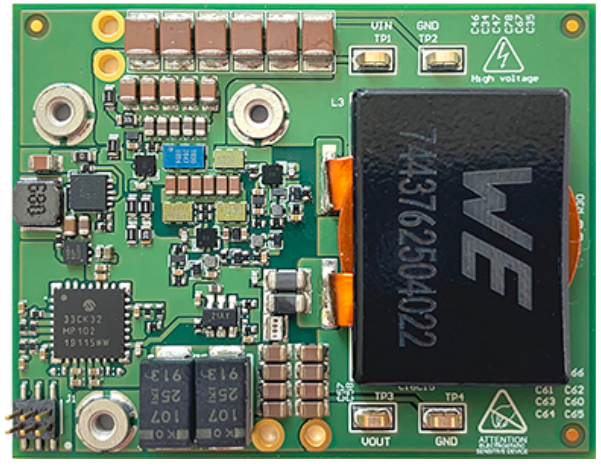

トップビュー

このコードの例は、DSPIC33CKのクローズドループ平均電流モード制御実装を示しています。 EPC9148 3レベルのバックコンバーターリファレンス設計用に特に開発されました。

ボードは、電源がボードに適用されると自動的にバックコンバーターを起動し、コンバーターの出力で12 Vの調整された出力電圧を提供します。起動手順は、Power Controller State Machineによって制御および実行され、パワーオンの遅延、ランプアップ期間、およびパワー遅延を備えた構成可能な起動手順が含まれてから、一定のレギュレーションモードにドロップします。追加の障害ハンドラールーチンは、入力電圧が定義された範囲外である場合、または出力電圧が10ミリ秒以上の規制から+/- 0.5 Vを超える場合、着信ADCデータと周辺ステータスのビットを継続的に監視し、電源をシャットダウンします。

注目のマイクロチップテクノロジー製品:

機能効率の高い電力変換(EPC)製品:

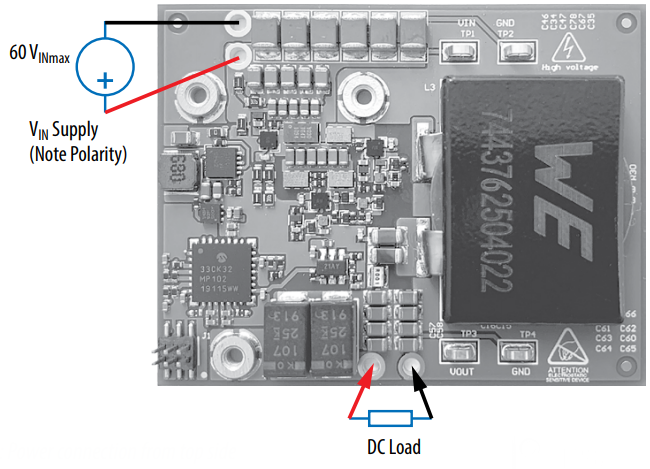

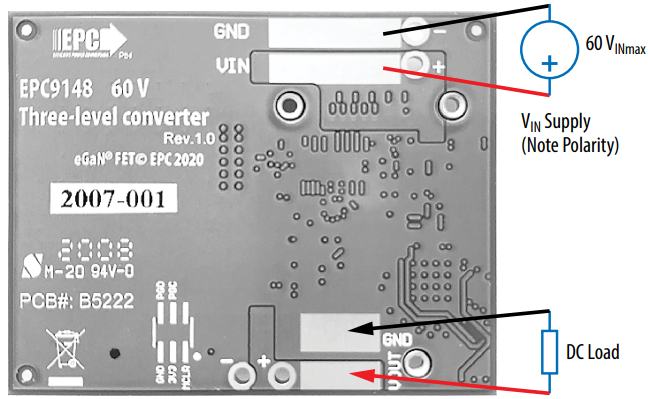

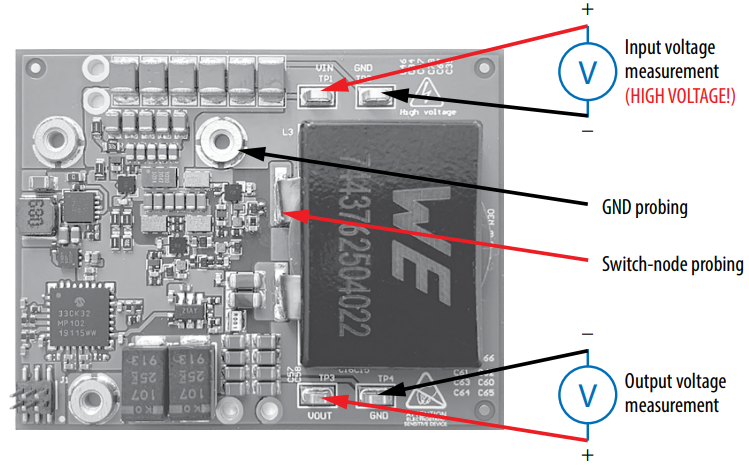

EPC9148 3レベルの同期バックコンバーターモジュールは、ベンチテスト中にキットを簡単かつ安全に処理するために、DSPIC33CK32MP102 DSCとバナナジャックコネクタをプログラムおよびデバッグするために必要なすべてのインターフェイスを提供します。 EPC9148 QSGは、詳細な操作手順の指示を提供します。

ボードはプログラムされており、開梱時に使用する準備ができています。公称出力電圧や起動タイミングなどの機能や設定を変更する必要がない限り、ボードを操作するためにターゲットデバイスの再プログラムは必要ありません。

ファームウェアベースの機能を変更する必要がある場合、Microchip DSPIC33CKコントローラーは、RJ-11プログラミングインターフェイスと5ピンヘッダーで利用可能なインサーキットシリアルプログラミングポート(ICSP)を使用して再プログラムできます。プログラミングキットとEPC9148を接続するには、リボンケーブルが必要です。これらのインターフェイスは、MPLAB®ICD4、MPLAB®リアルアイス、MPLAB®PickIT4、以前の誘導体など、Microchipのすべての回路プログラマー/デバッガーをサポートしています。詳細については、EPC9148クイックスタートガイドを参照してください。

EPC9148の入力端子に16.6 V DC以上が適用されると、コンバーターは自動的に起動します。 EPC9148クイックスタートガイドをお読みください。このリファレンスデザインのセットアップと操作の要件に関する詳細情報を取得してください。

状態マシンは、次の手順を年代順に通過します。

a)初期化

このステップでは、コントロールループパラメーターがデフォルトにリセットされ、PWM出力はオフになりますが、PWMはまだ実行されており、ADCを連続的にトリガーして、ボード温度だけでなくサンプリング入力と出力電圧をサンプリングし続けます。

b)リセットこれは、「フォールバック」状態であり、そこからバックコンバーターが正常に開始され、障害状態(電圧下/上の入力または温度条件)のためにシャットダウンされた後に再起動されます。

c)スタンバイリセット後、ステートマシンはすべての障害フラグがクリアされるのを待ち、enableとgoビットを設定します。

d)電力オン遅延(POD)バックコンバーターがクリアされると、ステートマシンは遅延の電源を掲載してからスタートアップ手順を実行します。これは単純な遅延であり、その間にコンバーターが非アクティブなままですが、障害ハンドラーは発生する障害条件のためにADCによって生成された値を観察します。

e)電源オンの遅延が期限切れになった後、電圧ランプを起動し、入力電圧と出力電圧が測定されます。コンバーター出力が事前にバイアスされている場合(電圧=非ゼロ)、パワーコントローラーは人工制御履歴とPWM出力を備えた「事前充電」され、最新のレベルから出力電圧を柔らかく上昇させます。

f)電圧ランプアップこれで、デジタルフィードバックループとPWMが有効になり、状態マシンのすべての実行(100 µSEC間隔)で閉ループシステムの参照値が増加します。制御ループは、コントロールシステムを安定させるために許容される最大摂動周波数に一致する10 kHzを超えるクロスオーバー周波数で動作するように調整されています。

g)参照電圧が事前に定義された公称レベルに増加した後、パワーマシンは電源良好な遅延期間に切り替えます。これは、制御ループが定常状態にある別の単純な遅延であり、遅延期間が期限切れになるのを待っています。

h)オンラインでは、パワーの良い遅延が失効した後、コンバーターは公称操作に低下します。この条件では、変更の基準値を継続的に観察します。ファームウェアの他の部分がコントローラーリファレンスを変更した場合、ステートマシンは参照をハードスイッチするのではなく、新しいレベルにそっとチューニングします。

i)パワーコントローラーが外部コマンド(例:障害条件またはユーザー相互作用による障害ハンドラー)によってシャットダウンおよびリセットされている場合、状態マシンはサスペンド状態に切り替えています。

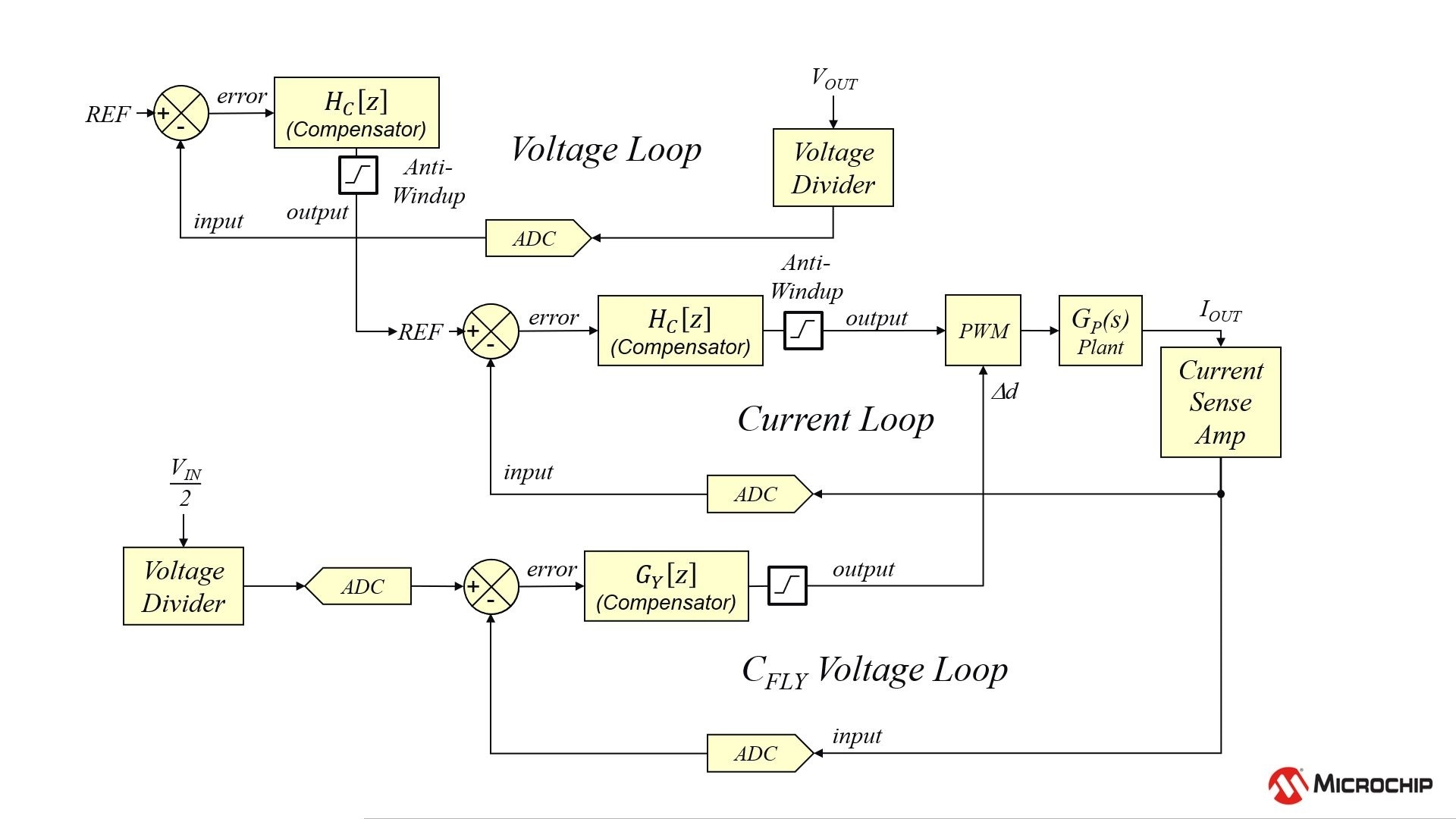

このファームウェアは、2つのデジタルタイプIIコントローラーを使用して、平均的な電流モードコントロールでフィードバックループを閉じます。コントローラーは、2つのカスケードループで構成されています。外側の電圧フィードバックループは、出力電圧誤差を決定し、内部平均電流フィードバックループに必要な基準を計算します。内側の平均電流ループは、新しい参照と最新のフィードバック信号との間の最新の偏差を決定し、PWMデューティサイクルを調整して電力需要を満たし、出力電圧誤差を修正します。各ループの数値出力は、定義された最小値と最大閾値に対してチェックされ、必要に応じてこれらのユーザー定義のしきい値に固定して、ハードウェアを保護し、ループ飽和を防止します。

基本的な平均電流モード制御実装に加えて、3番目のループが導入され、飛行コンデンサ電圧の監視とバランスが取れます。このループは、振動する飛行コンデンサ電圧の電圧ピークと谷を追跡し、PWMタイミングを調整して、成分の耐性、荷重、温度に対する偏差を補正します。補償フィルターは、速い過渡応答中の内部振動を防ぐために、バランスエラー補正係数の変化率を制限する単純なローパスフィルターに基づいています。次に、すべてのスイッチングサイクルで補正係数が現在のループ出力に組み込まれます。

この制御システムは、CNPNZ_Tコントローラーデータ構造のステータスワードで有効なビットを使用して、オン/オフにすることができます。

制御ループソースコードは、PowerSmart™ - デジタルコントロールライブラリデザイナー(DCLD)ソフトウェアによって構成および生成されます。

この追加のデザインソフトウェアは、GitHubページでダウンロードできます。

インストールすると、コントローラー構成を変更できます。最新の構成は、プロジェクトマネージャーの重要なファイルフォルダーにあるそれぞれのコントロールループ構成ファイル「xxx_loop.dcld」を右クリックすることにより、mplabx®アイデ内から開くことができます。各コントロールループは、電圧ループ用の「v_loop.dcld」という名前の個々の構成ファイルと、電流ループ用の「i_loop.dcld」で構成されています。右クリックしたら、[システム内で開く]を選択して、PowerSmart™DCLDで構成を開きます。

ソフトウェアに含まれ、アプリケーションのヘルプメニューから開くことができるPowerSmart™DCLDのユーザーガイドを参照してください。

ファームウェアにユーザー制御インターフェイスが追加されていません。公称出力電圧の再プログラミングを含む、ファームウェアの変更と参照設計の基本的な操作は、ハードウェア説明ヘッダーファイルのハードウェア固有の値を編集することで実行できます。

このファイルのコンバーター設定は、ボルト、アンペア、オームなどの物理値として定義されます。各定義値は、コンパイル時にいわゆるマクロによってバイナリ数に変換されます。したがって、ユーザーは値を手動で変換する必要はありません。

コンバーターをプログラムして、デフォルトで設定された20 V DCとは異なる公称出力電圧を提供するには、次の手順に従ってください。

公称出力電圧の設定は、これらの定義を使用して設定されます

#define BUCK_VOUT_NOMINAL (float)12.000 // Nominal output voltage

#define BUCK_VOUT_TOLERANCE_MAX (float)0.500 // Output voltage tolerance [+/-]

#define BUCK_VOUT_TOLERANCE_MIN (float)0.100 // Output voltage tolerance [+/-]

上記の許容範囲には、最大負荷ステップでの過渡応答が含まれます。最大出力電圧耐性「buck_vout_tolerance_max」の値は、障害ハンドラーによって観察されます。出力電圧の読み取り値が最新の基準電圧値から指定された範囲を超えて迂回した場合、コンバーターがシャットダウンされ、レギュレーションエラーが示されます。電源は障害条件がクリアされるとすぐに自動的に回復し、EPC9148ハードウェア説明ヘッダーファイルで宣言されたbuck_regerr_recovery_delayによって指定された回復遅延期間が期限切れになります。障害旅行の感度は、buck_regerr_trip_delay宣言を変更することで調整できます。

(与えられた行数は変更される場合があります)

このコードの例には、発電所の周波数応答の測定中に一般的に使用される代替の比例制御ループが含まれています。次の定義がtrueに設定されると、共通のメインコントロールループは比例コントローラーに置き換えられます。

app_power_control.c: #define PLANT_MEASUREMENT false

比例コントローラーはデフォルトでは不安定であり、通常の動作条件下で電源の出力を調整するのに適していません。植物の測定中、入力電圧と荷重は安定したままで変化しないことが必須です。

発電所の測定方法の詳細については、PowerSmart™DCLDユーザーガイドのセクション6.1を参照してください。

(c)2020、Microchip Technology Inc.