적응 형 플라잉 커패시터 전압 밸런싱을 갖는 평균 전류 모드 제어 기능이있는 3 레벨 동기 벅 컨버터

최고보기

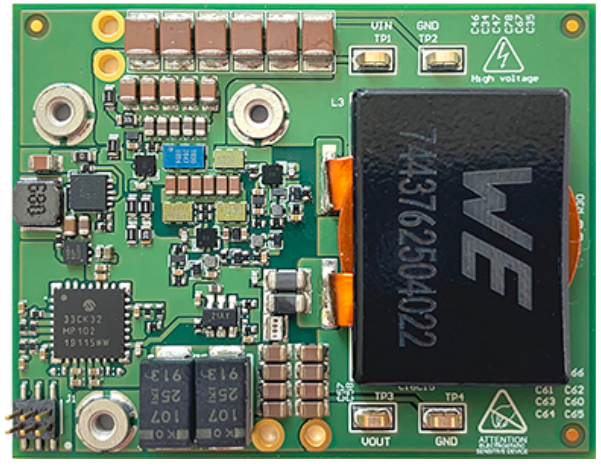

이 코드 예제는 DSPIC33CK의 폐쇄 루프 평균 전류 모드 제어 구현을 보여줍니다. EPC9148 3 레벨 벅 컨버터 참조 설계를 위해 구체적으로 개발되었습니다.

보드는 전원이 보드에 적용될 때 벅 컨버터를 자동으로 시동하여 변환기의 출력에서 12V의 조절 된 출력 전압을 제공합니다. 시작 절차는 Power Controller State Machine에 의해 제어되고 실행되며 전원 온도 지연, 램프 증가 기간 및 지속적인 규정 모드로 떨어지기 전에 전력 우수 지연이 포함 된 구성 가능한 시작 절차가 포함되어 있습니다. 추가 결함 핸들러 루틴은 들어오는 ADC 데이터 및 주변 상태 비트를 연속적으로 모니터링하고 입력 전압이 정의 된 범위를 벗어나거나 출력 전압이 10 밀리 초 이상에 대해 +/- 0.5V 이상인 경우 전원 공급 장치를 종료합니다.

주요 마이크로 칩 기술 제품 :

주요 효율적인 전력 변환 (EPC) 제품 :

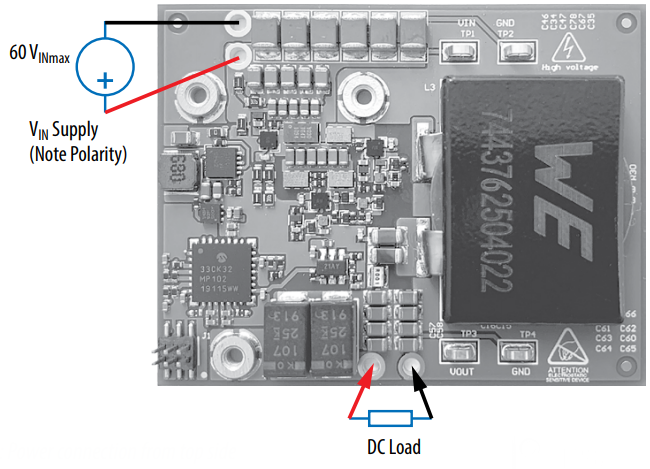

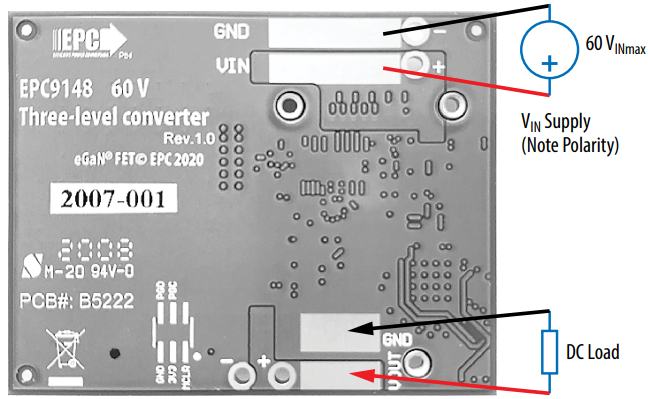

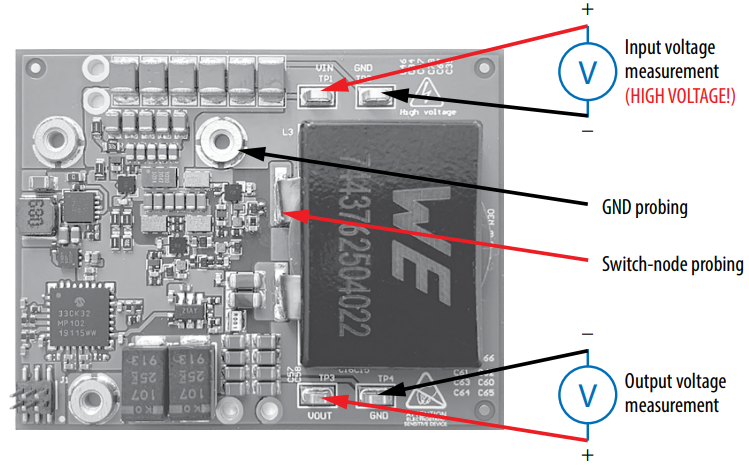

EPC9148 3 레벨 동기 벅 컨버터 모듈은 벤치 테스트 중에 키트를 쉽고 안전하게 처리 할 수 있도록 DSPIC33CK32MP102 DSC뿐만 아니라 DSPIC33CK32MP102 DSC를 프로그래밍하고 디버깅하는 데 필요한 모든 인터페이스를 제공합니다. EPC9148 QSG는 자세한 작동 절차 지침을 제공합니다.

보드는 프로그램이 풀리고 포장을 풀 때 사용할 준비가되어 있습니다. 공칭 출력 전압 또는 스타트 업 타이밍과 같은 기능이나 설정을 수정하지 않으면 보드를 작동하려면 대상 장치의 재 프로그래밍이 필요하지 않습니다.

펌웨어 기반 기능을 변경 해야하는 경우 RJ-11 프로그래밍 인터페이스와 5 핀 헤더에서 사용 가능한 ICSP (Incircuit Serial Programming Port)를 사용하여 Microchip DSPIC33CK 컨트롤러를 다시 프로그래밍 할 수 있습니다. 프로그래밍 키트와 EPC9148을 연결하려면 리본 케이블이 필요합니다. 이 인터페이스는 MPLAB® ICD4, MPLAB® Real Ice 또는 MPLAB® Pickit4 및 이전 파생 상품과 같은 모든 Microchip의 커미션 프로그래머/디버거를 지원합니다. 자세한 내용은 EPC9148 빠른 시작 안내서를 참조하십시오.

EPC9148의 입력 단자에 16.6 V DC 이상이 적용될 때 변환기가 자동으로 시작됩니다. 이 참조 설계의 설정 및 작동 요구 사항에 대한 자세한 정보를 얻으려면 EPC9148 빠른 시작 가이드를 읽으십시오.

주 머신은 다음 단계를 시간 순서대로 수행합니다.

a) 초기화

이 단계에서 제어 루프 매개 변수는 기본값으로 재설정되며 PWM 출력이 꺼져 있지만 PWM이 여전히 실행 중이며 ADC를 지속적으로 트리거하여 샘플링 입력 및 출력 전압 및 보드 온도를 유지합니다.

b) 재설정 벅 컨버터가 성공적으로 시작되면 벅 컨버터가 다시 시작되고 결함 조건으로 인해 종료 된 '낙하'상태입니다 (예 : 전압 미만/온도 조건).

c) 대기 재설정 후, 상태 기계는 모든 결함 플래그가 지워지고 활성화 및 GO 비트를 설정할 때까지 기다립니다.

d) 전원 온 지연 (POD) 벅 컨버터가 지워지면 State Machine은 전원 on 지연으로 시작하여 시작 절차를 실행합니다. 이는 변환기가 비활성 상태로 유지되는 간단한 지연이지만 결함 핸들러는 발생하는 결함 조건에 대해 ADC에 의해 생성 된 값을 관찰합니다.

e) 전원 온도 지연이 만료 된 후 발사 전압 램프, 입력 및 출력 전압이 측정됩니다. 컨버터 출력이 사전 바이어스 (전압 = 0이 아닌) 인 경우, 전력 컨트롤러는 인공 제어 기록을 사용하여 '사전 차지'되고 PWM 출력이 가장 최근 수준에서 출력 전압을 부드럽게 증가시킵니다.

f) 전압 램프 업 이제 디지털 피드백 루프 및 PWM이 활성화되고 폐쇄 루프 시스템 참조 값은 상태 기계의 모든 실행 (100 µSEC 간격)마다 증가합니다. 제어 루프는 제어 시스템을 안정적으로 유지하도록 허용되는 최대 섭동 주파수와 일치하는> 10 kHz의 크로스 오버 주파수로 작동하도록 조정되었습니다.

g) 전력 양호 지연 기준 전압이 사전 정의 된 공칭 수준으로 증가한 후, 상태 기계는 전력 양호 지연 기간으로 전환됩니다. 이것은 제어 루프가 지연 기간이 만료되기를 기다리는 정상 상태에있는 또 다른 간단한 지연입니다.

h) 온라인 전원 양호 지연이 만료 된 후 컨버터는 공칭 작업으로 떨어집니다. 이 조건에서는 변경에 대한 참조 값을 지속적으로 관찰합니다. 펌웨어의 다른 부분이 컨트롤러 참조를 변경하면 상태 머신은 참조를 하드 스위치하는 대신 새 레벨을 부드럽게 조정합니다.

i) 정지/오류 전원 컨트롤러가 외부 명령 (예 : 결함 핸들러가 결함 조건을 감지하거나 사용자 상호 작용을 통해 결함 핸들러)에 의해 재설정 된 경우, 상태 머신은 PWM 출력 및 제어 루프 실행을 비활성화하는 상태로 전환하고, 제어 역사를 지우고 재설정하도록 지정합니다.

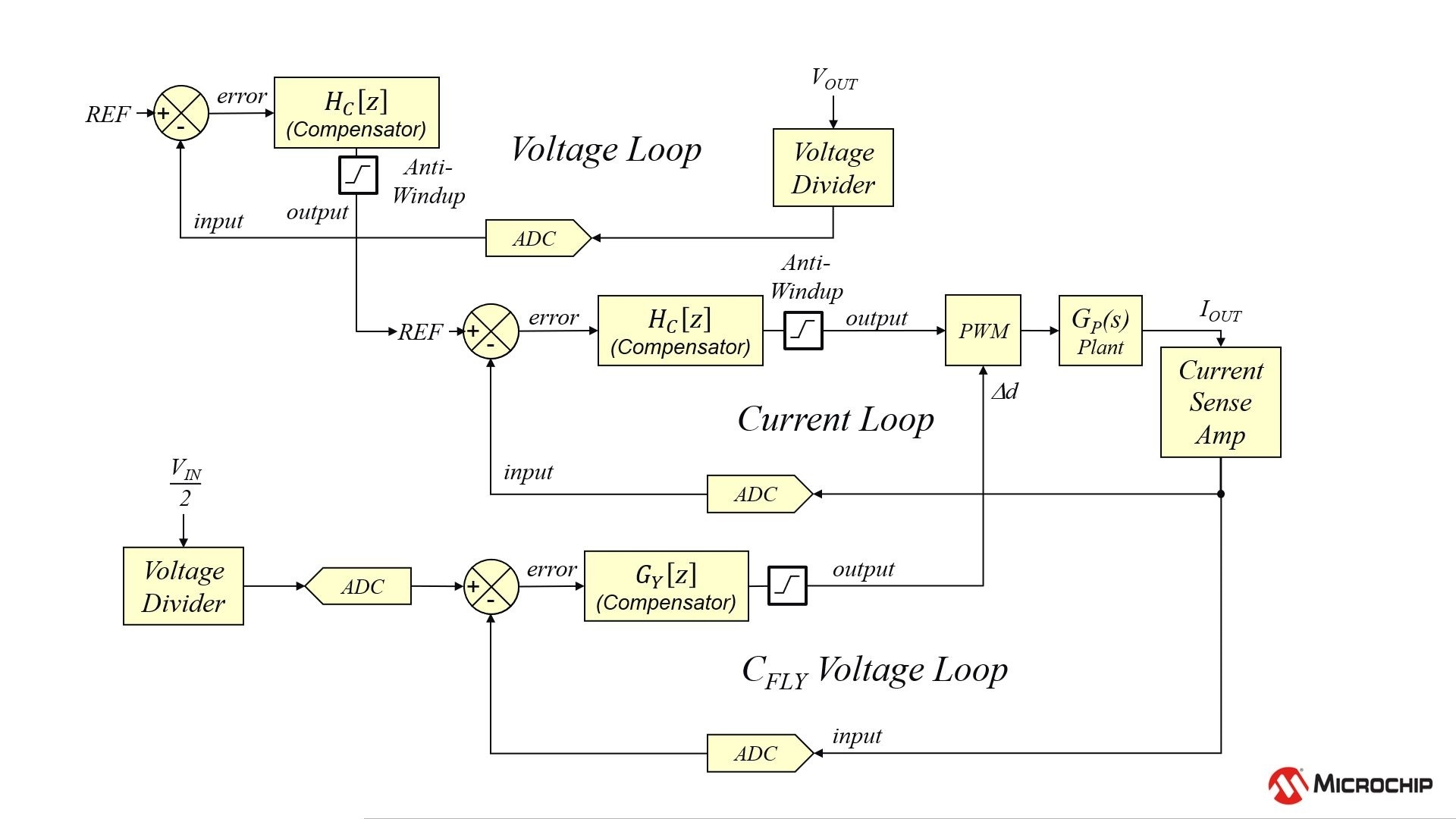

이 펌웨어는 두 개의 디지털 타입 II 컨트롤러를 사용하여 평균 전류 모드 제어에서 피드백 루프를 닫습니다. 컨트롤러는 두 개의 계단식 루프로 구성됩니다. 외부 전압 피드백 루프는 출력 전압 오차를 결정하고 내부 평균 전류 피드백 루프에 필요한 참조를 계산합니다. 내부 평균 전류 루프는 새로운 참조와 가장 최근의 피드백 신호 사이의 가장 최근 편차를 결정하고 PWM 듀티 사이클을 조정하여 전력 수요를 충족시키고 출력 전압 오차를 수정합니다. 각 루프의 숫자 출력은 정의 된 최소 및 최대 임계 값에 대해 확인되며 필요한 경우 하드웨어를 보호하고 루프 포화를 방지하기 위해 이러한 사용자 정의 임계 값에 클램핑됩니다.

기본 평균 전류 모드 제어 구현 외에도 플라잉 커패시터 전압을 모니터링 및 균형 잡는 세 번째 루프가 도입되어 있습니다. 이 루프는 진동 플라잉 커패시터 전압의 전압 피크와 밸리를 추적하고 PWM 타이밍을 조정하여 구성 요소 공차, 하중 및 온도에 대한 편차를 보상합니다. 보상 필터는 빠른 과도 응답 동안 내부 진동을 방지하기 위해 밸런싱 오류 보상 계수의 변경 속도를 제한하는 간단한 저역 통과 필터를 기반으로합니다. 그런 다음 보정 계수는 모든 스위칭 사이클에서 전류 루프 출력에 통합됩니다.

이 제어 시스템은 CNPNZ_T 컨트롤러 데이터 구조의 상태 워드에서 활성화 비트를 사용하여 켜지거나 꺼질 수 있습니다.

Control Loop 소스 코드는 Powersmart ™ - DIGING CONTROL LIBRARY DESIGNER (DCLD) 소프트웨어에 의해 구성되고 생성됩니다.

이 추가 디자인 소프트웨어는 GitHub 페이지에서 다운로드 할 수 있습니다.

일단 설치되면 컨트롤러 구성을 수정할 수 있습니다. 가장 최근의 구성은 프로젝트 관리자의 중요한 파일 폴더에있는 각 Control Loop 구성 파일 'XXX_LOOP.DCLD'를 마우스 오른쪽 버튼으로 클릭하여 MPLAB X® IDE 내에서 열 수 있습니다. 각 컨트롤 루프는 전압 루프의 경우 'v_loop.dcld'라는 개별 구성 파일 및 전류 루프의 경우 'i_loop.dcld'로 구성됩니다. 마우스 오른쪽 버튼을 클릭하면 '시스템에서 열기'를 선택하여 PowerSmart ™ DCld에서 구성을 엽니 다.

소프트웨어에 포함되어 있으며 응용 프로그램의 도움말 메뉴에서 열 수있는 Powersmart ™ DCLD의 사용자 안내서를 참조하십시오.

펌웨어에 사용자 제어 인터페이스가 추가되지 않았습니다. 하드웨어 설명 헤더 파일 'EPC9148_R10_HWDESCR.H'에서 하드웨어 별 값을 편집하여 공칭 출력 전압의 재 프로그래밍을 포함하여 펌웨어 변경 및 기본 설계의 기본 작동을 수행 할 수 있습니다.

이 파일의 변환기 설정은 Volt, Ampere, Ohm 등과 같은 물리적 값으로 정의됩니다. 각 정의 된 값은 컴파일 시간에 소위 매크로에 의해 이진 번호로 변환됩니다. 따라서 사용자는 수동으로 값을 변환 할 필요가 없습니다.

기본적으로 설정된 20 V DC와 다른 공칭 출력 전압을 제공하도록 변환기를 프로그래밍하려면 다음 단계를 따르십시오.

공칭 출력 전압의 설정은 이러한 정의를 사용하여 설정됩니다.

#define BUCK_VOUT_NOMINAL (float)12.000 // Nominal output voltage

#define BUCK_VOUT_TOLERANCE_MAX (float)0.500 // Output voltage tolerance [+/-]

#define BUCK_VOUT_TOLERANCE_MIN (float)0.100 // Output voltage tolerance [+/-]

위의 공차 설정에는 최대 하중 단계에서의 과도 응답이 포함됩니다. 최대 출력 전압 공차 'Buck_vout_tolerance_max'의 값은 고장 처리기에서 관찰됩니다. 출력 전압 판독 값은 주어진 범위보다 가장 최근의 참조 전압 값으로 인한 경우 변환기가 종료되고 규정 오류가 표시됩니다. EPC9148 하드웨어 설명 헤더 파일에 선언 된 Buck_Regerr_Recovery_delay가 지정된 복구 지연 기간이 만료되면 전원 공급 장치가 결함 조건이 지워지 자마자 자동으로 복구됩니다. Buck_Regerr_trip_delay 선언을 변경하여 오류 트립 감도를 조정할 수 있습니다.

(주어진 줄 번호는 변경 될 수 있습니다)

이 코드 예제에는 발전소의 주파수 응답을 측정하는 동안 일반적으로 사용되는 대안의 비례 제어 루프가 포함됩니다. 다음 정의가 true로 설정되면 공통 기본 제어 루프는 비례 컨트롤러로 대체됩니다.

app_power_control.c: #define PLANT_MEASUREMENT false

비례 컨트롤러는 기본적으로 불안정하며 정상적인 작동 조건에서 전원 공급 장치의 출력을 조절하는 데 적합하지 않습니다. 플랜트 측정 중에 입력 전압과 하중이 안정적으로 유지되고 변화하지 않아야합니다.

발전소 측정을 수행하는 방법에 대한 자세한 내용은 Powersmart ™ DCLD 사용자 안내서의 6.1 절을 참조하십시오.

(c) 2020, Microchip Technology Inc.