Convertidor bucónico bucaloso/impulso bidireccional de 2 fases

|  | |||

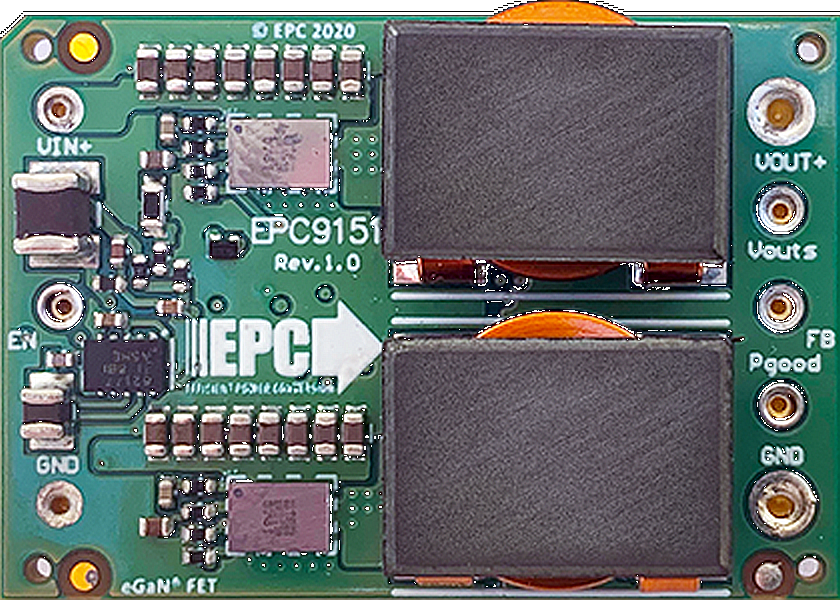

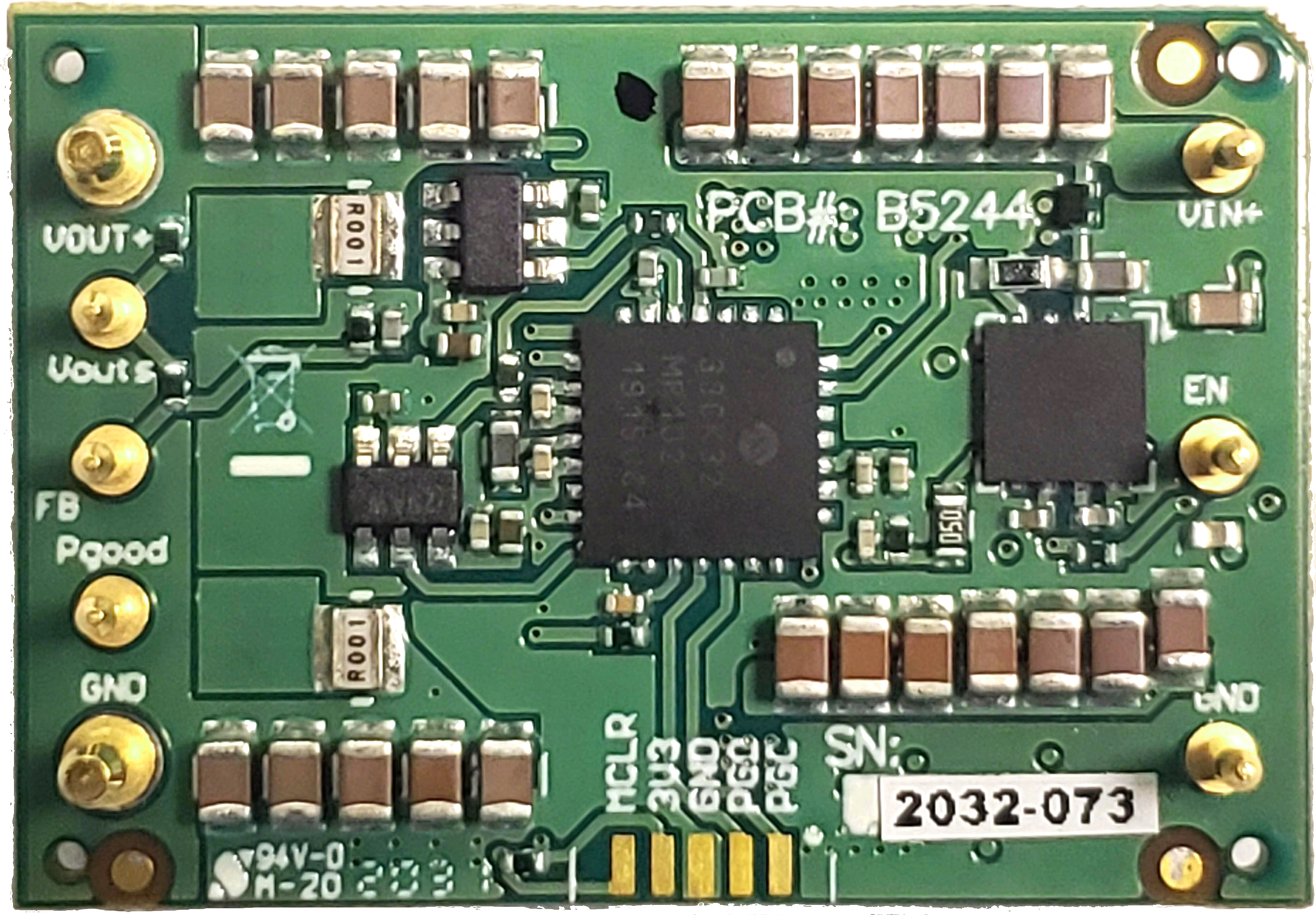

| Vista superior | Vista inferior |

Este ejemplo de código demuestra una implementación de control de modo de modo de corriente promedio de circuito cerrado para DSPIC33CK. Se ha desarrollado específicamente para el convertidor de ladrillo EPC9151 Rev1.0 1/16.

La placa admite una operación reducida y subiendo. En el modo de paso hacia abajo, la dirección de conversión va de 48 V a 12 V, mientras que en el modo de paso arriba, la dirección de conversión de 12 V a 48 V. Si no se indica, el lado de 48 V se llama 'Entrada' y el lado de 12 V se llama 'Salida' en este documento.

La placa inicia el convertidor de energía automáticamente cuando la energía se aplica a la placa, proporcionando un voltaje de salida regulado. El procedimiento de inicio es controlado y ejecutado por la máquina de estado del controlador de energía e incluye un procedimiento de inicio configurable con retraso de encendido, período de aumento y buena retraso antes de caer en el modo de regulación constante. Una rutina adicional de controlador de fallas monitorea continuamente los datos de ADC entrantes y los bits de estado periférico y cierra la fuente de alimentación si el voltaje de entrada está fuera del rango definido (UVLO/OVLO) o si el voltaje de salida es más de 0.5 V fuera de regulación por más de 10 milisegundos.

Se utiliza un controlador de modo promedio de Mutli-Loop tipo II (2P2Z) para equilibrar las corrientes de fase en ambas fases de este convertidor entrelazado. (ver detalles a continuación)

Productos de tecnología Microchip destacados:

Productos de conversión de potencia eficiente (EPC) destacados:

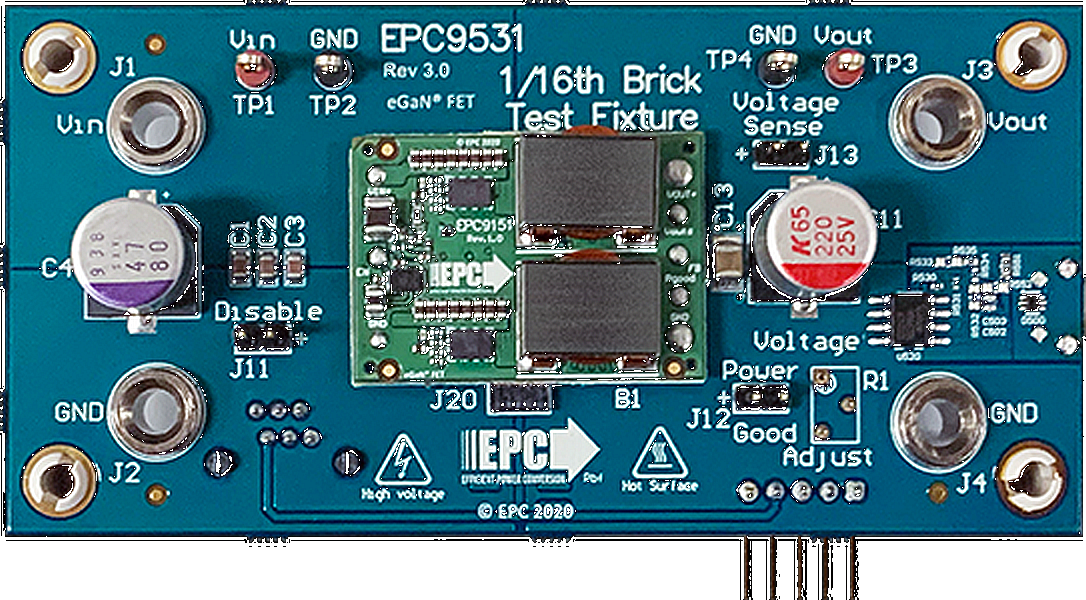

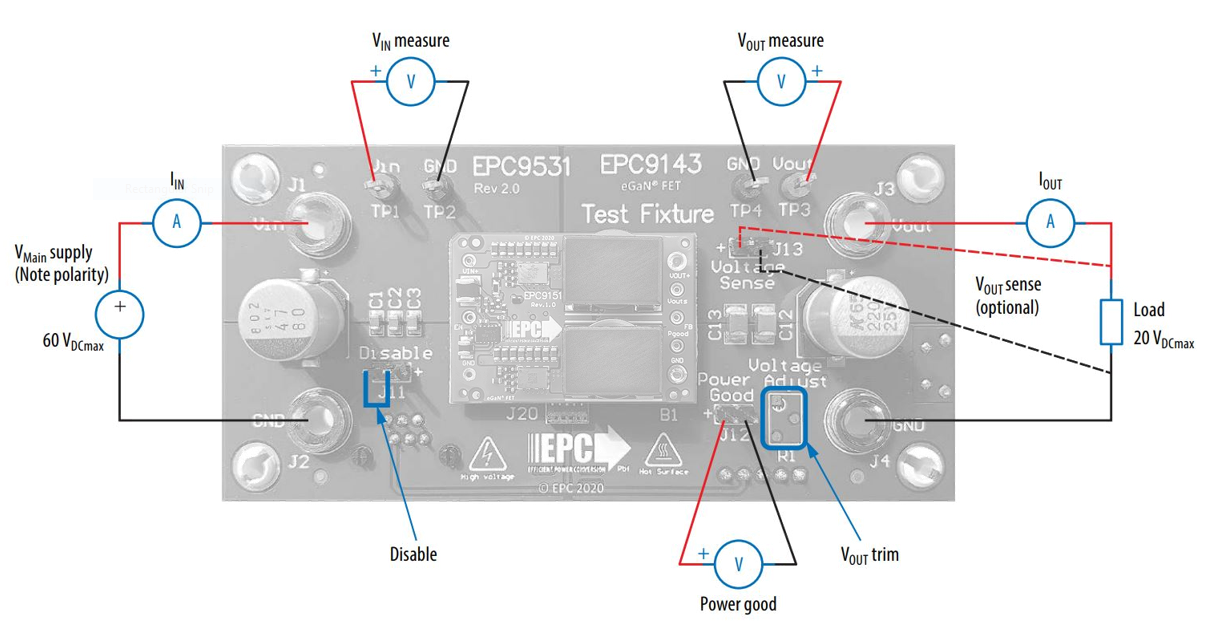

El módulo de alimentación de ladrillo EPC9151 1/16 se prueba mejor cuando se conecta al accesorio de prueba EPC9531. Este accesorio de prueba también proporciona todas las interfaces requeridas para programar y depurar el DSC DSPIC33CK32MP102, así como los puntos de prueba y los conectores de banana para un manejo fácil y seguro del kit durante las pruebas de banco. El EPC9531 QSG proporciona instrucciones detalladas del procedimiento operativo.

El tablero viene programado y listo para ser usado cuando se desempaqueta. No se requiere reprogramación del dispositivo de destino para operar la placa a menos que las características o configuraciones, como el voltaje de salida nominal o el tiempo de arranque, deben modificarse.

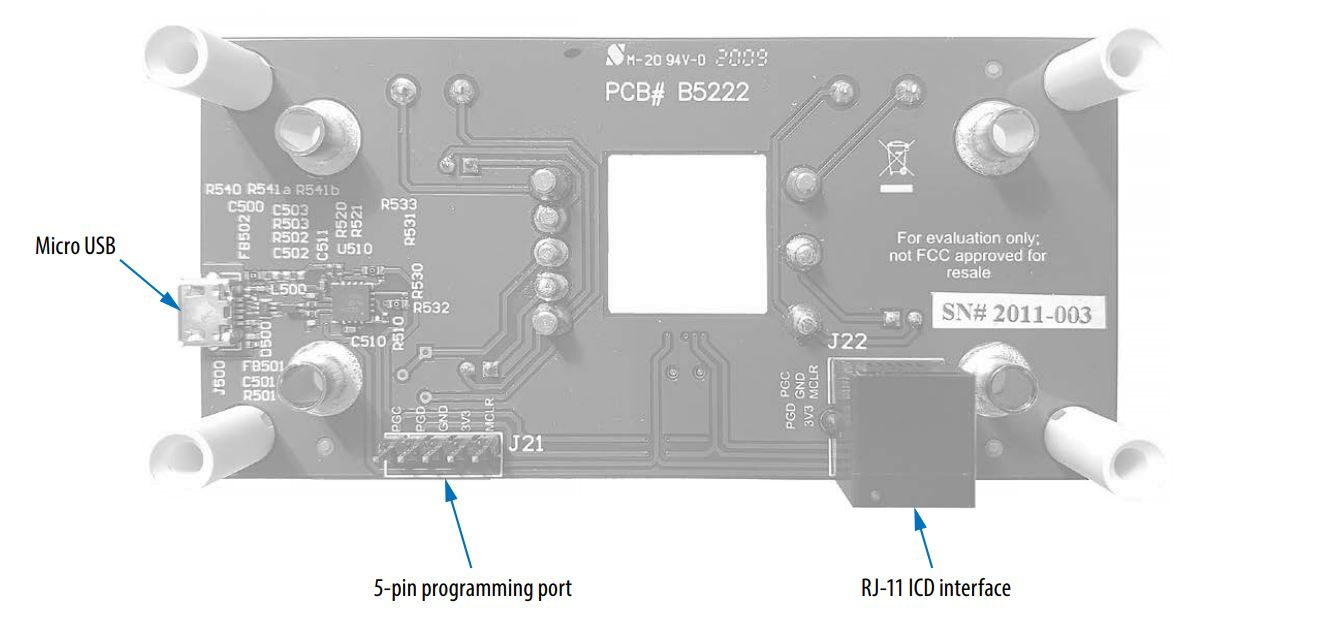

En caso de que las características basadas en el firmware deben cambiarse, el controlador Microchip DSPIC33CK se puede volver a programar utilizando el puerto de programación serial en circuito (ICSP) disponible en la interfaz de programación RJ-11, así como el encabezado de 5 pines proporcionado por la fijación de la prueba EPC9531. Estas interfaces admiten todos los programadores/depuradores de circuito de Microchip, como MPLAB® ICD4, MPLAB® Real Ice o MPLAB® Pickit4 y derivadas anteriores. Consulte la guía de inicio rápido EPC9531 para obtener más detalles.

El convertidor se inicia automáticamente cuando se aplican más de 8.5 V CC en los terminales de salida resp. 18 V a través de los terminales de entrada del accesorio de prueba EPC9531. No se recomienda operar el diseño de referencia EPC9151 sin una capacitancia de desacoplamiento adecuada en entrada o salida. El accesorio de prueba EPC9531 proporciona el mejor entorno de prueba para el convertidor. Lea la Guía de inicio rápido EPC9531 para obtener información detallada sobre los requisitos para la configuración y la operación de este diseño de referencia.

La máquina de estado pasa por los siguientes pasos en orden cronológico:

a) inicialización

En este paso, los parámetros del bucle de control se restablecen a sus valores predeterminados, las salidas PWM se apagan pero el PWM todavía se está ejecutando, activando continuamente el ADC para mantener la entrada de muestreo y el voltaje de salida, así como la temperatura de la placa.

b) Restablecer este es el estado de 'caída' del que se reiniciará el convertidor de dinero una vez que se haya iniciado con éxito y se haya cerrado debido a una condición de falla (por ejemplo, entrada bajo/sobre voltaje o sobre la condición de temperatura)

c) En espera después del reinicio, la máquina de estado espera a que se eliminen todas las banderas de falla y se establecen los bits de habilitación y Go.

d) Retraso de encendido (POD) Una vez que se haya borrado el convertidor Buck, la máquina de estado ejecutará el procedimiento de inicio que comienza con el retraso de encendido. Este es solo un retraso simple durante el cual el convertidor permanecerá inactivo, pero el controlador de fallas observará los valores generados por el ADC para las condiciones de falla que ocurren.

e) Rampa de voltaje de lanzamiento después de que el retraso de encendido haya expirado, se medirá el voltaje de entrada y salida. En caso de que la salida del convertidor esté pre-sesgo (voltaje = no cero), el controlador de potencia se "precargó" con un historial de control artificial y una salida PWM para aumentar suavemente el voltaje de salida desde su nivel más reciente.

f) Agrupación de voltaje Ahora el circuito de retroalimentación digital y el PWM están habilitados y el valor de referencia del sistema de circuito cerrado se incrementa con cada ejecución de la máquina de estado (intervalo de 100 µS). El bucle de control se ha ajustado para funcionar con una frecuencia cruzada de> 10 kHz que coincide con la frecuencia de perturbación máxima permitida para mantener el sistema de control estable.

g) Buena retraso de alimentación Después de que el voltaje de referencia se ha aumentado al nivel nominal predefinido, la máquina de estado cambia al período de retraso de buena potencia. Este es otro retraso simple donde el bucle de control está en estado estable esperando que expire el período de retraso.

h) En línea después de que el buen retraso ha expirado, el convertidor cae en operación nominal. En esta condición, observa continuamente el valor de referencia para los cambios. Si cualquier otra parte del firmware cambia la referencia del controlador, la máquina de estado sintonizará suavemente el nuevo nivel en lugar de cambiar la referencia.

i) suspender/error Si el controlador de alimentación se apaga y restablece mediante comandos externos (por ejemplo, el controlador de falla que detecta una condición de falla o mediante interacción del usuario), la máquina de estado está cambiando al estado de suspensión, que deshabilita las salidas PWM y la ejecución del bucle de control, borra las historias de control y restablece la máquina de estado para reiniciar

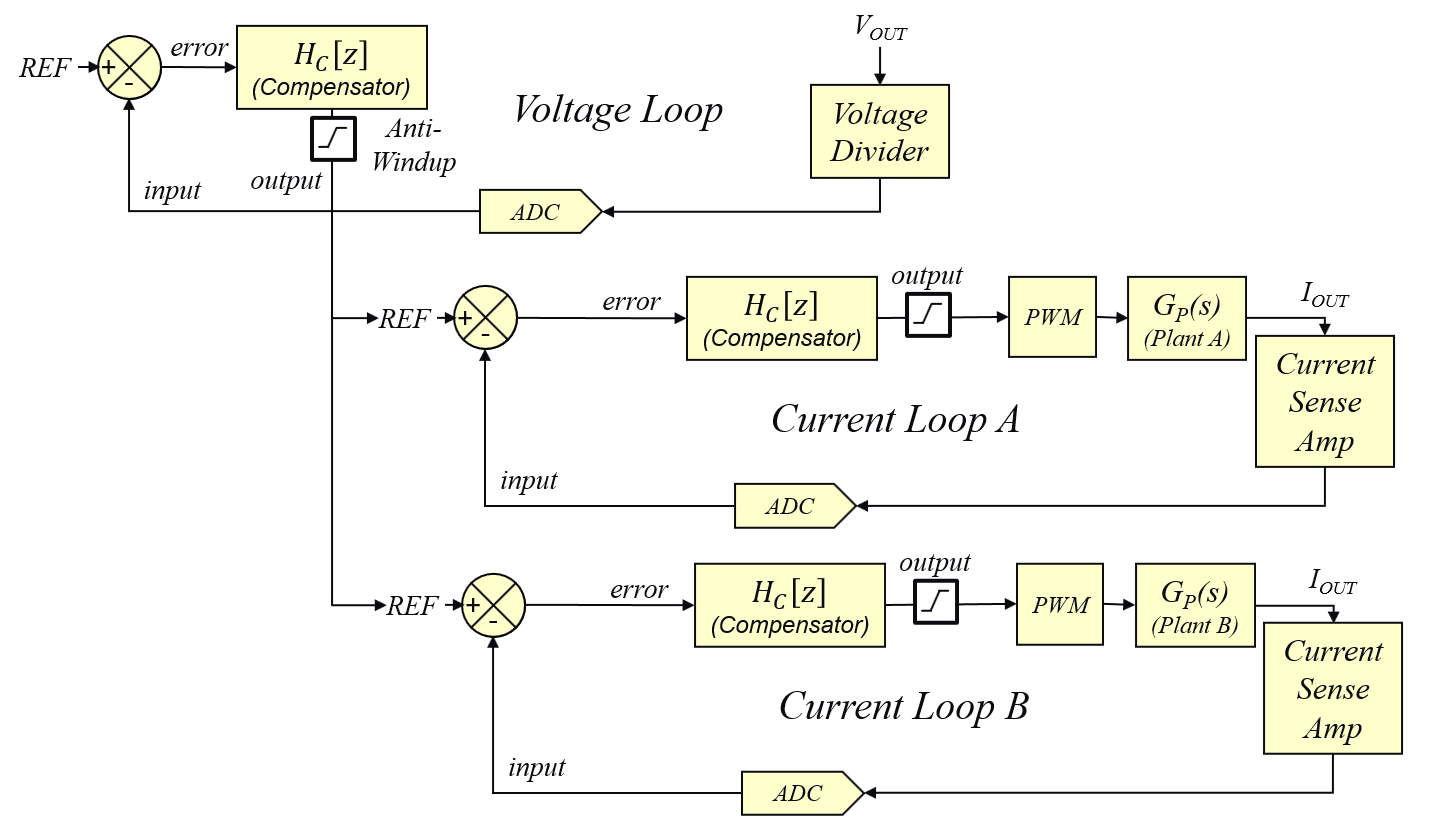

El sistema de control bidireccional de EPC9151 se basa en el control de modo de corriente promedio convencional (ACMC). Un bucle de voltaje exterior regula el voltaje de salida al comparar el valor de retroalimentación más reciente con una referencia interna. La desviación se procesa mediante un filtro de compensación discreto tipo II (2P2Z). La salida del bucle de voltaje establece la referencia para los dos bucles de corriente interna. Cada controlador de corriente de fase procesa la desviación entre la referencia de corriente dinámica dada y la retroalimentación de corriente más reciente individual. Cada salida de bucle de control de corriente ajusta el ciclo o fase de trabajo individual que resulta en corrientes de fase estrechamente equilibradas. Este esquema de control se aplica a ambos, de 48 V a 12 V dólar aguas abajo, así como al funcionamiento de impulso aguas arriba de 12 V a 48 V.

Cuando se alimenta desde una sola fuente de CC desde cualquier lado del convertidor, el voltaje de salida se mantendrá constante hasta la corriente de salida máxima de 25 por dólar respectivamente. 5.5 A Autor Operation, en la que el convertidor cambia al modo de corriente constante, desactiva efectivamente la regulación de voltaje.

Este firmware sirve como el bloque de construcción fundamental de los sistemas frontales del cargador de baterías mediante la implementación de un perfil de carga específico de la química o como convertidor de equilibrio entre dos rieles de autobuses alimentados por la batería.

Este bucle de control se puede encender/apagar utilizando el bit de habilitación en la palabra de estado de la estructura de datos del controlador CNPNZ_T. La modulación de ganancia de bucle adaptativa está activa permanentemente tan pronto como el bucle de control está habilitado.

El código fuente del bucle de control está configurado y generado por el software PowersMart ™ - Digital Control Library Designer (DCLD).

Este software de diseño adicional está disponible para descargar en las páginas de GitHub:

Una vez instalado, la configuración del controlador se puede modificar. La configuración más reciente se puede abrir desde el IDE MPLAB X® haciendo clic derecho en el archivo 'DPSK3_VMC.DCLD' ubicado en la carpeta de archivos importante del Administrador del proyecto. Cuando haga clic derecho, seleccione 'Abrir en el sistema' para abrir la configuración en PowersMart ™ DCLD.

Consulte la Guía del usuario de PowersMart ™ DCLD que se incluye en el software y se puede abrir desde el menú Ayuda de la aplicación.

No se ha agregado ninguna interfaz de control de usuario al firmware. Cualquier cambio en el firmware y la operación fundamental del diseño de referencia, incluida la reprogramación del voltaje de salida nominal se puede realizar editando los valores específicos de hardware en el archivo de encabezado Descripción de hardware 'EPC9151_R10_HWDESCR.H' ubicado en 'Project Manager => Archivos de encabezado/configuración' '

Las configuraciones del convertidor en este archivo se definen como valores físicos como Volt, Amperio, OHM, etc. Cada valor definido se convierte en números binarios por las llamadas macros, en el momento de la compilación. Por lo tanto, los usuarios no tienen que convertir valores manualmente.

Para programar el convertidor para proporcionar un voltaje de salida nominal diferente del conjunto de 12 V DC de forma predeterminada, siga estos pasos:

La configuración para el voltaje de salida nominal se encuentra en las líneas #324 a #326.

#define BUCK_VOUT_NOMINAL (float)12.000 // Nominal output voltage

#define BUCK_VOUT_TOLERANCE_MAX (float)0.500 // Output voltage tolerance [+/-]

#define BUCK_VOUT_TOLERANCE_MIN (float)0.100 // Output voltage tolerance [+/-]

La configuración de tolerancia anterior incluye la respuesta transitoria en un paso de carga máximo. El manejador de fallas observa el valor para la tolerancia de voltaje de salida máxima 'Buck_Vout_Tolerance_Max'. Si la lectura de voltaje de salida se desvía del valor de voltaje de referencia más reciente en más que el rango dado, el convertidor se apagará y se indicará un error de regulación. La fuente de alimentación se recuperará automáticamente tan pronto como se haya borrado la condición de falla y el período de retraso de recuperación especificado por Buck_Regerr_recovery_Delay en la línea #527 del EPC9151 Hardware Descripción El archivo de encabezado ha expirado.

(Los números de línea dado pueden estar sujetos a cambios)

Estos ejemplos de código incluyen un bucle de control proporcional alternativo que se usa comúnmente durante las mediciones de la respuesta de frecuencia de la planta de energía. Cuando la siguiente define se establece en verdadero, el bucle de control principal común se reemplaza por el controlador proporcional.

app_power_control.c, line 33: #define PLANT_MEASUREMENT false

Los controladores proporcionales son por defecto inestables y no son adecuados para regular la salida de una fuente de alimentación en condiciones de funcionamiento normales. Durante una medición de la planta, es obligatorio que el voltaje de entrada y la carga permanezcan estables y no cambien.

Para obtener más información sobre cómo realizar una medición de planta de energía, lea las secciones en la Guía del usuario de PowersMart ™ DCLD.

(c) 2020, Microchip Technology Inc.