Konverter Buck Converter Sinkron Kinerja Tinggi Rata -rata Kontrol Mode Saat Ini

Tampilan teratas

Contoh kode ini menunjukkan implementasi kontrol mode rata -rata saat ini untuk DSPIC33CK. Ini secara khusus telah dikembangkan untuk konverter Buck Synchronous Kinerja Tinggi EPC9153.

Papan memulai konverter buck secara otomatis ketika daya diterapkan ke papan, sehingga meningkatkan tegangan output dari 0 ke nilai nominalnya. Prosedur startup dikontrol dan dieksekusi oleh mesin status pengontrol daya dan mencakup prosedur startup yang dapat dikonfigurasi dengan penundaan daya, periode ramp up dan penundaan daya yang baik sebelum turun ke mode regulasi konstan. Rutin penangan kesalahan tambahan secara terus menerus memantau data ADC yang masuk dan bit status periferal dan mematikan catu daya jika tegangan input di luar kisaran maksimum yang ditentukan 41,5 V menjadi 59,5 V (UVLO/OVLO) atau jika tegangan output lebih dari +/- 0,5 V dari regulasi lebih dari 10.

Produk teknologi microchip yang ditampilkan:

Produk Konversi Daya Efisien (EPC) Feature:

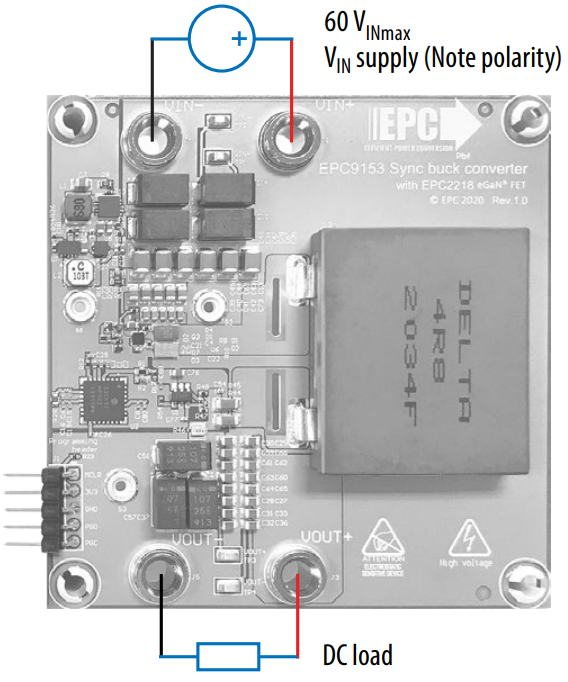

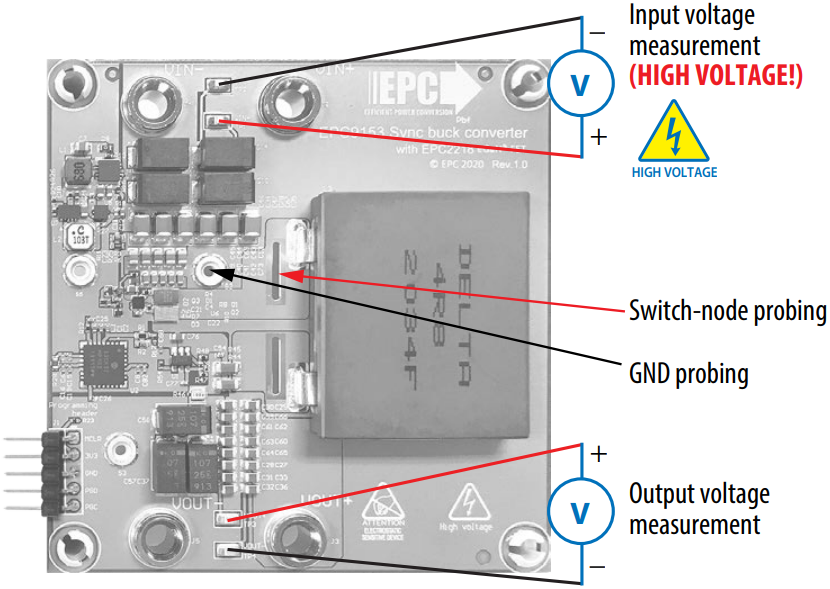

Modul konverter Buck Synchronous Kinerja Tinggi EPC9153 menyediakan semua antarmuka yang diperlukan untuk memprogram dan men -debug DSPIC33CK32MP102 DSC serta titik uji dan konektor pisang jack untuk penanganan kit yang mudah dan aman selama tes bangku. EPC9153 QSG menyediakan instruksi prosedur operasi terperinci.

Papan datang diprogram dan siap digunakan saat dibongkar. Tidak ada pemrograman ulang perangkat target yang diperlukan untuk mengoperasikan papan kecuali fitur atau pengaturan seperti tegangan output nominal atau waktu start-up perlu dimodifikasi.

Dalam kasus fitur berbasis firmware perlu diubah, pengontrol microchip DSPIC33CK dapat diprogram ulang menggunakan port pemrograman serial in-sirkuit (ICSP) yang tersedia pada antarmuka pemrograman RJ-11 serta header 5-pin. Antarmuka ini mendukung semua programmer/debugger microchip, seperti MPLAB® ICD4, MPLAB® Real Ice atau MPLAB® Pickit4 dan turunan sebelumnya. Lihat EPC9153 Panduan Mulai Cepat untuk detailnya.

Konverter mulai secara otomatis ketika lebih dari 41,5 V DC diterapkan di terminal input EPC9153. Silakan baca panduan start cepat EPC9153 untuk mendapatkan informasi terperinci tentang persyaratan untuk pengaturan dan pengoperasian desain referensi ini.

Mesin negara melewati langkah -langkah berikut dalam urutan kronologis:

a) Inisialisasi

Pada langkah ini parameter loop kontrol diatur ulang ke defaultnya, output PWM dimatikan tetapi PWM masih berjalan, terus memicu ADC untuk menjaga input pengambilan sampel dan tegangan output serta suhu papan.

b) Reset Ini adalah keadaan 'jatuh' dari mana konverter buck akan dimulai kembali setelah dimulai dengan sukses dan telah ditutup karena kondisi kesalahan (misalnya input di bawah/lebih dari tegangan atau kondisi suhu yang berlebihan)

c) Siaga setelah reset, mesin negara menunggu semua bendera kesalahan dibersihkan dan bit aktif dan go untuk diatur.

d) Power-On Delay (POD) Setelah konverter Buck telah dibersihkan, mesin negara akan menjalankan prosedur startup yang dimulai dengan daya penundaan. Ini hanyalah penundaan sederhana di mana konverter akan tetap tidak aktif tetapi penangan kesalahan akan mengamati nilai -nilai yang dihasilkan oleh ADC untuk kondisi kesalahan yang terjadi.

e) Luncurkan ramp tegangan setelah penundaan power-on telah kedaluwarsa, input dan tegangan output akan diukur. Dalam hal output konverter sudah pra-bias (tegangan = non-nol), pengontrol daya akan 'diisi sebelumnya' dengan riwayat kontrol buatan dan output PWM untuk dengan lembut meningkatkan tegangan output dari level terbaru.

f) Tegangan ramp-up Sekarang loop umpan balik digital dan PWM diaktifkan dan nilai referensi sistem loop tertutup bertambah dengan setiap eksekusi mesin negara (interval 100 μsec). Loop kontrol telah disesuaikan untuk beroperasi dengan frekuensi cross-over> 10 kHz yang cocok dengan frekuensi gangguan maksimum yang diizinkan untuk menjaga sistem kontrol stabil.

g) Daya penundaan yang baik setelah tegangan referensi telah ditingkatkan ke tingkat nominal yang telah ditentukan, mesin negara beralih ke periode penundaan daya yang baik. Ini adalah penundaan sederhana yang sederhana di mana loop kontrol dalam kondisi tunak menunggu periode penundaan berakhir.

h) Online Setelah penundaan daya daya telah berakhir, konverter turun ke operasi nominal. Dalam kondisi ini terus -menerus mengamati nilai referensi untuk perubahan. Jika bagian lain dari firmware mengubah referensi pengontrol, mesin negara akan dengan lembut menyetel ke tingkat yang baru alih-alih menggerakkan referensi.

i) Suspend/Error If the power controller is shut down and reset by external commands (eg fault handler detecting a fault condition or through user-interaction), the state machine is switching into the SUSPEND state, which disables the PWM outputs and control loop execution, clears the control histories and resets the state machine back to RESET

Firmware ini menggunakan dua pengontrol tipe II digital untuk menutup loop umpan balik dalam kontrol mode rata -rata saat ini. Pengontrol terdiri dari dua loop bertingkat. Loop umpan balik tegangan luar menentukan kesalahan tegangan output dan menghitung referensi yang diperlukan untuk loop umpan balik arus rata -rata dalam. Loop arus rata -rata dalam menentukan penyimpangan terbaru antara referensi baru dan sinyal umpan balik terbaru dan menyesuaikan siklus tugas PWM untuk memenuhi permintaan daya dan memperbaiki kesalahan tegangan output. Output numerik dari setiap loop diperiksa terhadap ambang batas minima dan maxima yang ditentukan dan, bila perlu, dijepit ke ambang batas yang ditentukan pengguna ini untuk melindungi perangkat keras dan mencegah saturasi loop.

Loop kontrol ini dapat dihidupkan/dimatikan dengan menggunakan bit aktif dalam kata status struktur data pengontrol CNPNZ_T. Modulasi gain loop adaptif aktif secara permanen segera setelah loop kontrol diaktifkan.

Kode sumber loop kontrol dikonfigurasi dan dihasilkan oleh perangkat lunak PowerSmart ™ - Digital Control Library Designer (DCLD).

Perangkat lunak desain tambahan ini tersedia untuk diunduh di halaman github:

Setelah diinstal, konfigurasi pengontrol dapat dimodifikasi. Konfigurasi terbaru dapat dibuka dari dalam IDE MPLAB X® dengan mengklik kanan pada masing-masing file konfigurasi loop kontrol 'xxx_loop.dcld' yang terletak di folder file penting dari manajer proyek. Setiap loop kontrol dikonfigurasi dalam file konfigurasi individualnya bernama 'v_loop.dcld' untuk loop tegangan dan 'i_loop.dcld' untuk loop saat ini. Saat diklik kanan, pilih 'Open in System' untuk membuka konfigurasi di PowerSmart ™ DCLD.

Silakan merujuk ke Panduan Pengguna PowerSmart ™ DCLD yang termasuk dalam perangkat lunak dan dapat dibuka dari menu bantuan aplikasi.

Tidak ada antarmuka kontrol pengguna yang ditambahkan ke firmware. Setiap perubahan pada firmware dan operasi mendasar dari desain referensi, termasuk pemrograman ulang tegangan output nominal dapat dilakukan dengan mengedit nilai-nilai khusus perangkat keras dalam file header deskripsi perangkat keras 'EPC9153_R10_HWDESCR.H' Terletak di 'Project Manager => file header/konfigurasi'

Pengaturan konverter dalam file ini didefinisikan sebagai nilai fisik seperti Volt, Ampere, OHM, dll. Setiap nilai yang ditentukan dikonversi menjadi angka biner oleh apa yang disebut makro, pada waktu kompilasi. Dengan demikian, pengguna tidak harus mengonversi nilai secara manual.

Untuk memprogram konverter untuk memberikan tegangan output nominal yang berbeda dari set 12 V DC secara default, ikuti langkah -langkah ini:

Pengaturan untuk tegangan output nominal diatur menggunakan definisi ini

#define BUCK_VOUT_NOMINAL (float)20.000 // Nominal output voltage

#define BUCK_VOUT_TOLERANCE_MAX (float)0.500 // Output voltage tolerance [+/-]

#define BUCK_VOUT_TOLERANCE_MIN (float)0.100 // Output voltage tolerance [+/-]

Pengaturan toleransi di atas termasuk respons sementara pada langkah beban maksimum. Nilai untuk toleransi tegangan output maksimum 'buck_vout_tolerance_max' diamati oleh penangan kesalahan. Jika pembacaan tegangan output dialihkan dari nilai tegangan referensi terbaru dengan lebih dari kisaran yang diberikan, konverter akan ditutup dan kesalahan regulasi akan ditunjukkan. Catu daya akan secara otomatis pulih segera setelah kondisi kesalahan telah dihapus dan periode penundaan pemulihan yang ditentukan oleh buck_regerr_recovery_delay, dinyatakan dalam file header deskripsi perangkat keras EPC9148, telah kedaluwarsa. Sensitivitas perjalanan kesalahan dapat disesuaikan dengan mengubah deklarasi buck_regerr_trip_delay.

(Nomor baris yang diberikan mungkin dapat berubah)

Contoh kode ini mencakup alternatif, loop kontrol proporsional yang biasanya digunakan selama pengukuran respons frekuensi pembangkit listrik. Ketika define berikut diatur ke True, loop kontrol utama umum digantikan oleh pengontrol proporsional.

app_power_control.c, line 33: #define PLANT_MEASUREMENT false

Pengontrol proporsional secara default tidak stabil dan tidak cocok untuk mengatur output catu daya dalam kondisi operasi normal. Selama pengukuran pabrik adalah wajib bahwa tegangan input dan beban tetap stabil dan tidak berubah.

Untuk informasi lebih lanjut tentang cara melakukan pengukuran pembangkit listrik, silakan merujuk ke Bagian 6.1 dari Panduan Pengguna DCLD PowerSmart ™.

(c) 2020, Microchip Technology Inc.